#### Instituto Tecnológico de Costa Rica

#### Escuela de Ingeniería Electrónica

Implementación de un algoritmo de reconocimiento de patrones en señales biomédicas para su evaluación en un microprocesador basado en la Arquitectura de Set de Instrucciones RISC V

> Informe de Proyecto de Graduación para optar por el título de Ingeniero en Electrónica con el grado académico de Licenciatura

> > Gabriel José Madrigal Boza

# INSTITUTO TECNOLÓGICO DE COSTA RICA ESCUELA DE INGENIERÍA ELECTRÓNICA PROYECTO DE GRADUACIÓN ACTA DE APROBACIÓN

Defensa de Proyecto de Graduación Requisito para optar por el título de Ingeniero en Electrónica Grado Académico de Licenciatura Instituto Tecnológico de Costa Rica

El Tribunal Evaluador aprueba la defensa del proyecto de graduación denominado Implementación de un algoritmo de reconocimiento de patrones en señales biomédicas para su evaluación en un microprocesador basado en la Arquitectura de Set de Instrucciones RISC V, realizado por el señor Gabriel José Madrigal Boza y, hace constar que cumple con las normas establecidas por la Escuela de Ingeniería Electrónica del Instituto Tecnológico de Costa Rica.

Miembros del Tribunal Evaluador

M.Sc. Ronny García Ramírez

Profesor lector

Ing, Carlos Mauricio Segura Quirós

Profesor lector

M.Sc. Roberto Molina Robles

Profesor asesor

Cartago, 30 de noviembre, 2017

Declaro que el presente Proyecto de Graduación ha sido realizado enteramente por mi persona, utilizando y aplicando literatura referente al tema e introduciendo conocimientos propios.

En los casos en que he utilizado bibliografía he procedido a indicar las fuentes mediante las respectivas citas bibliográficas. En consecuencia, asumo la responsabilidad total por el trabajo de graduación realizado y por el contenido del correspondiente informe final.

Gabriel José Madrigal Boza

Cartago, 28 de noviembre de 2017

Céd: 1-1580-0261

#### Resumen

En este documento se expone el desarrollo de un sistema de reconocimiento de eventos o patrones en señales de electrocardiogramas (ECG). La detección de eventos se realiza mediante la ejecución de un algoritmo de correlación, utilizando señales biomédicas reales representadas en un formato bitstream. El desarrollo del proyecto se divide en dos secciones, una de las cuáles está dedicada al desarrollo del algoritmo y su implementación en C++. Por otro lado, se tiene el desarrollo de la plataforma de hardware en la cual se ejecuta el algoritmo. En el caso del presente proyecto, se utiliza la plataforma RocketChip, de uso libre, que se basa en la arquitectura de set de instrucciones RISC V.

Palabras clave: Correlación cruzada, Dispositivos médicos implantables, RISCV, RocketChip

#### Abstract

In this document, the development of an event/pattern recognition system in ECG signals is presented. The event detection is performed via a cross-correlation algorithm, using real biomedical signals represented in a bitstream format. The development of the project is divided in two main sections, one of which considers the design of the algorithm and its implementation in C++. The other main section discusses the development of a hardware platform in which the algorithm is executed. In the case of the presented project, the hardware platform used is based on RocketChip, an open-source initiative based on the instruction set architecture RISC V.

Keywords: Cross-correlation, Implantable medical devices, RISCV, RocketChip

#### Agradecimientos

A mis padres, Víctor y Virginia, por ser el mejor ejemplo siempre. Han sido el apoyo fundamental durante toda mi vida, gracias al que he logrado cumplir esta meta. A mis hermanas, Aurora y Ana Victoria, por ayudarme en este camino y ser siempre la mejor compañía.

A todos mis amigos y amigas que me han acompañado en este camino. A todos los que conocí durante mi paso en el TEC, los compañeros de Electrónica y del DCILab. A todos los allegados al *Aparta 40*, les debo las mejores experiencias de estos 5 años.

Por último, a los profesores Renato Rímolo Donadio, Alfonso Chacón Rodríguez y Ronny García Ramírez, por darme la oportunidad de trabajar con ustedes y aprender tanto; y al profesor Roberto Molina Robles por su ayuda con este proyecto.

Gabriel José Madrigal Boza Cartago, 4 de diciembre de 2017

# Índice general

| Indice de figuras |      |         |                                                                |     |

|-------------------|------|---------|----------------------------------------------------------------|-----|

| Ín                | dice | de tab  | olas                                                           | vi  |

| Ín                | dice | de cód  | ligos fuente                                                   | vii |

| 1                 | Intr | oducci  | ión                                                            | 1   |

|                   | 1.1  | Proble  | ema                                                            | . 3 |

|                   | 1.2  | Objeti  | ivos                                                           | . 3 |

|                   |      | 1.2.1   | Objetivo General                                               | . 3 |

|                   |      | 1.2.2   | Objetivos Específicos                                          | . 4 |

| <b>2</b>          | Ma   | rco Teo | órico                                                          | 5   |

|                   | 2.1  | Rocket  | tChip SoC                                                      | . 5 |

|                   |      | 2.1.1   | Protocolo TileLink                                             | . 8 |

|                   |      | 2.1.2   | Microarquitectura básica del núcleo de procesamiento (Rocket)  | 9   |

|                   |      | 2.1.3   | Memorias Caché de 1er Nivel                                    | 10  |

|                   |      | 2.1.4   | Soporte de Depuración Externa para RISC-V                      | 11  |

|                   |      | 2.1.5   | Diagramas de referencia                                        |     |

|                   | 2.2  | Correl  | ación Cruzada de Señales                                       | 14  |

|                   | 2.3  | -       | sentación de señales en formato bitstream                      |     |

|                   | 2.4  | Señale  | es de Electrocardiogramas: ECG                                 | 16  |

|                   |      | 2.4.1   | Mecanismos de conducción eléctrica en el corazón               | 16  |

|                   |      | 2.4.2   | Elementos importantes presentes en un electrocardiograma       | 18  |

| 3                 | Imp  |         | tación de un SoC basado en RocketChip                          | 20  |

|                   | 3.1  |         | na en Chip Generado                                            |     |

|                   | 3.2  | Simula  | aciones y ejecución de programas de prueba                     | 24  |

| 4                 | Cor  | relació | on cruzada con señales bitstream                               | 25  |

|                   | 4.1  | Obten   | ción de las señales ECG                                        | 25  |

|                   | 4.2  |         | o del modulador $\Sigma\Delta$                                 |     |

|                   | 4.3  | Repres  | sentación bitstream de las señales                             | 28  |

|                   | 4.4  | _       | tmo de Correlación Cruzada implementado en C++ $\dots \dots$ . |     |

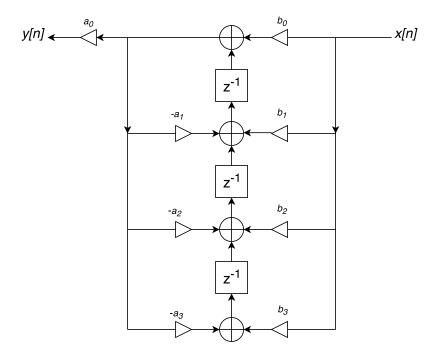

|                   | 4.5  | Diseño  | o de un filtro paso bajo digital de 3er orden                  | 31  |

Índice general ii

|              | 4.6   | Filtro de Media Móvil                                                       | 32 |

|--------------|-------|-----------------------------------------------------------------------------|----|

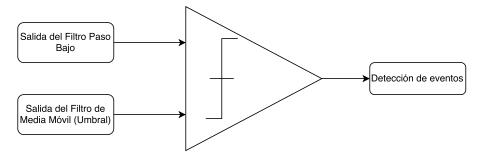

|              | 4.7   | Comparador y Detector implementados                                         | 34 |

| 5            | Res   | ultados y Análisis                                                          | 35 |

|              | 5.1   | Sistema en Chip generado                                                    | 35 |

|              | 5.2   | Resultados de la simulación con programas de prueba                         | 36 |

|              | 5.3   | Obtención del patrón de comparación para señales ECG                        | 42 |

|              | 5.4   | Representación bitstream de las señales utilizadas en las pruebas           | 43 |

|              | 5.5   | Respuesta en frecuencia del filtro paso bajo diseñado                       | 45 |

|              | 5.6   | Correlación cruzada entre señales de prueba y distintos patrones            | 46 |

|              | 5.7   | Detección de eventos en señales ECG                                         | 49 |

| 6            | Con   | iclusiones y Recomendaciones                                                | 52 |

|              | 6.1   | Conclusiones                                                                | 52 |

|              | 6.2   | Recomendaciones                                                             | 53 |

| Bi           | bliog | grafía                                                                      | 54 |

| $\mathbf{A}$ | Res   | ultados Adicionales                                                         | 57 |

|              | A.1   | Resultado de la correlación utilizando diferentes señales de prueba         | 57 |

|              | A.2   | Resultados de la detección de eventos ante señales senoidales de diferentes |    |

|              |       | frecuencias                                                                 | 61 |

| Ín           | dice  | alfabético                                                                  | 63 |

# Índice de figuras

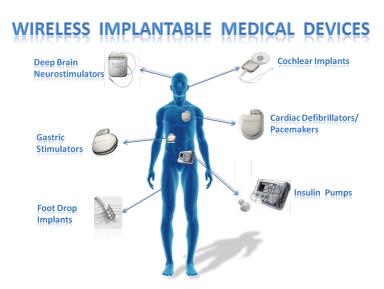

| 1.1 | Representación de diferentes sistemas médicos implantables. Imagen tomada de [1]                                                                                                                                                                                                                                                                                                | 1        |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1 | Ejemplo de un SoC diseñado utilizando RocketChip Generator. Se observan 2 recuadros, cada uno de los cuales contiene una unidad de procesamiento. En un caso es un núcleo Rocket, en el otro una unidad de ejecución fuera de orden (BOOM). Cada uno de los recuadros cuenta con sus memorias caché de 1er nivel, tanto para datos como instrucciones, y ambos núcleos incluyen |          |

| 0.0 | FPU y coprocesadores. Figura tomada de [5]                                                                                                                                                                                                                                                                                                                                      | 6        |

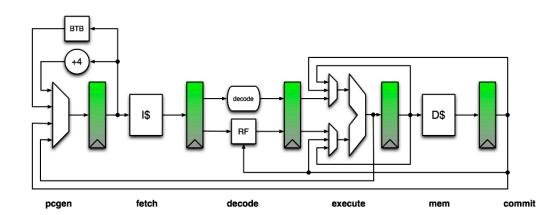

| 2.2 | Microarquitectura del núcleo Rocket, con las etapas (simplificadas) del pipeline. En la etapa de decodificación, el bloque denominado RF corresponde al banco de registros ( <i>Register File</i> ). El componente BTB corresponde a una unidad de almacenamiento de destino de saltos ( <i>Branch Target Buffer</i> ), que asiste en                                           |          |

| 9.9 | la predicción de saltos. Figura tomada de [15]                                                                                                                                                                                                                                                                                                                                  | 9        |

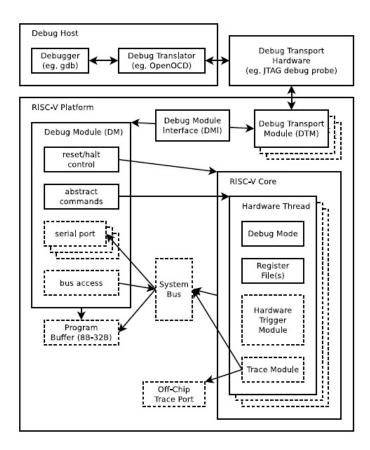

| 2.3 | Arquitectura del sistema de depuración externa. Se observa como la interfaz DMI sirve de puente entre el módulo de depuración DM y el DTM. Figura                                                                                                                                                                                                                               |          |

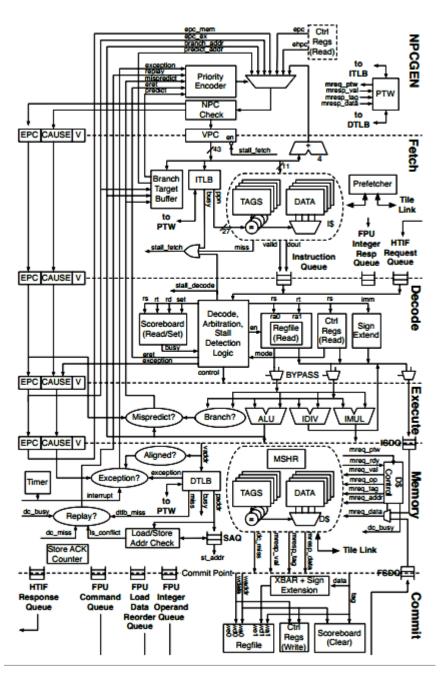

| 2.4 | tomada de [21]                                                                                                                                                                                                                                                                                                                                                                  | 11<br>12 |

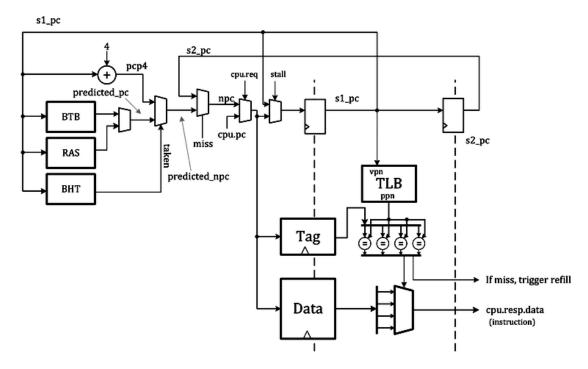

| 2.5 | Generador de PC y etapa Fetch. Figura tomada de [3]                                                                                                                                                                                                                                                                                                                             | 13       |

| 2.6 | Etapas del pipeline. En la implementación básica no se incluye la unidad de                                                                                                                                                                                                                                                                                                     |          |

|     | punto flotante. Figura tomada de [3]                                                                                                                                                                                                                                                                                                                                            | 13       |

| 2.7 | Memoria caché de datos. Figura tomada de [3]                                                                                                                                                                                                                                                                                                                                    | 14       |

| 2.8 | Ilustración del corazón, en la que se señalan los elementos principales involucrados en los procesos de conducción eléctrica. Las cavidades derechas (aurícula y ventrículo) se ubican a la <i>izquierda</i> de la ilustración, según el punto                                                                                                                                  |          |

|     | de vista del lector. Figura tomada de [14]                                                                                                                                                                                                                                                                                                                                      | 17       |

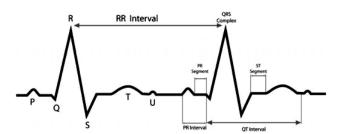

| 2.9 | Ejemplo típico de un electrocardiograma, se observan las principales ondas e intervalos que se presentan en un ECG. Se pueden observar los intervalos RR, PR y QT, además del complejo QRS y las ondas T y P. Figura tomada de [14].                                                                                                                                            | 18       |

|     |                                                                                                                                                                                                                                                                                                                                                                                 |          |

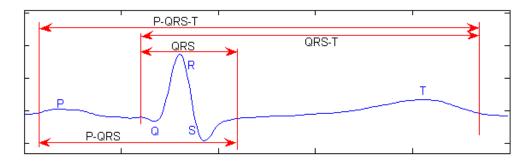

| 4.1 | Ciclo cardíaco completo, con sus diferentes fragmentos informativos, obtenido de la derivación I. Figura tomada de [18]                                                                                                                                                                                                                                                         | 26       |

Índice de figuras iv

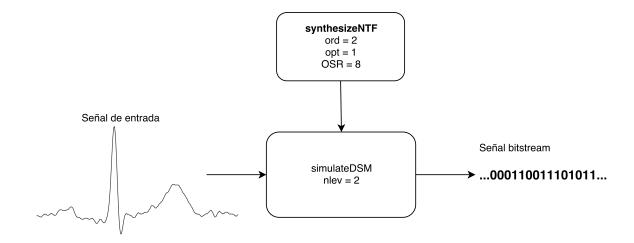

| 4.2  | Modulación $\Sigma\Delta$ utilizando el paquete de herramientas python sigma-delta. Los bloques representan cada una de las funciones utilizadas. Se muestran las señales de entrada y salida, además de los valores usados para cada uno de                                                                                                                                                                                                                                             |          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | los parámetros de entrada de las funciones                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27       |

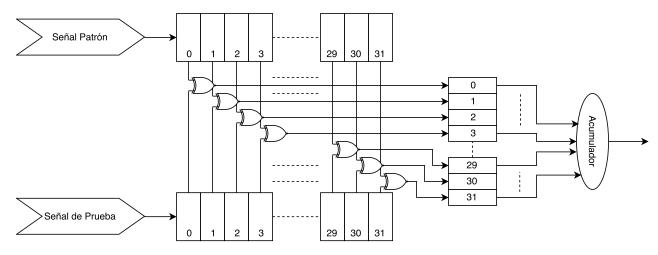

| 4.3  | Correlación cruzada, ejecutada bit por bit en una de las posiciones del arreglo                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 4.4  | de tipo <b>uint32_t</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32       |

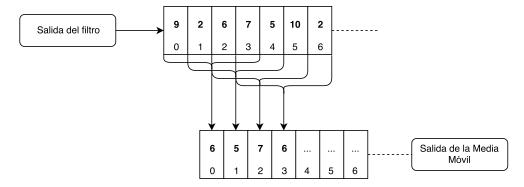

| 4.5  | Diagrama conceptual del cálculo de la media móvil. En este ejemplo se utilizan 4 valores de salida del filtro paso bajo, pero este valor se puede parametrizar                                                                                                                                                                                                                                                                                                                           | J2       |

| 4.6  | como N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33       |

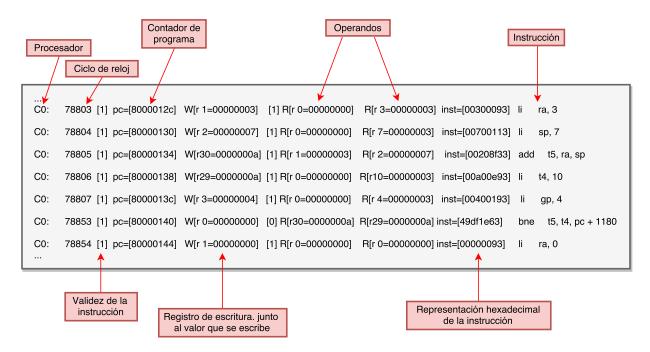

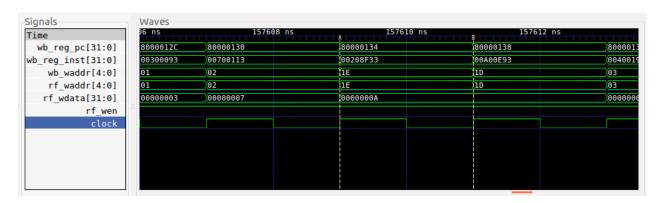

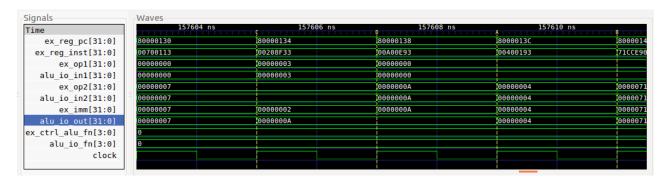

| 5.1  | Información relevante de la etapa Write Back durante la ejecución de un programa de prueba. Se observa la ejecución de una de las sumas del programa,                                                                                                                                                                                                                                                                                                                                    |          |

| 5.2  | para probar la instrucción add                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39       |

| 5.3  | instrucción ejecutada en ese ciclo y los operandos de la misma                                                                                                                                                                                                                                                                                                                                                                                                                           | 39       |

| 5.4  | (ALU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40       |

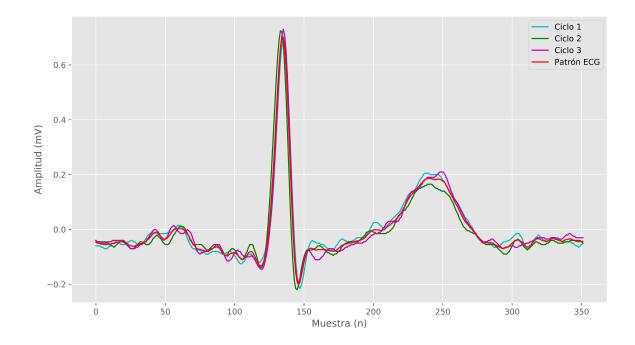

|      | de las cuales 3 corresponden a las señales extraídas de la base de datos                                                                                                                                                                                                                                                                                                                                                                                                                 | 43       |

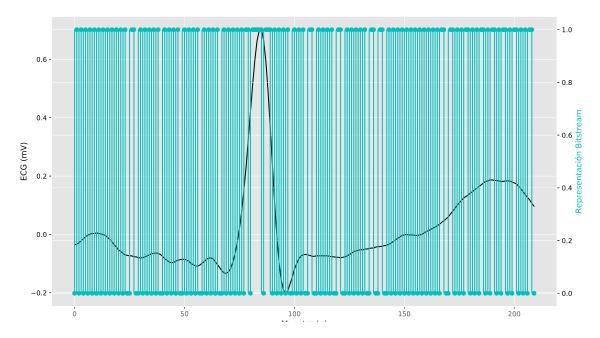

| 5.5  | Representación bitstream de la señal ECG utilizada como patrón. Para mejorar la visualización de las señales, se muestra sólo una porción de las mismas.                                                                                                                                                                                                                                                                                                                                 | 44       |

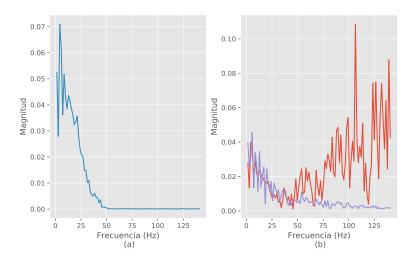

| 5.6  | Espectro de la señal de un electrocardiograma. En (a) se observa el espectro de la señal sin realizarle ningún preprocesamiento. En (b) se muestra el espectro de la señal modulada ( $\Sigma\Delta$ ) en rojo, junto al espectro de la misma señal luego de aplicar el filtro paso bajo diseñado. Además, se puede observar, en rojo, como el efecto de la modulación hace que el ruido de cuantización se mueva a frecuencias altas, y como este ruido se elimina al aplicar el filtro | 44       |

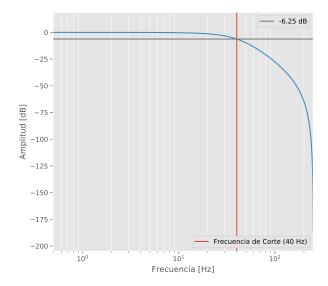

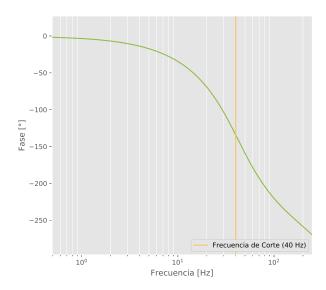

| 5.7  | Respuesta en frecuencia del filtro paso bajo diseñado. Se observa la frecuencia                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|      | de corte para la que el filtro fue diseñado, y el valor de la atenuación en dicha                                                                                                                                                                                                                                                                                                                                                                                                        | 4 =      |

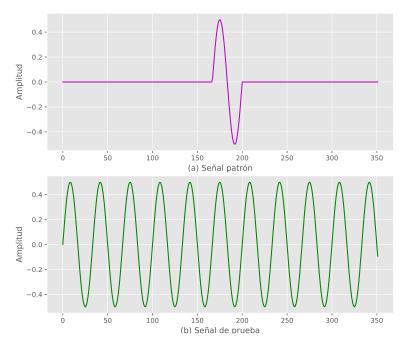

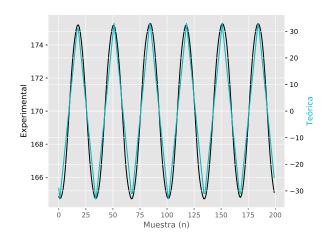

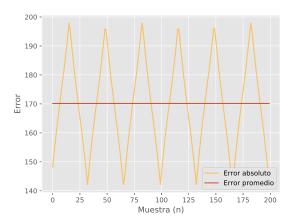

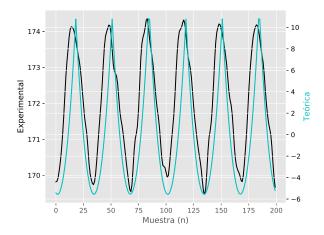

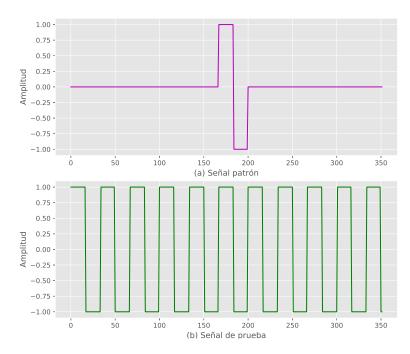

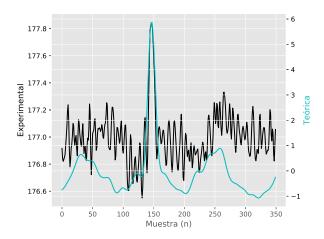

| 5.8  | frecuencia                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45<br>46 |

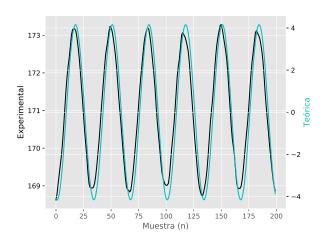

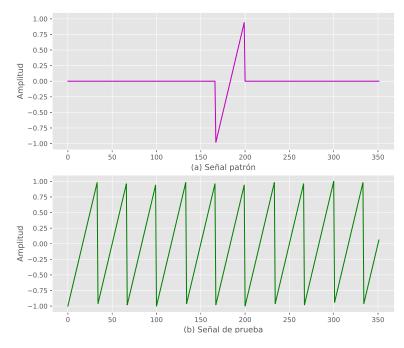

| 5.9  | Patrón y señal de prueba utilizados para la correlación de una señal senoidal.                                                                                                                                                                                                                                                                                                                                                                                                           | 47       |

| 5.10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47       |

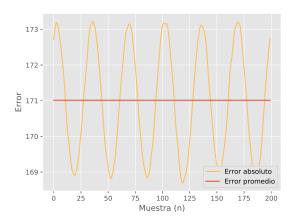

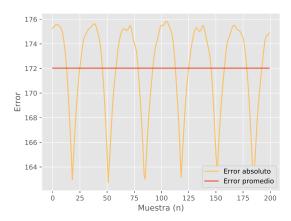

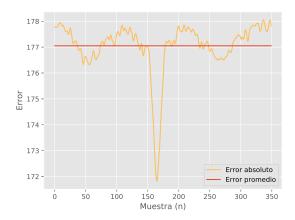

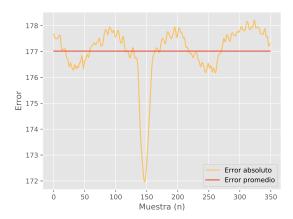

|      | Error en la correlación de una señal senoidal                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48       |

Índice de figuras

| 5.12 | Resultados de la correlación de una señal ECG contra su respectivo patrón,          | 10       |

|------|-------------------------------------------------------------------------------------|----------|

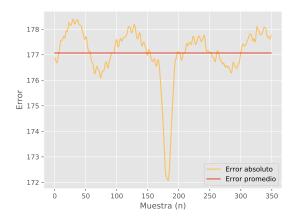

| 5 13 | caso 1                                                                              | 48<br>49 |

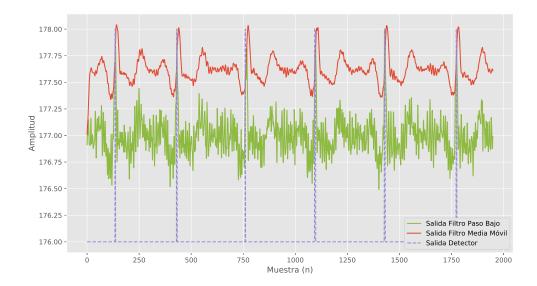

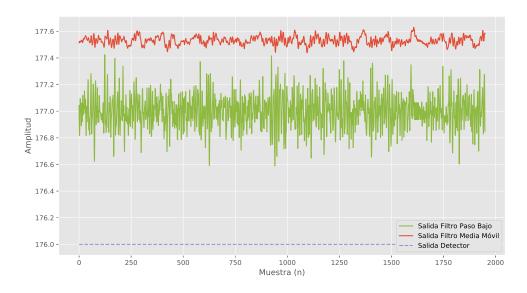

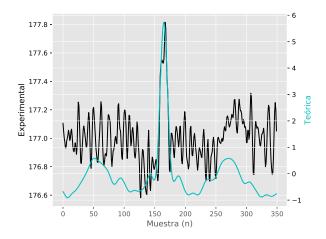

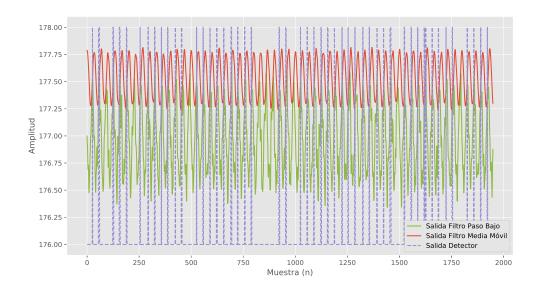

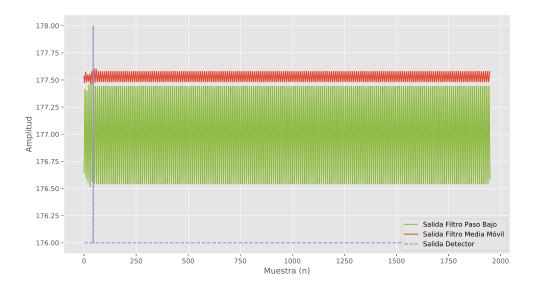

|      | Salida de los filtros paso bajo y de media móvil, junto a la salida del detector,   | 10       |

|      | al utilizar señales ECG como entrada al algoritmo.                                  | 50       |

| 5.15 | Salida de los filtros paso bajo y de media móvil, junto a la salida del detector,   |          |

|      | al utilizar una señal de ruido para probar la eficacia del sistema                  | 50       |

| A.1  | Correlación de una señal cuadrada                                                   | 57       |

| A.2  | Error en la correlación de una señal cuadrada                                       | 58       |

| A.3  | Correlación de una señal diente de sierra                                           | 58       |

| A.4  | Error en la correlación de una señal diente de sierra                               | 58       |

| A.5  | Patrón y señal de prueba utilizados para la correlación de una señal cuadrada.      | 59       |

| A.6  | Patrón y señal de prueba utilizados para la correlación de una señal diente de      |          |

|      | sierra                                                                              | 59       |

| A.7  | Resultados de la correlación de una señal ECG contra su respectivo patrón,          |          |

|      | caso 2                                                                              | 60       |

| A.8  | Error en la correlación de una señal ECG contra su respectivo patrón, caso 2.       | 60       |

| A.9  | Resultados de la correlación de una señal ECG contra su respectivo patrón,          |          |

|      | caso 3                                                                              | 60       |

| A.10 | Error en la correlación de una señal ECG contra su respectivo patrón, caso 3.       | 61       |

| A.11 | Salida de los filtros paso bajo y de media móvil, junto a la salida del detector,   |          |

|      | al utilizar una señal senoidal con frecuencia $f=15$ Hz                             | 62       |

| A.12 | 2 Salida de los filtros paso bajo y de media móvil, junto a la salida del detector, |          |

|      | al utilizar una señal senoidal con frecuencia $f = 200 \text{ Hz.}$                 | 62       |

### Índice de tablas

| 2.1 | Tabla de verdad de la función lógica XNOR                                                                                              | 15 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Comparación entre dos categorías de arquitecturas de computadores                                                                      | 21 |

| 4.1 | Representación binaria de los operandos utilizados en la expresión $A$ del algoritmo popount SWAR, donde $j = ((i >> 1) \& 0x5555555)$ | 30 |

| 4.2 | Transformada utilizada en el algoritmo popcount SWAR para cada par de bits.                                                            |    |

| 5.1 | Mapeo de memoria resultante para el Sistema en Chip diseñado                                                                           | 36 |

| 5.2 | Resultados de la ejecución de programas de prueba en el sistema diseñado.                                                              |    |

|     | Los resultados que se muestran son para el conjunto de instrucciones I de                                                              |    |

|     | RISC V. Todas las pruebas terminan con resultados positivos                                                                            | 41 |

| 5.3 | Resultados de la ejecución de programas de prueba en el sistema diseñado.                                                              |    |

|     | Los resultados que se muestran son para la extensión M de RISC V. Para                                                                 |    |

|     | estas pruebas los resultados obtenidos son positivos                                                                                   | 41 |

| 5.4 | Resultados de la ejecución de programas de prueba en el sistema diseñado.                                                              |    |

|     | Los resultados que se muestran son para las extensiones A, C y F de RISC                                                               |    |

|     | V. Dado que se eliminó el soporte para estas extensiones en el diseño del                                                              |    |

|     | procesador, para estas pruebas los resultados obtenidos son negativos                                                                  | 42 |

# Índice de códigos fuente

| 2.1 | Ejemplo de una configuración básica de un microprocesador Rocket. Se observa como se cambian los parámetros del recuadro que contiene el procesador        |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | para modificar las memorias caché y la unidad de multiplicación y división                                                                                 |    |

|     | del mismo. Con esta clase se pueden instanciar $N$ procesadores con las carac-                                                                             |    |

|     | terísticas especificadas dentro del mismo recuadro                                                                                                         | 7  |

| 2.2 | Configuración para modificar la arquitectura del procesador (para que sea de 32 bits). Al aplicar esta configuración también deben modificarse los         |    |

|     | parámetros mostrados de las unidades de Punto Flotante y Multiplicación                                                                                    | _  |

|     | y División                                                                                                                                                 | 1  |

| 2.3 | Configuración utilizada para eliminar la Unidad de Punto Flotante. Al retirar esta unidad se elimina también el soporte para la extensión de instrucciones |    |

|     | F de RISC V                                                                                                                                                | 8  |

| 2.4 | Configuración utilizada para instanciar un módulo de depuración JTAG al                                                                                    |    |

|     | sistema                                                                                                                                                    | 8  |

| 2.5 | Configuración para cambiar el archivo de inicialización almacenado en la me-                                                                               |    |

|     | moria boot ROM                                                                                                                                             | 8  |

| 3.1 | Configuración del sistema en chip diseñado. Se observan las clases utilizadas                                                                              |    |

|     | para disminuir el conjunto de instrucciones que se implementa. También se                                                                                  |    |

|     | observa como se modifican los parámetros de las memorias caché de 1er nivel                                                                                |    |

|     | para disminuir su tamaño                                                                                                                                   | 22 |

| 3.2 | Configuración base del sistema en chip. Esta configuración es el punto de                                                                                  |    |

|     | partida para el diseño del sistema deseado                                                                                                                 | 23 |

| 4.1 | Función escrita en C++ para obtener el número de bits en alto de una variable                                                                              |    |

|     | de tipo entero sin signo de 32 bits. Implementa el algoritmo SWAR más                                                                                      |    |

|     | conocido como popcount                                                                                                                                     | 29 |

| 4.2 | Función escrita en C++ para obtener la media móvil. El parámetro de entrada                                                                                |    |

|     | es una arreglo de 18 posiciones (para este ejemplo) de tipo flotante. En este                                                                              |    |

|     | se almacenan los últimos 18 valores de salida del Filtro Paso Bajo                                                                                         | 33 |

| 4.3 | Sección de la rutina principal (escrita en C++) donde se actualiza el arreglo                                                                              |    |

|     | que contiene los N (18) últimos valores de salida del Filtro Paso Bajo. Con                                                                                |    |

|     | estos se calcula el valor actual de la Media Móvil                                                                                                         | 33 |

| 5.1 | Porción del programa de prueba rv32ui-p-add                                                                                                                | 37 |

| 5.2 | Definición de los macros utilizados en el programa de prueba $\emph{rv32ui-p-add}$                                                                         | 37 |

| 5.3 | Información del programa posterior a su compilación. Se muestran tanto las                                                                                 |    |

|     | instrucciones resultantes como las direcciones de memoria donde se almacenan.                                                                              | 38 |

#### Capítulo 1

#### Introducción

Desde la aparición del primer marcapasos completamente implantable, los implantes biomédicos han ganado terreno en la industria de la medicina, tanto en lo que respecta a la aceptación del público, como en los avances en miniaturización y diversificación de aplicaciones. Es posible observar como diferentes ramas de la medicina, como la cardiología y la neurología, se han visto beneficiadas por dichos dispositivos. Usualmente, las tareas realizadas por dichos implantes corresponden a la medición de variables físicas y químicas dentro del cuerpo humano, junto, en algunos casos, a la estimulación de órganos con fines terapéuticos. Estas variables medidas se relacionan directamente con los procesos realizados por los diferentes sistemas que componen el organismo, y pueden revelar información importante sobre el mismo. Por ejemplo, las señales medidas del corazón contienen información que puede indicar la presencia de arritmias u otros defectos [9] [10]. El nivel de glucosa en la sangre es un indicador importante para personas que padecen diabetes [12]. Algunas afecciones gastroesofágicas, como el reflujo, pueden ser prevenidas si se conocen los niveles de pH en sitios clave del aparato digestivo [7].

**Figura 1.1:** Representación de diferentes sistemas médicos implantables. Imagen tomada de [1].

1 Introducción 2

Para ilustrar de una manera más adecuada la versatilidad y diversidad que ofrecen estos sistemas, es útil referirse a la figura 1.1. En esta figura se observan diferentes aplicaciones en las que los sistemas implantables encuentran utilidad.

El impacto de estos sistemas implantables no se reduce a labores terapéuticas o de restablecimiento, como es el caso de los implantes cocleares o los marcapasos. El área de la investigación médica también ha obtenido beneficios de los avances en esta tecnología. En particular, se ha visto un progreso importante en el área de la neurociencia, pues la reducción del tamaño de los implantes ha permitido la implementación de plataformas para el estudio de fenómenos del sistema nervioso. En este ámbito, los implantes son diseñados de manera que puedan obtener información de grandes grupos de neuronas, mientras los sujetos estudiados realizan tareas específicas. Esta información se presenta en la forma de señales eléctricas. De esta manera, es posible estudiar el funcionamiento de las redes de neuronas, su respuesta a estímulos y la relación entre las diferentes partes del sistema nervioso [4] [16].

Uno de los principales motores de los avances en este ámbito (los implantes biomédicos) ha sido la investigación en microelectrónica. El refinamiento y el aumento de la complejidad de los implantes se posibilita gracias a las mejoras en los procesos de fabricación de circuitos integrados. Con cada nueva tecnología, se reduce el tamaño de los transistores, lo que permite integrar circuitos con mayores capacidades en áreas menores. Esta tendencia se encuentra en concordancia con las necesidades de la industria médica, pues para que los implantes sean prácticos, su tamaño debe ser reducido en cuanto sea posible.

El flujo de diseño de los circuitos integrados que componen estos sistemas debe contemplar criterios de diseño particulares. Estos criterios, y restricciones, se derivan de la necesidad de disminuir el consumo de potencia, sin dejar de cumplir las necesidades de la aplicación para la que el sistema se ha planteado. En general, dichos circuitos integrados contienen módulos de procesamiento (en forma de microprocesadores, microcontroladores o máquinas de estados finitos); convertidores analógico/digitales (ADCs) y digitales/analógicos (DACs); módulos de almacenamiento de memoria (memorias RAM, bancos de registros); circuitos analógicos de acondicionamiento de señales (amplificadores, filtros, etc); y sensores para la medición de las variables pertinentes.

Además, dos de los componentes a los que se presta más atención son los concernientes a la alimentación del implante y la comunicación del mismo con sistemas exteriores. En el primer caso, algunas de las técnicas de alimentación se basan en baterías. Entre las variedades de las baterías están las no recargables, diseñadas con miras a funcionar por varios años, y las recargables, que son diseñadas para funcionar por períodos menores de tiempo, pero pueden ser recargadas por medio de enlaces inalámbricos. Otra tendencia observada son los implantes que se alimentan únicamente por medio de enlaces inalámbricos.

1 Introducción 3

En cuanto al aspecto de la comunicación, su importancia radica en que, en general, las mediciones realizadas por el implante deben ser almacenadas en dispositivos externos, para que un especialista pueda analizarlos y valorar el estado del paciente. Además, en los casos en los que se implementa un microprocesador en el implante, es posible hacer modificaciones, ajustes y actualizaciones al programa ejecutado por el mismo. La mayor tendencia en este aspecto es la implementación de la comunicación mediante enlaces inalámbricos.

El proyecto descrito en el presente informe forma parte de una iniciativa de investigación en desarrollo, liderada por profesores e investigadores de la Escuela de Ingeniería Electrónica.

#### 1.1 Problema

Aún cuando la investigación en implantes biomédicos es extensa, los esfuerzos y avances observados se realizan de manera aislada. La necesidad de incorporar módulos de procesamiento a los mismos presenta un reto de diseño a los investigadores, el cual puede ser resuelto por medio de diferentes acercamientos. Por un lado, es posible recurrir a alternativas comerciales, como los procesadores ARM. Esto posibilita la reducción de los tiempos de diseño e implementación. Sin embargo, no es posible optimizar dichos módulos, por lo que no se puede reducir su área dentro del circuito integrado, ni su consumo de potencia. Otra alternativa es el diseño integral del procesador o controlador. Esto permite una alta optimización de los recursos, pero se aumenta el tiempo dedicado al diseño del implante.

Por otro lado, otra característica importante a tomar en cuenta de dichos dispositivos es la necesidad de que sean seguros y tolerantes a fallas. La implementación de estas características implicaría una mayor complejidad a nivel de hardware, lo que conlleva un aumento en el consumo de potencia. Sin embargo, es necesario tomar en cuenta estos aspectos, si los implantes diseñados quieren llevarse efectivamente de los laboratorios de investigación a aplicaciones prácticas en hospitales y clínicas.

#### 1.2 Objetivos

#### 1.2.1 Objetivo General

Desarrollar una unidad de procesamiento y control escalable, descrita a nivel RTL para aplicaciones de dispositivos médicos implantables, que pueda ser adaptada en términos de funcionalidad y recursos, y que posea la capacidad de procesamiento necesaria para aplicaciones médicas del sistema cardiovascular.

1 Introducción 4

#### 1.2.2 Objetivos Específicos

• Utilizar la herramienta RocketChip Generator para generar un microprocesador que cumpla con las especificaciones del Set de Instrucciones RISCV en su versión básica (RISC V-IM de 32 bits).

- Implementar un algoritmo de correlación cruzada como método de reconocimiento de patrones en señales en formato *bitstream*.

- Evaluar el rendimiento y la funcionalidad del algoritmo implementado, utilizando el microprocesador generado.

El resto del informe se presenta como sigue: en el Capítulo 2 se presentan los fundamentos teóricos y conceptos utilizados a lo largo del proyecto, prestando especial atención a los detalles que involucran la microarquitectura implementada en RocketChip y los desarrollos matemáticos en los que se basan las técnicas de representación de datos en formato bitstream y la correlación cruzada. Los Capítulos 3 y 4 presentan el desarrollo conceptual y el diseño de la solución propuesta, mientras que el Capítulo 5 contiene los principales resultados obtenidos. Finalmente, en el capítulo 6 se extraen las conclusiones pertinentes en base a los resultados obtenidos, y se presentan algunas recomendaciones.

#### Capítulo 2

#### Marco Teórico

#### 2.1 RocketChip SoC

RocketChip es el producto de una iniciativa que busca el diseño e implementación de un Sistema en Chip (SoC, System-on-Chip) de uso libre. Dicha iniciativa es liderada por investigadores de la Universidad de California-Berkeley. RocketChip cuenta con todos los elementos necesarios de un SoC funcional: procesador(es), memoria(s), buses de datos y control, previstas para periféricos en un modelo de mapeo de memoria, protocolos de coherencia de memorias caché, etc. El código fuente del sistema está escrito en Chisel, un lenguaje de construcción de hardware embebido en Scala. Gracias a la naturaleza de este lenguaje, el código es altamente parametrizable, lo que permite lograr diseños variados con la modificación de pocas líneas de código, dejando el resto intacto. Para generar los diferentes diseños de Rocket, se utiliza una herramienta denominada RocketChip Generator [5].

RocketChip está basado en la Arquitectura de Set de Instrucciones RISC V, e incluye tanto un procesador de ejecución de instrucciones en orden (Rocket), como una máquina de ejecución fuera de orden (BOOM) [5]. El núcleo de procesamiento Rocket es parametrizable. Esto quiere decir que los diferentes dispositivos que lo componen pueden ser añadidos o eliminados deliberadamente, para atender las necesidades de una aplicación específica. Como se mencionó, RocketChip cuenta con los componentes necesarios para la comunicación con dispositivos periféricos. Esta comunicación se lleva a cabo por medio de módulos que cumplan con el protocolo AXI. Además, cuenta con los componentes necesarios para realizar tareas de depuración. Dentro de la arquitectura del SoC, se encuentra la memoria de arranque (BootROM), que contiene el código necesario para la configuración inicial de los registros de Control y Estado (CSR) del procesador. En cualquier implementación de RocketChip, es necesario incluir las memorias caché de Datos e Instrucciones (D\$ e I\$, respectivamente) de primer nivel, que cuentan con comunicación directa con el procesador. Además de estas, opcionalmente pueden incluirse memorias de segundo nivel (L2).

Dentro de RocketChip los diferentes componentes se organizan en distintos bloques según su funcionalidad. Cada núcleo, junto a las memorias caché de datos e instrucciones, la unidad de punto flotante y el coprocesador (si se incluyen) se agrupan dentro de un recuadro (Tile). Cada recuadro se conecta con el resto del sistema utilizando memoria compartida y mapeo de memoria. Para garantizar la coherencia de las memorias caché, se utilizan unidades que cumplan con el protocolo TileLink, el cual se describe más adelante. Con este es posible diseñar una interfaz con buses de sistema que cumplan con el protocolo AXI, por ejemplo. En la figura 2.1 se observa un ejemplo de un sistema diseñado con esta herramienta.

Figura 2.1: Ejemplo de un SoC diseñado utilizando RocketChip Generator. Se observan 2 recuadros, cada uno de los cuales contiene una unidad de procesamiento. En un caso es un núcleo Rocket, en el otro una unidad de ejecución fuera de orden (BOOM). Cada uno de los recuadros cuenta con sus memorias caché de 1er nivel, tanto para datos como instrucciones, y ambos núcleos incluyen FPU y coprocesadores. Figura tomada de [5].

Como se señaló anteriormente, el diseño del sistema puede modificarse con tan sólo alterar el valor de una serie de parámetros. Dentro de las posibilidades disponibles, se puede modificar el tamaño del bus de datos, para que sea 32-bit, 64-bit o 128-bit. También es posible añadir, o eliminar, el soporte para distintos conjuntos de instrucciones de RISC-V, manteniendo siempre el soporte mínimo para el conjunto I (operaciones con enteros) [27]. Ciertos componentes pueden agregarse o eliminarse, como las Unidades de Punto Flotante, las memorias caché de segundo nivel, y los coprocesadores. A continuación, en el código fuente 2.1, se muestra un ejemplo de una configuración básica.

```

class WithNBigCores(n: Int) extends Config((site, here, up) => {

case RocketTilesKey => {

val big = RocketTileParams(

= RocketCoreParams(mulDiv = Some(MulDivParams(

mulUnroll = 8,

mulEarlyOut = true,

divEarlyOut = true))),

dcache = Some(DCacheParams(

rowBits = site (SystemBusParams).beatBits,

nMSHRs = 0,

blockBytes = site(CacheBlockBytes))),

icache = Some(ICacheParams(

rowBits = site (SystemBusParams).beatBits,

blockBytes = site(CacheBlockBytes))))

List. fill(n)(big) ++ up(RocketTilesKey, site)

})

```

Código fuente 2.1: Ejemplo de una configuración básica de un microprocesador Rocket. Se observa como se cambian los parámetros del recuadro que contiene el procesador para modificar las memorias caché y la unidad de multiplicación y división del mismo. Con esta clase se pueden instanciar N procesadores con las características especificadas dentro del mismo recuadro.

Esta configuración puede utilizarse para instanciar n núcleos Rocket. Implícitamente se trata de una arquitectura de 64 bits, dado que el parámetro XLen por defecto tiene un valor de 64. Debido a que la constante mulDiv no se encuentra vacía, se implementa la unidad de multiplicación y división por hardware. Con esto se habilita el soporte para instrucciones del conjunto M de RISC-V. Por otro lado, esta configuración incluye una Unidad de Punto Flotante, debido a que por defecto el valor de la variable fpu es igual a true.

Para cambiar la arquitectura a una de 32 bits, es posible concatenar a dicha configuración una nueva clase, donde explícitamente se declare que XLen debe tener un valor igual a 32. Esta clase se presenta en el código fuente 2.2.

```

class WithRV32 extends Config((site, here, up) => {

case XLen => 32

case RocketTilesKey => up(RocketTilesKey, site) map { r =>

r.copy(core = r.core.copy(

mulDiv = Some(MulDivParams(mulUnroll = 8)),

fpu = r.core.fpu.map(_.copy(divSqrt = false))))

}

```

Código fuente 2.2: Configuración para modificar la arquitectura del procesador (para que sea de 32 bits). Al aplicar esta configuración también deben modificarse los parámetros mostrados de las unidades de Punto Flotante y Multiplicación y División.

Como se observa, para que esta configuración funcione correctamente, también es necesario modificar algunos parámetros para las unidades de multiplicación y división, y de punto flotante. Si además se desea eliminar la FPU, incluir un módulo de depuración JTAG (usando el *Debug Transport Module, DTM*), o cambiar el archivo de inicialización almacenado en la memoria *BootROM*, por ejemplo, se pueden utilizar las clases mostradas en los códigos fuente 2.3, 2.4 y 2.5, respectivamente.

```

class WithoutFPU extends Config((site, here, up) => {

case RocketTilesKey => up(RocketTilesKey, site) map { r =>

r.copy(core = r.core.copy(fpu = None))

}

}

```

Código fuente 2.3: Configuración utilizada para eliminar la Unidad de Punto Flotante. Al retirar esta unidad se elimina también el soporte para la extensión de instrucciones F de RISC V.

```

class WithJtagDTM extends Config ((site, here, up) => {

case IncludeJtagDTM => true

})

```

Código fuente 2.4: Configuración utilizada para instanciar un módulo de depuración JTAG al sistema.

Código fuente 2.5: Configuración para cambiar el archivo de inicialización almacenado en la memoria boot ROM.

#### 2.1.1 Protocolo TileLink

TileLink es un marco de referencia para protocolos que describe la comunicación entre distintos bloques que componen un sistema a escala de circuito integrado. Está diseñado de tal manera que sea un modelo común para las transacciones de coherencia caché dentro de una jerarquía de memoria definida [11]. De esta manera, es posible implementar un protocolo de coherencia y los diferentes agentes necesarios con base en esta especificación.

Con el ánimo de esclarecer el rol de TileLink dentro del sistema en chip, se debe diferenciar entre un protocolo de coherencia y la política o algoritmo de coherencia. El algoritmo, entre otras cosas, define como se representan los permisos y transferencias de diferentes bloques de memoria, así como sus reemplazos, de manera que se pueda sostener el modelo Single Writer-Multiple Readers [11]. Por otro lado, el protocolo define cuáles mensajes se deben intercambiar entre los agentes involucrados en la transacción para implementar dicho algoritmo. La ventaja que ofrece TileLink para este efecto es que implementa un protocolo sobre el cuál pueden implementarse uno o más algoritmos de coherencia deseados, sin que estos afecten las comunicaciones entre los agentes.

De manera similar a distintos protocolos de comunicación, sigue un esquema de Maestro-Esclavo. Dentro de TileLink, los agentes se denominan Administrador y Cliente. Utilizando TileLink dentro del diseño del sistema en chip, es posible lograr la comunicación entre los diversos componentes del mismo, ya sean núcleos de procesamiento, coprocesadores, aceleradores, controladores DMA, y demás, manteniendo la coherencia en la jerarquía de memoria.

#### 2.1.2 Microarquitectura básica del núcleo de procesamiento (Rocket)

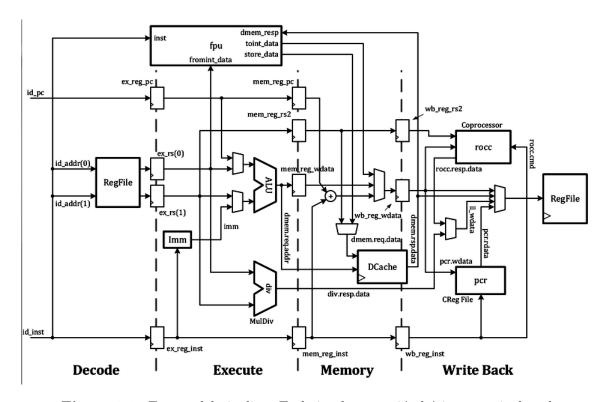

La microarquitectura básica del procesador Rocket está compuesta por un pipeline de 5 etapas (6 si se toma en cuenta el generador de contador de programa, **genpc**). La ejecución de las instrucciones es en orden. En la figura 2.2 se observa el diagrama simplificado del procesador. El núcleo Rocket es, en general, capaz de ejecutar las instrucciones del conjunto G de RISC V, que incluye las instrucciones básicas para números enteros (conjunto I), una extensión para Multiplicaciones y Divisiones (M), las extensiones para operaciones en punto flotante de precisiones sencilla y doble (F y D, respectivamente), y por último las extensiones que incluyen las instrucciones atómicas (A) y comprimidas (C). Sin embargo, para la implementación más sencilla del procesador es posible eliminar la Unidad de Punto Flotante, además de deshabilitar la ejecución de instrucciones atómicas y comprimidas. Con esto el conjunto de instrucciones que ejecuta se reduce únicamente a IM.

Figura 2.2: Microarquitectura del núcleo Rocket, con las etapas (simplificadas) del pipeline. En la etapa de decodificación, el bloque denominado RF corresponde al banco de registros (Register File). El componente BTB corresponde a una unidad de almacenamiento de destino de saltos (Branch Target Buffer), que asiste en la predicción de saltos. Figura tomada de [15].

Con el objetivo de reducir el tamaño del procesador, su complejidad, y con esto, su consumo de potencia, se debe implementar una arquitectura de 32 bits, con soporte para la ejecución de un subconjunto de instrucciones menor a G. Al eliminar la unidad de punto flotante (FPU), se deshabilita el roporte para los conjuntos de instrucciones F y D. Con esto el conjunto de instrucciones que ejecuta se reduce a IMAC.

#### 2.1.3 Memorias Caché de 1er Nivel

En el diseño básico se utilizan dos memorias caché dentro del recuadro que contiene el núcleo. Estas memorias caché utilizan un mapeo asociativo de conjuntos (Set-Associative Mapping). De esta manera, utilizando ciertos parámetros que se encuentran expuestos en el RocketChip Generator, es posible modificar su tamaño y asociatividad.

Los parámetros son:

- nWays.

- nSets.

El parámetro nSets determina el número de conjuntos utilizados. Estos conjuntos, a su vez, están compuestos por una cantidad de líneas determinada por el parámetro nWays. Estas líneas son las unidades fundamentales a las que cada bloque de la memoria principal se asocia utilizando el mapeo. Estos bloques, y consecuentemente, las líneas de las memorias caché, pueden almacenar una cantidad de palabras o bytes según el diseño de la memoria. Para RocketChip, cada línea puede almacenar 64 Bytes.

Según [24] el mapeo asociativo por conjuntos está planteado de manera que tenga las ventajas de los mapeos directo y asociativo, minimizando sus desventajas. Cada dirección de la memoria principal se interpreta dividiéndola en tres partes: la etiqueta (tag), el conjunto (set), y la palabra (word). Los d bits que especifican el conjunto pueden apuntar a cualquiera de los  $2^d$  conjuntos definidos en los parámetros expuestos en RocketChip. Además, para representar el bloque de memoria, se utilizan s bits, que contienen tanto los bits de la etiqueta, como los bits del conjunto. Con estos se puede especificar cualquiera de los  $2^s$  bloques de la memoria principal. Al aumentar la cantidad de conjuntos, el tamaño de la etiqueta disminuye considerablemente con respecto al tamaño de la misma utilizando un mapeo de memoria puramente asociativo. Conforme disminuye la cantidad de líneas por conjunto, el mapeo se acerca más al comportamiento de un mapeo directo. Por otro lado, si la cantidad de conjuntos se acerca a 1, y el número de líneas por conjunto es igual al número de líneas en la caché, el mapeo se comporta como un mapeo puramente asociativo [24].

#### 2.1.4 Soporte de Depuración Externa para RISC-V

Actualmente, RocketChip implementa un sistema de depuración externa que cumple con la norma RISC V External Debug Support 0.13, para la verificación del funcionamiento del SoC [21]. Esta depuración se hace por medio de un dispositivo externo, como una laptop, que se conecta con la plataforma RISC-V utilizando hardware de depuración (e.g. un adaptador USB/JTAG). Dentro de la plataforma RISC-V, en este caso RocketChip, se encuentran el módulo de transporte de depuración (Debug Transport Module, DTM), una interfaz DMI (Debug Module Interface) y un módulo de depuración (Debug Module, DM).

Por medio del hardware mencionado, un usuario que utilice el dispositivo externo puede emitir comandos y enviar datos a la plataforma, para así modificar el comportamiento de la plataforma con el fin de verificar su funcionamiento. Utilizando esta herramienta se tiene la capacidad de detener o reanudar la ejecución de un hart (Hardware Thread). En la figura 2.3 se observa la arquitectura de este sistema de depuración.

**Figura 2.3:** Arquitectura del sistema de depuración externa. Se observa como la interfaz DMI sirve de puente entre el módulo de depuración DM y el DTM. Figura tomada de [21].

#### 2.1.5 Diagramas de referencia

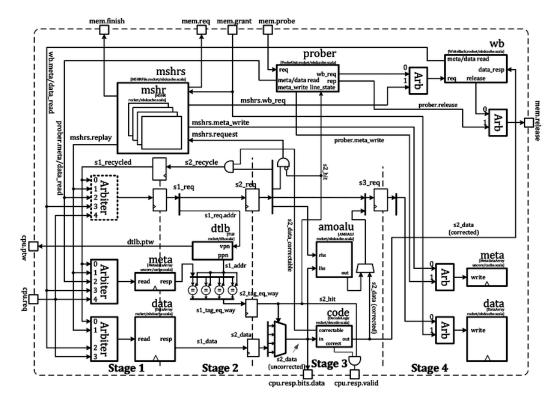

En la figura 2.4, se observan las etapas del procesador de una manera detallada. La memoria cache de instrucciones se encuentra en la etapa Fetch. Por otra parte, la memoria cache de datos se observa en la etapa Memory. En la etapa de Ejecución se tienen las unidades aritmético-lógica, IMUL e IDIV. En la implementación básica del núcleo, dado que se elimina el soporte para el conjunto M de instrucciones, la unidad IMUL no aparece.

Figura 2.4: Microarquitectura del núcleo de procesamiento Rocket. Se muestran los bloques funcionales de los que está compuesto el mismo. Se pueden observar las señales y colas que comunican el núcleo con la FPU, TileLink, HTIF (Host Target Interface) y PTW. Figura tomada de [15].

En las figuras 2.5, 2.6 y 2.7, se muestran diagramas de bloques para el generador del contador de programa, además de las diferentes etapas del pipeline del procesador. También se tiene un diagrama de la memoria caché de datos. Los nombres de las señales en estos diagramas corresponden a los de la descripción RTL.

Figura 2.5: Generador de PC y etapa Fetch. Figura tomada de [3].

**Figura 2.6:** Etapas del pipeline. En la implementación básica no se incluye la unidad de punto flotante. Figura tomada de [3].

Figura 2.7: Memoria caché de datos. Figura tomada de [3].

Cabe resaltar que estos diagramas son una guía, más que una descripción exacta de la microarquitectura básica generada. Esto porque en estos aún se muestran unidades que se eliminaron para disminuir el consumo de potencia y el área utilizada, como la unidad de punto flotante. Además la ubicación en la que e muestran algunos módulos no corresponde exactamente a su posición en la descripción RTL. Un ejemplo de esto son las memorias caché D e I, que se muestran dentro de las etapas del pipeline, pero en realidad se implementan en módulos separados del núcleo, siempre dentro del mismo recuadro.

#### 2.2 Correlación Cruzada de Señales

Para validar el sistema desarrollado en este proyecto, se propone la implementación de un algoritmo de correlación cruzada para la detección de eventos (latidos) en electrocardiogramas. En esta sección se presentan los fundamentos teóricos que respaldan este método.

La correlación entre dos señales es un método matemático que permite obtener el grado de similitud entre dos señales, o el desfase entre las mismas [22]. Resulta una herramienta útil cuando se desea extraer características de señales desconocidas, valiéndose de la comparación con una señal previamente estudiada.

Matemáticamente se puede definir como

$$(f \star g)(\tau) = \int_{-\infty}^{\infty} f^*(t)g(t+\tau)dt \tag{2.1}$$

para señales continuas. Si se trabaja con señales discretas, la definición cambia a

$$(f \star g)[t] = \sum_{k=0}^{n-1} f^*[k]g[t+k]$$

(2.2)

donde f\* es el conjugado complejo de f [17].

Se puede observar que, dada la naturaleza de la correlación, es conveniente realizar el cálculo utilizando las señales representadas en un formato *bitstream*. Con esto es posible reducir la carga computacional [25]. La operación adecuada para obtener el resultado de la correlación es una XNOR, ejecutada bit por bit, como se puede observar en la tabla 2.1.

| A | В | XNOR ⊙ |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

Tabla 2.1: Tabla de verdad de la función lógica XNOR.

Se observa como esta función lógica es adecuada para calcular la correlación, pues siempre y cuando el valor de cada bit coincida con entre ambas señales, el valor de salida será un 1 lógico. Con esto, entre mayor sea la similitud de las señales comparadas, mayor será la cantidad de 1's dentro del resultado, como es de esperarse.

#### 2.3 Representación de señales en formato bitstream

Normalmente, la representación bitstream de señales se usa en las etapas intermedias de convertidores Analógico/Digitales (ADC), o Digital/Analógicos (DAC) de tipo Sigma Delta  $(\Sigma\Delta)$ . Este tipo de dispositivos se denominan convertidores de sobremuestreo, pues trabajan a una frecuencia mayor a la frecuencia de Nyquist de las señales de interés. La tasa de muestreo se representa como

$$F_s = OSR * f_s \tag{2.3}$$

donde  $F_s$  es la tasa de muestreo del convertidor, OSR es la razón de sobremuestreo (*Over-Sampling Ratio*), y  $f_s$  es la frecuencia de Nyquist. El objetivo de utilizar esta técnica es lograr señales de alta fidelidad, disminuyendo el error de codificación.

En principio, estos dispositivos utilizan un modulador  $\Sigma\Delta$  para obtener la representación bitstream de la señal. Posteriormente, se realizan dos procesos adicionales: un filtrado de la señal, para pasar de una modulación por densidad de pulsos a una modulación por pulsos codificados; y por último un diezmado, para bajar el muestreo de la señal resultante a la frecuencia de muestreo de Nyquist. Con esto se obtiene una representación fiel de la señal de entrada, sin acumular datos innecesarios a la salida, pues la tasa de muestreo se disminuye hasta alcanzar el límite donde se puede asegurar que no existe aliasing.

#### 2.4 Señales de Electrocardiogramas: ECG

Un electrocardiograma se define como la grabación y registro del cambio de potenciales eléctricos con respecto al tiempo. Estos potenciales se refieren particularmente a los que se producen debido a la contracción de los músculos cardíacos (miocardio) [14]. Los electrocardiogramas representan una de las herramientas de diagnóstico más utilizadas en cardiología, por la gran cantidad de información que pueden contener.

El uso de los electrocardiogramas se ha extendido debido a las ventajas que posee. En primer lugar, las señales son fáciles de obtener, debido a que se requiere un procedimiento poco invasivo. Los electrodos utilizados para la adquisición de las señales se colocan en la superficie de la piel, sin necesidad de intervenciones quirúrgicas. Otra ventaja que poseen es su bajo costo, lo que convierte a esta técnica en un método posible de implementar en diferentes escenarios.

#### 2.4.1 Mecanismos de conducción eléctrica en el corazón

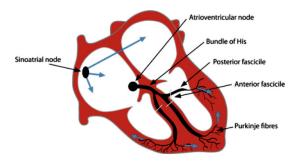

Para comprender el origen de las señales que se ven representadas en la grabación de un electrocardiograma, es necesario introducir el sistema de conducción eléctrica del corazón. En primer lugar, se debe resaltar que la actividad eléctrica en este órgano es producto de reacciones químicas, las cuáles toman lugar en ciertas secciones particulares del mismo.

Los músculos cardíacos están compuestos, principalmente, por dos tipos de células. Se tienen los cardiomiocitos, que al contraerse generan potenciales eléctricos. A su vez, se tienen células especializadas en la generación y conducción de los potenciales de acción [14]. Los potenciales de acción se refieren a descargas eléctricas dentro del tejido, que cambian la distribución de las cargas eléctricas en el mismo.

En general, en estado de reposo, los cardiomicoitos se encuentran polarizados con un potencial de membrana de alrededor de -90 mV [14]. Es importante aclarar, en este punto, que al mencionar el potencial de membrana se refiere a la diferencia de potencial eléctrico a ambos lados de una membrana celular. Esta diferencia de potencial se ocasiona por la presencia de dos sustancias de diferente concentración de iones a ambos lados de la

membrana. Ahora, un estímulo externo puede iniciar un proceso de despolarización, en el cual se permite la entrada de iones positivos de sodio (y en algunos casos, de calcio) dentro de la membrana. En este proceso se revierte el potencial eléctrico en las células del miocardio. Luego de la despolarización, el músculo cardíaco vuelve a su estado eléctrico inicial.

La fase de repolarización se refiere al cambio hacia abajo del potencial de acción, ocasionado principalmente por la salida de iones de potasio fuera de la célula. Una característica importante de este proceso de repolarización es que durante este el miocardio no puede ser estimulado, lo que protege el músculo contra estímulos prematuros.

Figura 2.8: Ilustración del corazón, en la que se señalan los elementos principales involucrados en los procesos de conducción eléctrica. Las cavidades derechas (aurícula y ventrículo) se ubican a la *izquierda* de la ilustración, según el punto de vista del lector. Figura tomada de [14].

En la figura 2.8 se muestra una ilustración básica de la estructura del corazón, prestando especial atención a los elementos involucrados en la conducción eléctrica dentro del miocardio. Se observan 4 cavidades principales [28]:

- Aurículas: cavidades superiores, divididas a su vez en aurícula derecha y aurícula izquierda. Estas cavidades se encargan de recolectar la sangre que ya ha circulado por todo el organismo.

- Ventrículos: cavidades inferiores, que se dividen en ventrículo izquierdo y ventrículo derecho. Estas cavidades toman la sangre de su respectiva aurícula, y se contraen para bombear la sangre de vuelta al resto del cuerpo.

Se observa que existe una división en la organización de las cavidades, de manera que los lados izquierdo y derecho se encuentran separados. Esta división tiene un carácter funcional, pues responde a la necesidad de cada uno de los lados de proveer la sangre para una sección del organismo específica. El lado derecho se encarga de la circulación de la sangre en el sistema pulmonar, mientras que la región izquierda hace su parte para el resto de los sistemas del organismo [28].

En un estado normal, las contracciones que permiten el movimiento de la sangre a través de dichas cavidades están reguladas por un marcapasos natural. Esta función se lleva a cabo en el nodo sinoauricular (sinoatrial node). Este nodo se denota con la abreviatura SA. La función principal del nodo SA es la de generar impulsos eléctricos que inician la con-

tracción de la aurícula derecha, mediante procesos de despolarización espontánea. Además, el sistema de conducción incluye el nodo atrio ventricular (AV), ubicado en la cercanía de la división entre las cavidades superior e inferior. Las células de este nodo también presentan un proceso de despolarización espontáneo, pero a una frecuencia menor que la del nodo SA. Esta actividad funciona (en parte) como un respaldo para la despolarización del nodo SA, y en condiciones normales el efecto de estos procesos es suprimido por la acción de este mismo nodo. Por último, algunos otros elementos importantes de este sistema son el haz de His, y las fibras de Purkinje. El haz de His es una membrana celular que permite la conducción de pulsos eléctricos desde el nodo AV hacia otras regiones del corazón. Las fibras de Purkinje también presentan automaticidad, generando pulsos a una tasa de aproximadamente 30 bpm [14].

#### 2.4.2 Elementos importantes presentes en un electrocardiograma

Los electrocardiogramas almacenan información importante sobre el funcionamiento y estado del sistema cardiovascular del paciente estudiado. Para facilitar su interpretación, en un electrocardiograma se identifican diversas secciones y elementos que evidencian el funcionamiento de los diferentes componentes del sistema de conducción eléctrico del corazón.

En la figura 2.9 se presentan algunas de las secciones, intervalos y ondas más importantes que se observan en un electrocardiograma.

**Figura 2.9:** Ejemplo típico de un electrocardiograma, se observan las principales ondas e intervalos que se presentan en un ECG. Se pueden observar los intervalos RR, PR y QT, además del complejo QRS y las ondas T y P. Figura tomada de [14].

El primer elemento que se presenta en un ECG es la onda P, característica de la despolarización de las aurículas. El proceso de repolarización de estas cavidades no se puede observar en un electrocardiograma, pues ocurre durante la despolarización de los ventrículos y es opacado por esta actividad. La onda P tiene una duración normal de 0,12 segundos, y su amplitud es cercana al rango de 0,25 - 0,15 mV, al utilizar las derivaciones de las extremidades superiores. Si esta amplitud supera los valores mencionados, y además la onda presenta muescas o deformaciones, se considera que existe un comportamiento anormal, lo que puede indicar deformaciones en las aurículas.

Otro elemento importante que puede observarse es el complejo QRS, que es la manifestación de la despolarización de las cavidades ventriculares. Como se puede intuir de su nombre, este complejo se compone por las ondas Q, R y S. Típicamente, la duración de este complejo no es mayor a los 0,12 segundos, similar a la onda P. Una duración mayor a este valor puede resultar de asincronías en la despolarización de ambos ventrículos. Esto ocurre en casos en los que se presentan síndromes de pre-exitación o contracciones ventriculares prematuras.

El intervalo RR representa la duración de un ciclo cardíaco, y con este se puede determinar ritmo cardíaco del sujeto de la prueba. En este informe, el ciclo cardíaco utilizado para la obtención del patrón y la detección de eventos corresponde al segmento del electrocardiograma desde la onda P hasta las vecindades de la onda U.

#### Capítulo 3

# Implementación de un SoC basado en RocketChip

Como un primer acercamiento a la resolución del problema descrito, se plantea utilizar un microprocesador de uso libre para evaluar su rendimiento ante tareas y algoritmos típicos de dispositivos médicos implantables. Para este efecto se deben considerar diferentes candidatos para realizar la evaluación. El primer aspecto a tomar en cuenta es la arquitectura de set de instrucciones a utilizar. Para esta variable, la mayor parte del desarrollo tecnológico cae dentro de dos categorías: RISC (Reduced Instruction Set Computer) y CISC (Complex Instruction Set Computer). Algunas de las ventajas y desventajas de ambas opciones se presentan en la tabla 3.1.

Se observa que, por la naturaleza de los implantes médicos, los computadores RISC presentan características ventajosas. Por ejemplo, al necesitar componentes de hardware de menor complejidad, el área del microprocesador, y su consumo de potencia, se ven disminuidos. Además, a pesar de que cada programa, al expresarse en lenguaje ensamblador, resulta más complejo y extenso por la capacidad reducida de las instrucciones RISC, esta complejidad extra se enmascara dentro de los compiladores, que tienden a ser muy eficientes para estas arquitecturas.

El siguiente paso es escoger, dentro de los Sets de Instrucciones RISC, el más adecuado para el desarrollo del proyecto. Algunas opciones son ARM, OpenRISC, MIPS y RISC V. De estas, ARM y MIPS son propietarias, por lo que su uso está limitado por el pago de licencias. Por otro lado, OpenRISC es una arquitectura que carece de un ambiente activo de desarrollo y mantenimiento, por lo que también se limita su factibilidad. Por otro lado, RISC V cuenta con un conjunto de organizaciones activas en el área de la investigación y el desarrollo comercial. Por ser un estándar vigente, con amplio respaldo, documentación y mantenimiento, presenta las mayores ventajas como plataforma base para el desarrollo de proyectos de hardware libre.

Tabla 3.1: Comparación entre dos categorías de arquitecturas de computadores.

| Arquitectura de<br>Computador | Ventajas                                                                                                                                 | Desventajas                                                                                                                                                |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CISC                          | Permite diseñar software con una menor cantidad de instrucciones. El procesador debe ejecutar menos instrucciones.                       | Aumento de la complejidad del hardware, e. g. el decodificador es más lento y requiere un área mayor [6]. El tiempo de ejecución por instrucción es mayor. |

| RISC                          | Hardware más sencillo. Menor tiempo de ejecución por instrucción.  Modos de direccionamiento, y formato de instrucciones sencillos [24]. | El software se vuelve más complejo y elaborado. Se necesitan más líneas de código para realizar las mismas tareas, i.e. menor densidad de código [6].      |

Parte del auge experimentado por el set de instrucciones RISC V se debe a su adopción, para la implementación de microprocesadores y sistemas en chip, por parte de grupos de investigación de universidades como ETH Zurich, la Universidad de Bolonia, y la Universidad Industrial de Santander, por nombrar algunos [2]. En su mayoría, estos operan bajo licencias abiertas (como las licencias Apache, BSD y MIT), lo que los transforma en candidatos adecuados para el desarrollo de plataformas estándar de implantes biomédicos. Como ejemplos de estas plataformas se pueden nombrar el SoC RocketChip (junto al procesador Rocket), y los procesadores ORCA, PULPino y OPenV/mriscv [2]. De estas plataformas, se elige trabajar con RocketChip debido a su descripción en alto nivel, su alto grado de parametrización, y la flexibilidad que ofrece para modificar la microarquitectura para adaptarla a la aplicación planteada.

Una vez definida la plataforma de hardware a utilizar, se procede a realizar el diseño del Sistema en Chip deseado, con el que se pueden realizar pruebas de funcionamiento y evaluaciones. RocketChip, además de proveer el SoC, cuenta con un conjunto de benchmarks y asm-tests (assembly tests), para la verificación y estudio de la ejecución de instrucciones RISC V. Con estos programas de prueba es posible conocer el rendimiento de la arquitectura generada, además de verificar la ejecución de las instrucciones relevantes.

#### 3.1 Sistema en Chip Generado

El código en Chisel necesario para describir el SoC deseado se presenta en el código fuente 3.1. Cabe resaltar que, dentro de la clase WithNTinyCores, se instancian dos memorias caché de primer nivel, para instrucciones y datos. Sin embargo, la caché de datos (en la declaración original) cuenta con 256 Sets. Por esta razón, para disminuir su tamaño (y con esto el tamaño del sistema), se limita este número a 64. Con esta configuración, se genera un SoC que cuenta con un solo núcleo de procesamiento de 32 bits, el cuál está desprovisto de FPU, y cuenta con 2 memorias caché de 4096 bytes.

```

class RocketRV32i extends Config(

// Estas dos primeras configuraciones deben estar presentes

new WithNMemoryChannels (0) ++

new WithStatelessBridge ++

// TinyCores es de 32 bits, sin FPU, con MulDiv