# Instituto Tecnológico de Costa Rica Escuela de Ingeniería Electrónica

Diseño, estudio e implementación de técnicas de diseño DFT para un microprocesador de propósito general

Informe de Proyecto de Graduación para optar por el título de Ingeniero en Electrónica con el grado académico de Licenciatura

Luis Enrique Alfaro Rojas

Cartago, Semestre I 2018

# INSTITUTO TECNOLÓGICO DE COSTA RICA ESCUELA DE INGENIERÍA ELECTRÓNICA PROYECTO DE GRADUACIÓN ACTA DE APROBACIÓN

Defensa de Proyecto de Graduación Requisito para optar por el título de Ingeniero en Electrónica Grado Académico de Licenciatura Instituto Tecnológico de Costa Rica

El Tribunal Evaluador aprueba la defensa del proyecto de graduación denominado Diseño, estudio e implementación de técnicas de diseño DFT para un microprocesador de propósito general, realizado por el señor Luis Enrique Alfaro Rojas y, hace constar que cumple con las normas establecidas por la Escuela de Ingeniería Electrónica del Instituto Tecnológico de Costa Rica.

Miembros del Tribunal Evaluador

Ing. Anibal Ruíz Barquero

Ing. Esteban Baradín Méndez

Profesor lector

Profesor lector

Ing. Roberto Molina Robles

Profesor asesor

Cartago, 25 de junio, 2018

# Declaratoria de Autenticidad

Declaro que el presente Proyecto de Graduación ha sido realizado, en su totalidad, por mi persona, utilizando y aplicando literatura referente al tema e introduciendo conocimientos propios.

En los casos en que he utilizado material bibliográfico, he procedido a indicar las fuentes mediante citas.

En consecuencia, asumo la responsabilidad total por el trabajo de graduación realizado y por el contenido del correspondiente informe final.

1-1535-064

Luis Enrique Alfaro Rojas

Céd. 1-1535-0672

Cartago Junio, 2018.

# Resumen

En este documento se resume el procedimiento que se siguió para estudiar el funcionamiento y utilización de 3 técnicas de diseño de DFT, las cuales buscan mejorar ciertas características de los circuitos digitales para reducir el tiempo invertido en el desarrollo e implementación de pruebas una vez manufacturados los dispositivos.

Desde la aparición de los circuitos integrados el diseño y la prueba de los circuitos una vez producidos han sido todo un reto para los diseñadores, debido a lo difícil que se torna el diseñar diferentes patrones de entradas necesarios para fijar estados internos y extraer datos, por ello muchos algoritmos de probabilidad se desarrollaban para establecer la buena o mala producción de un integrado. En este documento se trata una parte de la solución que se utiliza desde hace varias décadas, el DFT, Design For Testability.

DFT mejora la controlabilidad y observabilidad de los circuitos digitales secuenciales. La controlabilidad se refiere a que tan fácil se puede cambiar el estado lógico de una señal interna, y la observabilidad que tan sencillo es ver el estado lógico de una señal interna por medio de un pin físico del dispositivo que se diseña.

Se estudian tres técnicas básicas de DFT los cuales buscan mejorar la controlabilidad y observabilidad, la detección de grandes retardos en señales internas y reducir los tiempos de ejecución de pruebas. Para lograr completar el estudio, se realizan diferentes diseños de un mismo circuito digital aplicando las diferentes técnicas, una vez conseguido ello, se procede a realizar simulaciones de operación y pruebas, se obtienen datos de consumo de potencia y consumo de recursos.

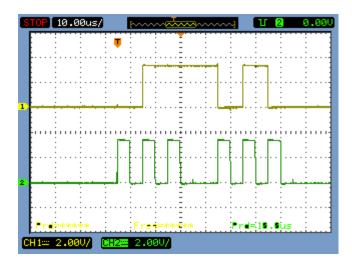

Finalmente se implementan los diseños en un circuito de pruebas como lo es la Nexys 4 de Digilent, la cual contiene una FPGA Artix 7 capaz de simular desde circuitos combinacionales simples, hasta microprocesadores complejos, lo que la convierte en una tarjeta muy versátil. Para obtener los resultados de la implementación se utiliza un osciloscopio Tektronix TDS-220.

Palabras clave: Circuito digital, Design For Testability, Nexys 4, Máquinas de estado, Flip-Flop.

# Abstract

This document resumes the procedure that was followed to study the functionality and the use of some DFT design techniques, that try to improve some features of digital circuits, with the goal of reduce the time invested on the development and implementation of tests when the devices are manufactured.

Since the appearance of the integrated circuits, the design and tests of the circuits when are produced have being a challenge for the designers, because it's too hard to design the required patterns of inputs to set some internal signals and to extract internal data, that is the reason because some probability algorithms was designed to establish the good or bad production of an integrated circuit. In this document the theme is about a little part of the solution that some engineers applied since a few decades ago, DFT, Design For Testability.

DFT improves the controllability and observability of sequential digital circuits. The controllability refers to how easy is to set an internal signal, and the observability is about of how easy is to get an internal signal state on a physical pin of the device that is being designed.

Three basic techniques of DFT that search the improve of controllability and observability, the detection of internal big latches and reduce the execution time of test, are studied. To achieve the study completion, a sort of different designs of the same circuit applying this techniques are developed, when that goal have being achieve, some simulations of functionality and tests are executed, and the power and resources consumption.

For the finish of the document and project the developed designs are implemented on a tests circuit board like the Nexys 4 of Digilent is, that board contents an Artix 7 FPGA that can simulate since simple combinational circuits until complex microprocessors, that feature tells how versatile is the board. To obtain the results of the implementation a Tektronix TDS-220 oscilloscope is used.

Keywords: Digital circuit, Design For Testability, Nexys 4, States Machine, Flip-Flop.

# Agradecimientos

Agradezco a los compañeros y amigos que conocí durante mi estadía en el TEC, quienes hicieron del día a día un motivo más por el qué avanzar siempre. A los profesores que conocí a lo largo de la carrera, quienes siempre inculcaron un espíritu de lucha, nunca rendirse y siempre esforzarse para cumplir los objetivos.

Le agredezco a mi familia por el apoyo incondicional que me brindaron a lo largo de mi carrera universitaria, e incluso a lo largo de la vida. Siempre dándome el ejemplo al no rendirse ni afligirse ante los momentos dfíciles que hemos pasado juntos y principalmente respetar las demás personas.

Le agradezco principalmente a mi madre Jeannethe Rojas Agüero quién siempre ha estado a mi lado y me ha apoyado en mi toma de decisiones, mujer a la que admiro y respeto por sobre todas las cosas y a la que nunca podré pagarle por todo lo que me ha dado y enseñado.

Especialmente le dedico este trabajo y mi título a mi hermano Kenneth Alfaro Rojas quién sé que desde el cielo me está viendo y cuidando, y como siempre, riendo de mis tonterías.

# Índice general

| R            | esumen                                  | II          |

|--------------|-----------------------------------------|-------------|

| $\mathbf{A}$ | bstract                                 | III         |

| A            | gradecimientos                          | IV          |

| ${f Li}$     | ista de figuras                         | VIII        |

| Li           | ista de cuadros                         | X           |

| 1.           | Introducción 1.1. Entorno               | 1<br>1<br>3 |

| 2.           | Propuesta de solución                   | 4           |

|              | 2.1. Enfoque de solución                | 4<br>5      |

| 3.           | Meta y Objetivos                        | 6           |

|              | 3.1. Meta                               | 6           |

|              | 3.2. Objetivo general                   | 6           |

|              | 3.3. Objetivos específicos              | 7           |

| 4.           | Marco Teórico                           | 8           |

|              | 4.1. DUT                                | 8           |

|              | 4.2. Design For Testability (DFT)       | 8           |

|              | 4.3. Scan Cells                         | 9           |

|              | 4.4. Scan Chain                         | 10          |

|              | 4.5. Ruta Crítica                       | 11          |

|              | 4.6. Vectores de Prueba                 | 11          |

|              | 4.7. Scan Design                        | 12          |

|              | 4.8. Diagrama de Flujo para Scan Design | 15          |

|              | 4.9. Scan Hold Flip Flop                | 17          |

|              | 4.10. Enhanced Scan                     | 18          |

|              | 4.11. Snapshot Scan                     | 19          |

|              | 4.12. Error-Resilient Scan              | 21          |

| <b>5</b> . | $\operatorname{Des}$ | arrollo de Solución                                           |

|------------|----------------------|---------------------------------------------------------------|

|            | 5.1.                 | Circuito de pruebas                                           |

|            | 5.2.                 | Uso de software para prueba de diseños HDL                    |

|            |                      | 5.2.1. Chipscope Pro                                          |

|            | 5.3.                 | Diseño de circuito de adquisición y generación de datos       |

|            |                      | 5.3.1. Circuito de control para Scan Design basico            |

|            |                      | 5.3.2. Circuito de control para Enhanced Scan                 |

|            |                      | 5.3.3. Circuito de control para Snapshot Scan                 |

|            | 5.4.                 | Circuito de prueba con Scan Design                            |

|            | 5.5.                 | Circuito de Prueba con Enhanced Scan                          |

|            | 5.6.                 | Circuito de Prueba con Snapshot Scan                          |

|            | 0.0.                 | oneand de l'idead com amapanot accur vivivivivivivivivivivivi |

| 6.         | Res                  | ultados                                                       |

|            | 6.1.                 | Circuito de pruebas                                           |

|            |                      | 6.1.1. Simulación                                             |

|            |                      | 6.1.2. Consumo de potencia                                    |

|            | 6.2.                 | Circuito de pruebas con ChipScope                             |

|            |                      | 6.2.1. Simulación de circuito creado con Chipscope            |

|            |                      | 6.2.2. Consumo de potencia                                    |

|            | 6.3.                 | Circuito de control para Scan Design                          |

|            |                      | 6.3.1. Simulación                                             |

|            |                      | 6.3.2. Consumo de potencia                                    |

|            | 6.4.                 | Circuito de control para Enhanced Scan                        |

|            | 0.1.                 | 6.4.1. Simulación                                             |

|            |                      | 6.4.2. Consumo de potencia                                    |

|            | 6.5.                 | Circuito de control con Snapshot                              |

|            | 0.0.                 | 6.5.1. Simulación                                             |

|            |                      | 6.5.2. Consumo de potencia                                    |

|            | 6.6.                 | Circuito de pruebas con Scan Design                           |

|            | 0.0.                 | 6.6.1. Simulación                                             |

|            |                      | 6.6.2. Consumo de potencia                                    |

|            |                      | 6.6.3. Señales obtenidas de FPGA                              |

|            | 6.7.                 | Circuito de pruebas con Enhanced Scan                         |

|            | 0.1.                 | 6.7.1. Simulación                                             |

|            |                      | 6.7.2. Consumo de potencia                                    |

|            |                      | 6.7.3. Señales obtenidas de FPGA                              |

|            | 6.8.                 | Circuito de pruebas con Snapshot Scan                         |

|            | 0.0.                 | -                                                             |

|            |                      | 6.8.1. Simulación                                             |

|            |                      | 6.8.2. Consumo de potencia                                    |

|            |                      | 6.8.3. Señales obtenidas de FPGA                              |

| 7          | Aná                  | disis de Resultados                                           |

| ١.         | 7.1.                 | Circuito inicial de pruebas                                   |

|            | 7.1.                 | *                                                             |

|            |                      | ·                                                             |

|            | 1.3.                 | Consumo de potencia de circuitos de pruebas rediseñados       |

|    | 7.4.   | Recursos de FPGA utilizados por circuitos rediseñados         | 65         |

|----|--------|---------------------------------------------------------------|------------|

|    | 7.5.   | Consumo de potencia de circuitos de control                   | 66         |

|    | 7.6.   | Recursos de FPGA utilizados por circuitos de control          | 67         |

|    | 7.7.   | Señales adquiridas de implementación en FPGA                  | 68         |

|    | 7.8.   | Aplicación en un microprocesador o cualquier circuito digital | 69         |

| 8. | Con    | iclusiones y Recomendaciones                                  | 71         |

|    | 8.1.   | Conclusiones                                                  | 71         |

|    | 8.2.   | Recomendaciones                                               | 73         |

| Bi | bliog  | grafía                                                        | <b>7</b> 4 |

| Aı | Anexos |                                                               |            |

# Índice de figuras

| 1.  | Celda de escaneo. Tomado de $[1]$                                          | 9  |

|-----|----------------------------------------------------------------------------|----|

| 2.  | Cadena de escaneo (Scan Chain)                                             | 10 |

| 3.  | Ejemplo de ruta crítica de un circuito combinacional                       | 11 |

| 4.  | Ejemplo de circuito secuencial. Tomado de [2]                              | 12 |

| 5.  | Ejemplo de circuito secuencial con SFF. Tomado de [2]                      | 13 |

| 6.  | Ejemplo de Partial-Scan design. Tomado de [2]                              | 13 |

| 7.  | Ejemplo de Random-Access-Scan design. Tomado de [2]                        | 14 |

| 8.  | Diagrama de flujo para implementar el scan design. Tomado de [2]           | 15 |

| 9.  | Esquema de un SHFF. Tomado de [1]                                          | 17 |

| 10. | Esquema de un circuito con Enhanced Scan. Tomado de [1]                    | 18 |

| 11. | Diagrama de señales de un circuito con Enhanced Scan. Tomado de [1]        | 18 |

| 12. | Diagrama de señales de un circuito con Snapshot Scan. Tomado de $[1]$      | 19 |

| 13. | Esquema de celda utilizada para Error-Resliente Scan. Tomado de [1]        | 21 |

| 14. | Circuito inicial de pruebas. Tomado de [2]                                 | 24 |

| 15. | Tabla de transiciones de circuito de pruebas. Tomado de [2]                | 25 |

| 16. | Diagrama de estados de circuito de pruebas. Tomado de [2]                  | 25 |

| 17. | Circuito de pruebas modificado con Chipscope                               | 26 |

| 18. | Diagrama de circuito de adquisicion y generación de datos                  | 27 |

| 19. | Diagrama de estados de control para Scan Design                            | 28 |

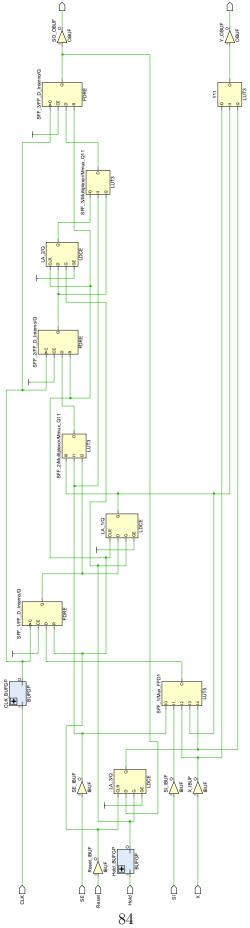

| 20. | Esquemático de circuito de control para Scan Design                        | 29 |

| 21. | Esquemático Post synthesis de circuito de control para Scan Design         | 30 |

| 22. | Diagrama de tiempo para pruebas en Scan Design. Tomado de 2                | 30 |

| 23. | Esquemático de circuito de control para Enhanced Scan                      | 32 |

| 24. | Esquemático Post synthesis de circuito de control para Enhanced Scan       | 32 |

| 25. | Diagrama de tiempo para pruebas en Enhanced Scan. Tomado de 2              | 33 |

| 26. | Diagrama de estados de control para Enhanced Scan                          | 34 |

| 27. | Esquemático de circuito de control para Snapshot Scan                      | 35 |

| 28. | Esquemático Post synthesis de circuito de control para Snapshot Scan       | 35 |

| 29. | Sección de Esquemático Post synthesis de circuito de control para Snapshot |    |

|     | Scan                                                                       | 36 |

| 30. | Diagrama de estados de control para Snapshot Scan                          | 37 |

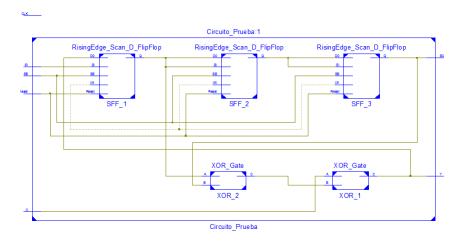

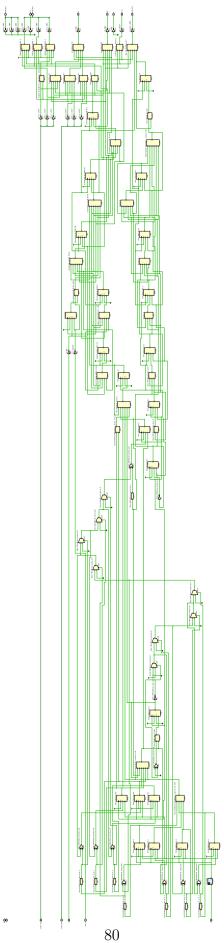

| 31. | Circuito de pruebas con Scan Design                                        | 38 |

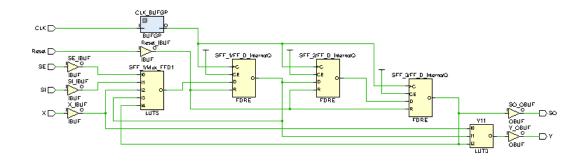

| 32. | Circuito de pruebas postsynthesis con Scan Design                          | 39 |

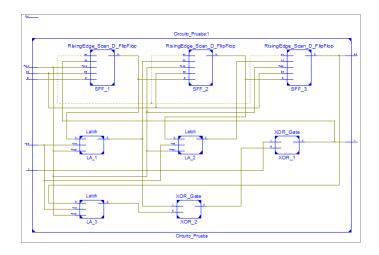

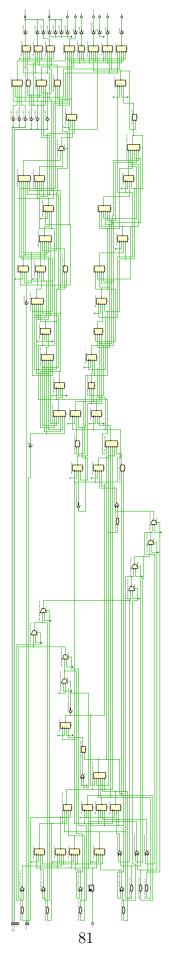

| 33. | Circuito de pruebas con Enhanced Scan                                      | 40 |

| 34. | Circuito de pruebas postsynthesis con Enhanced Scan                        | 40 |

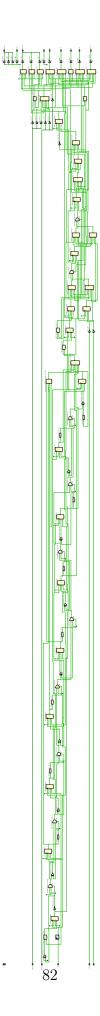

| 35. | Circuito de pruebas con Snapshot Scan                                            | 41 |

|-----|----------------------------------------------------------------------------------|----|

| 36. | Circuito de pruebas post-synthesis con Snapshot Scan                             | 42 |

| 37. | Simulación de circuito de pruebas en FPGA                                        | 43 |

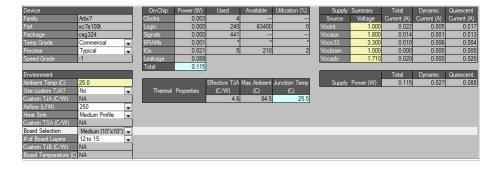

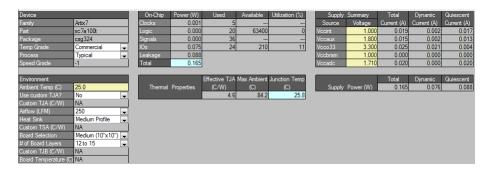

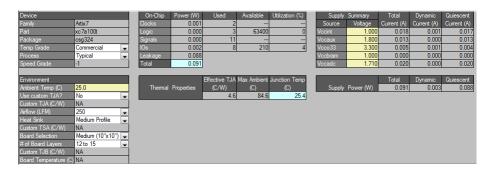

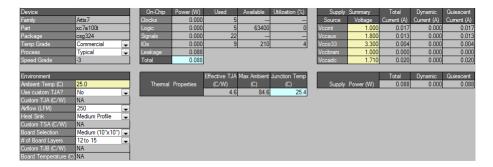

| 38. | Consumo de potencia de circuito de pruebas en FPGA                               | 44 |

| 39. | Simulación de circuito de pruebas al incorporar Chipscope                        | 44 |

| 40. | Señales de salidas de flip-flops de circuito de pruebas al incorporar Chipscope. | 45 |

| 41. | Consumo de potencia de circuito de pruebas al incorporar Chipscope               | 45 |

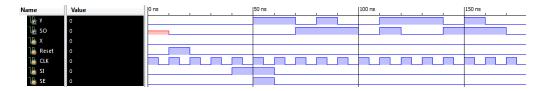

| 42. | Simulacion de circuito de control para Scan Design                               | 46 |

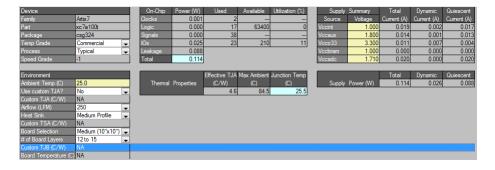

| 43. | Consumo de potencia de circuito de control para Scan Design                      | 46 |

| 44. | Diagrama de señales para circuito de control de Enhanced Scan. Tomado de 2       | 47 |

| 45. | Consumo de potencia de circuito de control para Enhanced Scan                    | 48 |

| 46. | Diagrama de tiempos de señales de control para Snapshot Scan                     | 49 |

| 47. | Consumo de potencia de circuito de control para Snapshot Scan                    | 50 |

| 48. | Simulación de circuito de pruebas con Scan Design                                | 50 |

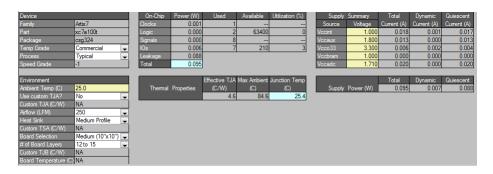

| 49. | Consumo de circuito de pruebas con Scan Design                                   | 51 |

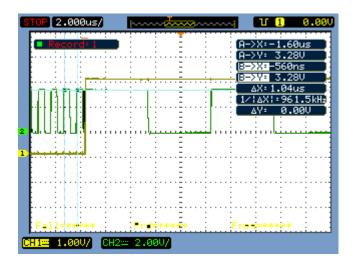

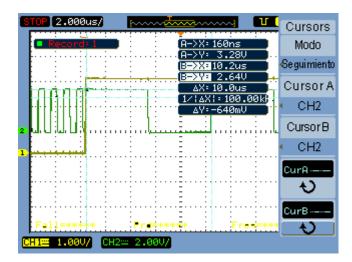

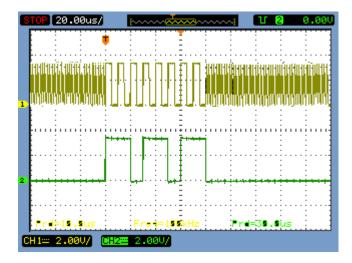

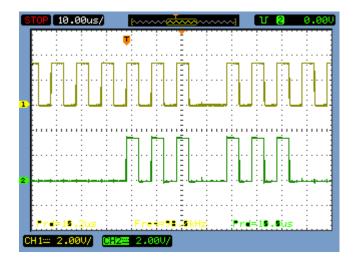

| 50. | Señal de reloj 1MHz para circuito con Scan Design                                | 52 |

| 51. | Señal de reloj 100 KHz para circuito con Scan Design                             | 52 |

| 52. | Señal EN_S y SE en circuito con Scan Design                                      | 53 |

| 53. | Señal EN_S y SI en circuito con Scan Design                                      | 53 |

| 54. | Señal CLK y SO en circuito con Scan Design                                       | 54 |

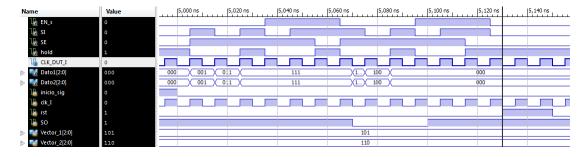

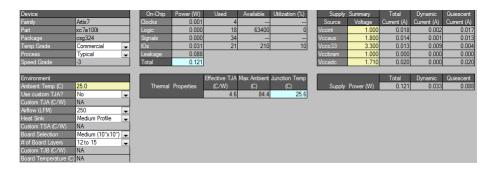

| 55. | Simulacion de circuito de pruebas con Enhanced Scan                              | 54 |

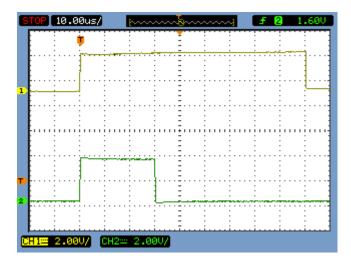

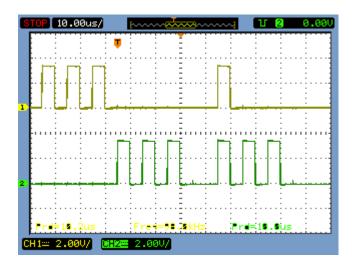

| 56. | Consumo de circuito de pruebas con Enhanced Scan                                 | 55 |

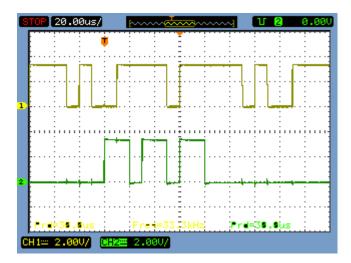

| 57. | Señal de reloj de 100KHz para circuito con Enhanced Scan                         | 56 |

| 58. | Señal de HOLD para circuito con Enhanced Scan                                    | 56 |

| 59. | Señal de SI para circuito con Enhanced Scan                                      | 57 |

| 60. | Señal de SO para circuito con Enhanced Scan                                      | 57 |

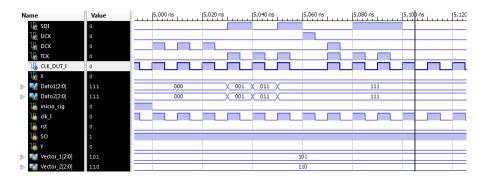

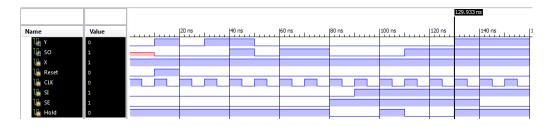

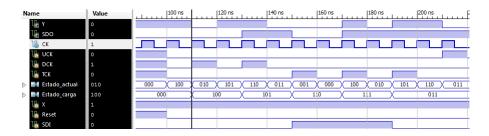

| 61. | Señales en el tiempo de circuito de pruebas con Snapshot Scan                    | 58 |

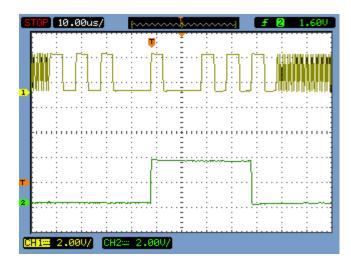

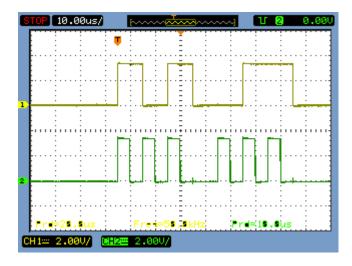

| 62. | Consumo de potencia y recursos de circuito de pruebas con Snapshot Scan          | 59 |

| 63. | Señal de reloj del DUT con Snapshot Scan                                         | 59 |

| 64. | Señal DCK del DUT con Snapshot Scan                                              | 60 |

| 65. | Señal UCK del DUT con Snapshot Scan                                              | 61 |

| 66. | Señal SI del DUT con Snapshot Scan                                               | 61 |

| 67. | Señal SO del DUT con Snapshot Scan                                               | 62 |

# Índice de cuadros

| 1.  | Distribución de I/O para circuito de control para Scan Design                      | 30 |

|-----|------------------------------------------------------------------------------------|----|

| 2.  | Distribución de I/O para circuito de control para Enhanced Scan                    | 33 |

| 3.  | Distribución de I/O para circuito de control para Snapshot Scan                    | 36 |

| 4.  | Distribución de I/O para circuito rediseñado con Scan Design                       | 36 |

| 5.  | Distribución de I/O para circuito rediseñado con Enhanced Scan                     | 40 |

| 6.  | Distribución de I/O para circuito rediseñado con Snapshot Scan $\ .\ .\ .\ .\ .$ . | 42 |

| 7.  | Consumo de potencia de circuitos de prueba rediseñados                             | 64 |

| 8.  | Recursos de FPGA utilizados por circuitos de prueba rediseñados                    | 65 |

| 9.  | Consumo de potencia de circuitos de control diseñados                              | 66 |

| 10. | Recursos de FPGA utilizados por circuitos de control diseñados                     | 67 |

# Capítulo 1

# Introducción

A continuación, se brinda una breve descripción de importantes aspectos generales, necesarios para comprender el origen del proyecto. Aspectos como el donde se desarrolla, la problemática que lo rodea, así como su motivación e importancia en el desarrollo de circuitos digitales utilizados en la industria actualmente, son tocados durante el desarrollo del presente documento.

#### 1.1. Entorno

El Instituto Tecnológico de Costa Rica es una institución nacional de educación superior universitaria, dedicada a la docencia, la investigación y la extensión de la tecnología. Por medio de la escuela de Ingeniería en Electrónica y con ayuda de varios de sus estudiantes y profesores está desarrollando un microprocesador de propósito general para su implementación en un dispositivo médico implantable.

Un microprocesador es un tipo de circuito integrado (chips) complejo constituido por componentes extremadamente pequeños, formados en una única pieza plana de poco espesor de un material semiconductor. Es un circuito electrónico que actúa como unidad central de proceso de un ordenador, es decir, es el componente dentro de un ordenador que interpreta las instrucciones de un programa informático.

El circuito logra esa interpretación mediante la realización de operaciones básicas aritméticas, lógicas y de entrada/salida del sistema obteniendo así el control de las operaciones de cálculo, a las cuales no se tiene un fácil acceso. Este tipo de circuitos digitales se pueden encontrar no solo en computadoras, si no también en otros dispositivos programables, como por ejemplo impresoras, automóviles, aviones e incluso dispositivos médicos.

En el área médica se han desarrollado microprocesadores que cumplen tareas específicas, como por ejemplo, algunos son capaces de almacenar la información del ADN de las personas, esto para poder determinar cómo reaccionará el organismo ante ciertos fármacos; así como algunos que pueden convertir la luz en señales eléctricas y así poder enviar información al

cerebro de una persona ciega.

Este tipo de dispositivos médicos consisten en artefactos que son introducidos de manera parcial o total en el cuerpo humano por medio de una intervención quirúrgica, y que permanecen allí luego del procedimiento para mejorar o monitorear la salud del paciente.

El microprocesador que se encuentra en desarrollo tendrá ciertas características físicas y operacionales que lo harán útil para cualquier aplicación en la medicina. Características como un bajo consumo de energía, gran velocidad de procesamiento, capacidad de ejecución de pocas instrucciones y ser físicamente pequeño, son parte de las características deseadas.

Sin embargo, para lograr ese tipo de características estos chips deben ser sometidos, una vez manufacturados, a diferentes pruebas complejas para comprobar en un corto tiempo que su funcionamiento sea el esperado según lo que el cliente solicita, en este caso, el Instituto Tecnológico de Costa Rica; además, deben hallarse la mayor cantidad de errores en el funcionamiento de componentes internos causados por su manufactura, de igual manera en un período corto.

Tomando en cuenta lo anterior, es necesario encontrar una manera de disminuir la complejidad y el tiempo que tomará realizar las diferentes pruebas al circuito que se encuentra en desarrollo, una vez se construya físicamente.

Muchas tareas complicadas e importantes, e incluso la vida de los pacientes en el caso de los dispositivos implantables, dependen enormemente de los microprocesadores, es por ello que debe asegurarse que los errores que pueden aparecer después de su fabricación sean menores, para así no comprometer su funcionamiento y asegurar la seguridad del paciente o portador final.

#### 1.2. Desarrollo del problema

Durante la manufactura de microprocesadores existen varias etapas de prueba muy importantes; una de las finales es en la que se verifica que el producto después de su manufacturación continúe cumpliendo con los requerimientos solicitados por un cliente y además con sus funcionalidades esperadas.

Un reto para los desarrolladores, y en la que se enfocará este proyecto, es el diseño de circuitos a partir de diferentes técnicas en DFT (Design For Testabilty) que puedan cumplir con los requerimientos de diseño y brindar un camino más sencillo para la realización de pruebas. Esas técnicas de diseño son utilizadas para poder simplificar las pruebas, la depuración y las tareas de diagnóstico en la evaluación del rendimiento y funcionalidad de un circuito digital manufacturado; además de mejorar la calidad y reducir el costo de esas pruebas.

Además es necesaria la estimulación de las diferentes señales internas asociadas a los componentes del circuito en desarrollo para poder realizar las pruebas, el lograr esto sin contar con una estrategia consume mucho tiempo y dinero para una empresa que se dedique a ello, e incluso, en el caso del Instituto Tecnológico de Costa Rica y el desarrollo de su microprocesador.

Las diferentes técnicas de DFT que se estudiarán en el presente proyecto, pueden ser aplicadas a un circuito digital para conseguir, como se menciona en [2], un diseño listo para escaneo (Scan Design), y cumplir los objetivos mencionados anteriormente. Por ello es necesario la evaluación y comparación entre ellas para poder seleccionar las más eficientes para ser aplicadas en el circuito digital que se encuentra en desarrollo. Siempre tratando de reducir el tiempo de ejecución y mejorar precisión de los resultados de las pruebas post manufactura.

# Capítulo 2

# Propuesta de solución

## 2.1. Enfoque de solución

Una manera de lograr la reducción de fallas es mejorar la testabilidad de los circuitos digitales; la testabilidad describe las caracteristicas de controlabilidad y observabilidad de un dispositivo. La controlabilidad indica la dificultad de poder establecer un estado lógico a una señal interna por medio de los pines de entrada físicos del circuito digital bajo prueba, y por otro lado la observabilidad indica la dificultad de mostrar o propagar el valor lógico de una señal de salida interna hacia los pines físicos de salida.

Las técnicas de diseño de circuitos integrados brindadas por DFT (Design for Testability) agregan características de testabilidad a el diseño de un producto. Se plantea el estudio, evaluación y aplicación de 3 diferentes técnicas de DFT que se enfocan en el diseño para escaneo, para así poder crear un circuito digital capaz de brindar las facilidades y beneficios en la etapa de pruebas post manufactura de un circuito digital, además con estas técnicas, en su aplicación industrial, se pretenden identificar y corregir violaciones a reglas de diseño.

De manera un poco más detallada, en este proyecto, el objetivo principal es rediseñar una serie de circuitos digitales dependiendo de la técnica de DFT implementada. Estos circuitos serán útiles para tomarlos como ejemplo de implementación de las técnicas de DFT para la realización de pruebas tanto de rendimiento como de operación de un microprocesador de propósito general que se encuentra en desarrollo, el cual puede ser programado en una FPGA.

Lo anterior se logrará por medio de la evaluación, comparación e implementación de las técnicas de DFT de propósito específico que se listan más adelante, en el diseño de un circuito digital de propósito general. Dichas técnicas serán comprobadas con ayuda de dicho circuito y una FPGA.

- Scan Design Básico

- Escaneo mejorado (Enhanced Scan).

• Escaneo instantáneo (Snapshot Scan).

Estas tres técnicas son utilizadas para realizar pruebas de retardo y depuración del sistema. Cada una con diferentes características de implementación y operación. Inicialmente se planea aplicar individualmente las diferentes técnicas de DFT en el diseño de circuito digitales con los que se pueda extraer información de rendimiento y operación, como por ejemplo compuertas lógicas o máquinas de estados simples.

A partir de los resultados adquiridos por el paso mencionado anteriormente, se planteará teóricamente la implementación de las técnicas de DFT bajo estudio en un microprocesador de código abierto; se dice teóricamente ya que la utilización de estas técnicas de diseño implica un trabajo que tomaría mucho tiempo si no se cuenta con información de operación del mismo. Al no contar con datos esperados a nivel interno, la realización de pruebas y la comparación de resultados es muy difícil de lograr. Por ello, y por el tiempo con el que se cuenta para poder desarrollar el proyecto, se utilizará un circuito digital de propósito general para comprobar en una FPGA el funcionamiento de los circuitos rediseñados con las técnicas de DFT.

## 2.2. Hipótesis

Mediante el uso de las técnicas de DFT se crean circuitos similares al sistema original, con la diferencia que estos circuitos son capaces de extraer estados lógicos de las señales internas de los diferentes componentes que conforman el sistema. Información como tiempos de retardo, y la generación de protección ante errores leves son algunas características y mejoras que se obtienen con su aplicación.

Estos circuitos adicionales son accedidos por medio de la configuración de las entradas físicas del sistema para así forzar un estado de prueba, en el cual se extrae información tanto de la lógica secuencial como de la lógica combinacional de los componentes, y con ello de ser necesario rediseñar los componentes que fallen o el sistema en su totalidad.

# Capítulo 3

# Meta y Objetivos

#### 3.1. Meta

La realización de pruebas post manufactura del microprocesador que se encuentra en desarrollo en el Instituto Tecnológico de Costa Rica, utilizando las técnicas de DFT estudiadas.

Indicador: Adquisición de datos internos del microprocesador por medio de un pin físico.

# 3.2. Objetivo general

Rediseñar un sistema digital de propósito general que implementen las técnicas de DFT bajo estudio.

Indicador: Simulación de los sistemas creados y comprobación de su funcionamiento en una FPGA.

# 3.3. Objetivos específicos

• Rediseñar un circuito que implemente la técnica de Scan Design en un sistema digital de propósito general.

Indicador: Simulación del circuito diseñado en el software Xilinx/Modelsim y su implementación en una FPGA.

• Rediseñar un circuito que implemente la técnica de escaneo mejorado (Enhanced scan) a un sistema digital de propósito general.

Indicador: Simulación del circuito que aplica el Escaneo Mejorado en el software Xilinx/Modelsim para realizar su implementación en una FPGA.

• Rediseñar un circuito que implemente la técnica de escaneo instantáneo (Snapshot Scan) aplicado a un sistema digital de propósito general.

Indicador: Simulación del circuito que aplica el escaneo instantáneo en el software Xilinx/Modelsim y su implementación en una FPGA.

# Capítulo 4

# Marco Teórico

#### 4.1. DUT

Siglas de "Device Under Test", es un acrónimo que se utiliza para hacer referencia al dispositivo al que se le está realizando una prueba.

## 4.2. Design For Testability (DFT)

El DFT, o como se le puede llamar en español, Diseño para "Testabilidad", consiste en el uso de diferentes técnicas y reglas de diseño de circuitos digitales, las cuales son utilizadas para mejorar la calidad y reducir el costo de las pruebas realizadas a los propios circuitos digitales, tal y como se indica en [1] (Wang, L., Wu, C. and Wen, X. 2006).

Este tipo de diseño es utilizado para detectar violaciones a las reglas de DFT utilizadas para crear circuitos que puedan ser "testeables". Al hacer caso omiso a esas reglas de diseño, será más complicado y costoso la creación de las pruebas para ese circuito.

Parte de las complicaciones a las que se enfrentaban años atrás los diseñadores era la gran dificultad de crear patrones de prueba que fueran capaces de estimular y extraer señales internas de los dispositivos de almacenamiento, las cuales implicaban a su vez un alto costo de desarrollo de pruebas y una pérdida de calidad en los dispositivos producidos. Esto generó la necesidad de combinar el diseño de un circuito digital, junto al diseño de sus pruebas, (Wang et al.,2006).

Una característica primordial de este tipo de diseño es que se busca mejorar la "testabilidad" (Testability) de un circuito, esto quiere decir que se busca mejorar la controlabilidad, que indica que tan fácilmente se puede cambiar el estado lógico de una señal interna por medio de un pin físico, así como la observabilidad, la cual busca aumentar la facilidad con la que es posible el observar el estado lógico de una señal interna por medio de un pin físico.

El mejoramiento de la controlabilidad y observabilidad se logra, como se menciona anteriormente, por medio del rediseño del circuito original, sustituyendo los elementos de almacenamiento de interés por su equivalente con ciertas modificaciones; entre otros aspectos de rediseño a considerar de los que se hablará más adelante para alcanzar ese objetivo.

Las técnicas de DFT se aplican tanto para circuitos combinacionales como para secuenciales, donde en estos últimos, es más complicado la aplicación de las técnicas de rediseño y la realización de las pruebas, y años atrás, muy complicado el alcanzar una buena zona de cobertura de señales. Sin embargo, gracias a la investigación y desarrollo que se ha dado durante el surgimiento de nuevas tecnologías la dificultad de realizar pruebas y obtener información de los circuitos secuenciales, se ha podido reducir a temas puramente combinacionales.

#### 4.3. Scan Cells

Las Scan Cells, o celdas de escaneo, son elementos de almacenamiento modificados, los cuales son de gran ayuda para poder acceder de una manera más sencilla a los datos que almacenan. Generalmente el poder tener acceso a los datos almacenados sin el uso de estas celdas resulta en una tarea muy complicada, ya que se requiere utilizar muchos recursos del circuito bajo prueba para poder establecer valores definidos en las diferentes rutas de datos.

Existen diferentes tipos de estrucuturas de DFT utilizadas en la industria:

- Muxed-D Scan Cell

- Clocked-Scan Cell

- LSSD Scan Cell

Típicamente las celdas más utilizadas y las que se van a tratar en este proyecto, son las Muxed-D, las cuales se basan en la conexión de un multiplexor en la entrada de un flip-flop tipo D, para formar un conjunto llamado Scan Flip-Flop (SFF) [2] (Bushnell, M., Agrawal, V. D., 2000).

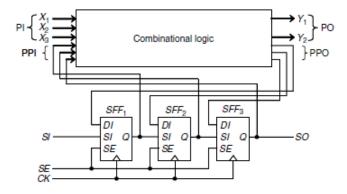

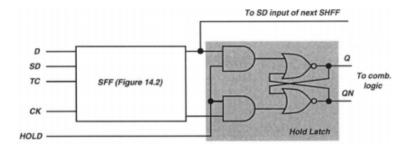

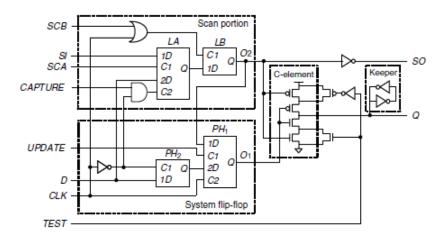

Figura 1: Celda de escaneo. Tomado de [1]

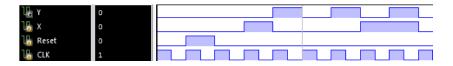

Como se puede apreciar en la figura 1 estas celdas están compuestas por 3 entradas y una salida, así como una señal de reloj. Dos de esas entradas se utilizan para ingresar los datos a manipular; generalmente en la entrada 0 del multiplexor se conecta la fuente de la señal regular del circuito (DI, Data Input), y en la entrada 1 se conecta la fuente de la señal que se desea insertar (SI, Scan Input), es decir, la señal de prueba. La tercer entrada de esta celda se trata de la señal de control del multiplexor (SE, Scan Enable), la cual se encarga de

cambiar la fuente de datos. Cuando SE está en estado bajo y se aplica una señal de reloj, el flip-flop almacenará el dato actual de la ruta de datos normal. Caso contrario se almacenará el dato de prueba que se encuentre en SI.

Una de las ventajas, y a la vez desventaja, del uso de este tipo de celdas es que el área que comprende el circuito no se incrementa demasiado debido al uso del multiplexor. Sin embargo, su uso incrementa sustancialmente la controlabilidad del circuito bajo prueba. La mayor desventaja es que se agrega un retardo de un multiplexor a la operación regular del circuito.

#### 4.4. Scan Chain

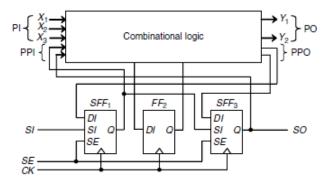

Se refiere a la conexión en serie de varias celdas de escaneo (Scan Cells); cuando se realiza una o varias cadenas de este tipo es posible el ingreso y extracción de datos simplemente por medio de 2 pines físicos. En la figura 2 se puede ver la conexión y formación de este tipo de cadenas.

Figura 2: Cadena de escaneo (Scan Chain).

La construcción de estas cadenas es bastante simple, basta con interconectar todas las señales de control SE y ubicar correctamente las entradas DI de los Scan Flip-Flop en sus puntos originales dentro de la lógica combinacional, así como conectar la señal de salida de un SFF a la entrada 2 del siguiente SFF para poder utilizar este recurso tan útil. (Wang et al.,2006).

El funcionamiento de las celdas se conserva, simplemente al formar una cadena se logra obtener un registro de corrimiento que utilizará la entrada SI de la primer celda de escaneo para ingresar datos, y la salida SO de la última celda de escaneo para extraer los bits que se encuentran almacenados en los SFF. Pueden existir varias cadenas de celdas, dependiendo de la disponibilidad de pines físicos así como de la cantidad y ubicación de los datos que se requieren.

#### 4.5. Ruta Crítica

Se le conoce como ruta crítica a la ruta por la que se puede dar un flujo de datos que pasan por la mayor cantidad de elementos combinacionales de un circuito digital (Wang et al.,2006), lo que implicaría que es la ruta con el mayor retardo combinacional. En la figura 3 se puede ver un ejemplo de lo mencionado anteriormente.

Figura 3: Ejemplo de ruta crítica de un circuito combinacional.

Un aspecto importante en este tema es que siempre existen retardos entre la estimulación de la entrada de un elemento y su salida, además de la oscilación de estados lógicos mientras se distribuye la información por el elemento a la que se le llama trasiente; lo que se busca con la ruta crítica es encontrar los componentes que generen un retardo tan grande en la ruta de datos, que la respuesta del circuito final en sus salidas se prolongue por mucho tiempo. Durante el diseño y fabricación de dispositivos siempre se trata que el retardo de la respuesta de las salidas no sea mayor a un ciclo de reloj de operación del elemento a desarrollar (Wang et al.,2006).

#### 4.6. Vectores de Prueba

Los vectores de prueba son la combinación de los bits que serán utilizados para forzar un estado del DUT; este grupo de bits incluye las entradas primarias, físicas, del DUT llamadas PI (Primary Input) y las entradas pseudo-primarias llamadas PPI (Pseudo-Primary Inputs), estas últimas se refiere a los puntos en los cuales se conectan las salidas de los SFF que a su vez se dirigen hacia la entrada de la lógica combinacional del circuito bajo prueba.

Aunque no forman parte del vector de prueba, cabe mencionar que a las salidas físicas del DUT se les conoce como PO (Primary Output), y a las salidas internas de la lógica combinacional del DUT como PPO (Pseudo Primary Outputs); estas señales forman parte primordial de la prueba a realizar, ya que generalmente forman parte de los resultados de interés y por ende parte de los datos que se almacenan para poder determinar el correcto funcionamiento del circuito.

Estos vectores son ingresados de forma serial a los SFF, tal y como se mencionó anteriormente en el apartado de "Scan Cells", es decir, se agrega uno a uno los bits que lo componen, lo que implica que el tiempo de prueba depende directamente de la cantidad de SFF que forman la cadena o las cadenas con las que se cuente.

## 4.7. Scan Design

Scan Design según [2] (Bushnell, M., Agrawal, V. D., 2000), se refiere a la metodología estructurada de DFT más utilizada en el diseño de circuitos digitales, la cual logra mejorar la controlabilidad y observabilidad de elementos secuenciales dentro de un dispositivo. La sustitución de elementos de almacenamiento por SFF equivalentes y la adición de señales de control es parte de las herramientas utilizadas en este proyecto para poner al dispositivo en diferentes modos de operación según se requiere.

Los modos de operación son el modo normal, modo registro y modo de captura; después de rediseñar el circuito, durante el modo normal la operación del circuito es la misma que la alcanzada con el diseño original, es decir, el dispositivo no tomará en cuenta las señales de control generadas por el circuito de control usado durante pruebas. El modo de registro es el primer modo utilizado al ingresar los bits por medio de la entrada SI, consiste en indicarle al DUT que permita el paso de los datos ingresados por SI y a su vez extraiga los resultados del ingreso del vector previo por medio de la salida SO. El modo de captura utiliza las mismas señales de control que el modo registro, con la diferencia conceptual que durante el modo captura, se toman los datos de la salida SO y se almacena en un registro con latches para su posterior revisión.

Dependiendo de la cantidad de elementos de memoria de los que se desea obtener información, existen diferentes estructuras que serán de utilidad. Entre ellas existen las siguientes:

#### Full-scan design (Diseño para Escaneo Completo)

En este tipo de arquitectura, todos los elementos de almacenamiento son sustituidos por SFF para poder formar las cadenas de SFF (Wang et al.,2006), así se logra tener con certeza el estado lógico de todos los datos internos, sin embargo, hay que tomar en cuenta que dependiendo de las dimensiones del área máxima que se pueda utilizar en el desarrollo del dispositivo, puede ser conveniente o no el utilizar esta arquitectura, ya que, si se cuenta con poco espacio no debe utilizarse. A pesar de esto, esta arquitectura es la más utilizada en la actualidad debido a la facilidad de uso y beneficios en cuanto adquisición de datos.

Figura 4: Ejemplo de circuito secuencial. Tomado de [2]

Figura 5: Ejemplo de circuito secuencial con SFF. Tomado de [2]

Observando las figuras 10 y 11 se puede comprobar como todos los elementos de almacenamiento de la figura 10 son sustituidos por las celdas de escaneo, brindando así la oportunidad de conseguir información de cada uno.

#### Partial-Scan Design(Diseño para Escaneo Parcial)

A diferencia del Full-Scan Design, esta arquitectura solamente sustituye una parte de los elementos de memoria (Wang et al.,2006), un obstáculo que se encuentra en el uso de este tipo de estructura es la complejidad que adquiere la generación de los vectores de prueba, ya que será necesario establecer un mayor número de combinaciones de las entradas de los SFF disponibles para poder establecer un estado deseado en los flip-flop que no se encuentren dentro de la cadena de celdas.

Figura 6: Ejemplo de Partial-Scan design. Tomado de [2]

Al no incluir todos los elementos de almacenamiento en la cadena existe una complejidad mucho mayor en el control de los mismos, ya que va a ser necesario controlarlos con señales de reloj diferentes y por ende una mayor cantidad de lineas de conexion y área que ocuparían los elementos en general del DUT.

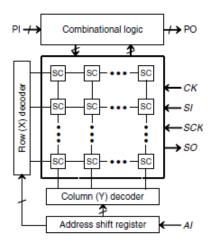

#### • Random-Access Scan Design

Este tipo especial de diseño tiene una mayor complejidad, ya que, a diferencia de las 2 arquitecturas anteriores esta arquitectura le asigna una dirección a cada SFF, por lo que, no existirán los problemas de consumo de potencia, calentamiento, fallas del circuito, etc, debido al acceso desproporcionado al circuito.

Dentro de sus desvantajas se encuentra el alto calentamiento en los componentes debido a la implementación del acceso aleatorio que se debe desarrollar, entre ellos las señales de reloj, SI, SO y demás dependiendo de las cadenas que se deseen activar según la dirección de registro que se envíe desde el circuito de control. (Bushnell, M., Agrawal, V. D., 2000)

Figura 7: Ejemplo de Random-Access-Scan design. Tomado de [2]

Sin embargo, de igual manera que en las anteriores, esta arquitectura afecta los valores de las señales de otras celdas cuando están dentro de la misma cadena.

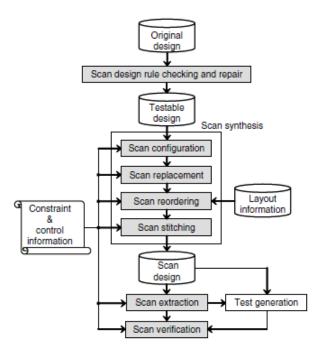

## 4.8. Diagrama de Flujo para Scan Design

Esta sección se incluye para brindar información extra sobre el DFT y Scan design.

A pesar de que no es posible ni viable implementar este diagrama de flujo en el presente proyecto, ya que no se cuenta con la disponibilidad de equipo, el recurso humano que implica ni el tiempo disponible, es importante tener presente que detrás del simple concepto de rediseño de un circuito, existe una larga lista de pasos y requerimientos que implementar en el momento de utilizar este tipo de diseño.

A continuación se presenta el diagrama de flujo utilizado durante la implementación del scan design, el mismo se resume de (Wang et al.,2006).

Figura 8: Diagrama de flujo para implementar el scan design. Tomado de [2]

De la figura 8 se pueden introducir las siguientes secciones:

• Scan design rule checking and repair: Identificar y reparar todas las violaciones al scan design para convertir el diseño original en un diseño testeable.

Reglas de Scan Design necesarias:

- Buses tristate

- Puertos bidireccionales

- Gated clocks (muxed D full scan)

- Clocks derivados /muxed D full scan)

- Realimentaciones combinacionales

- Señales de Set/Reset asíncronas

- Señales de reloj que transportan datos

- Buses flotantes

- Entradas flotantes

- Compuertas NAND-NOR cruzadas-emparejadas

- Elementos de almacenamiento no usados en el scan

- Scan síntesis: Una vez que se han realizado todas las reparaciones del circuito original. Es en este punto donde se convierte el circuito testeable a un diseño escaneable sin afectar el funcionamiento del circuito original. Se utilizan herramientas de análisis estático y verificadores de equivalencia para comprobar que la operación de los 2 circuitos sea la misma.

- Configuración de scan: Primer paso en la formación en la cadena de escaneo. Aquí se toma la decisión de el número de cadenas, el tipo de scan cell a utilizar, los elementos de almacenamiento a incluir en las cadenas y la manera en la que se ordenarán las scan cell.

- Sustitución de scan: Aquí se sustituyen todos los FF por los SFF. Al nuevo circuito se le conoce como scan-ready design.

- Reordenamiento de scan: Se refiere al reordenamiento de las scan cells en las cadenas de escaneo, dependiendo de su ubicación física, esto para minimizar las interconexiones.

- Union de puntos de scan: En este paso se unen las scan cells para formar la cadena. El proceso se refiere a la unión de la salida de los SFF a la entrada del siguiente SFF, así como la conexión de la entrada física con el SI del primer SFF, al igual que la conexión de la salida física con el SO del último SFF.

- Extracción de scan: Aquí se verifica la integridad de las cadenas de escaneo. En él se extraen todas las instancias de todas las cadenas, se logra trazando el diseño para cada cadena para verificar que todas las conexiones están intactas cuando el diseño entre en shift mode.

- Verificación de scan: Esta se realiza cuando ya se ha implementado físicamente el diseño, es decir, ya cuando se ha manufacturado el dispositivo, es por ello que se genera un archivo de tiempo llamado Standard Delay Format (SDF), ese archivo construye el comportamiento en el tiempo del dispositivo manufacturado, necesario para poder realizar las pruebas.

- Verificación de la operación de ingreso de vectores.

- Verificación de la operación de captura.

- Costo del Scan Design: La implementación del diseño implica sobrecalentamiento de un área, costo de pines de I/O, disminución de rendimiento y esfuerzo del circuito. Sin embargo, los beneficios son el incremento de la testabilidad, bajo costo de desarrollo y la reducción del tiempo de diagnóstico y análisis de fallas.

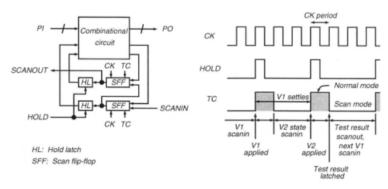

## 4.9. Scan Hold Flip Flop

El SHFF (Scan Hold Flip flop) es un tipo de celda de escaneo a la cual se le adiciona en la salida un latch, el cual lo convierte en un componente importante en el análisis de retardos de circuitos combinacionales y secuenciales; este latch es útil para aislar la parte de extraccion de datos del resto del circuito, y con ello el problema de análisis de retardos se convierte en un problema combinacional, ya que solo se debe manipular una señal no secuencial para poder cumplir con el objetivo.

Figura 9: Esquema de un SHFF. Tomado de [1]

De la figura 9 se puede notar que mientras la señal HOLD se mantenga en estado bajo, no se permitira la actualizacion de datos en las PPI, una vez se active esa señal, el latch será transparente para el resto del circuito, por lo que dejará pasar las señales a través de él.

El modo normal se selecciona con HOLD=1, en modo de escaneo TC=1 y HOLD=0. Con este procedimiento se puede separar la parte combinacional de la actividad de escaneo.

Una vez que se ingresa el vector V1 de prueba para el circuito, se debe aplicar un cambio de HOLD de 0 a 1 para ingresar los nuevos valores a la lógica combinacional.

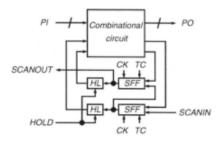

#### 4.10. Enhanced Scan

Este tipo de diseño es muy similar al Scan Design basico, el principio y objetivo de funcionamiento es el mismo, su nombre se adjudica debido a la adicion de un latch en la salida de los SFF, es decir, a la utilizacion de un SHFF.

Figura 10: Esquema de un circuito con Enhanced Scan. Tomado de [1]

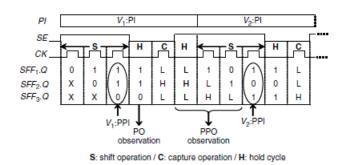

Figura 11: Diagrama de señales de un circuito con Enhanced Scan. Tomado de [1]

Como se puede ver en la figura 10, la adicion del latch se encuentra entre la conexion de las salidas de los SFF y las entradas de la logica combinacional (PPI). En la figura 11 se puede apreciar el diagrama temporal de señales necesario para poder llevar a cabo las pruebas, y obtener el resultado de las mismas.

Inicialmente se introduce por medio de los SFF el primer vector de prueba, una vez finalizado esto, se procede a cargar el vector a la logica combinacional estableciendo en 1 la señal TC y HOLD, despues de realizar esto se procede a ingresar el segundo vector de pruebas, de la misma manera se manipulan las señales TC y HOLD para cargar el vector en el DUT; finalmente mientras se carga el siguiente vector 1 de pruebas se extraen los resultados del vector 2 de la prueba anterior.

La desventaja de esta tecnica con respecto al Scan Design basico es el calentamiento y retrasos en respuesta de la señal debido al uso constante del latch. Ademas, el tamaño de los FF se incrementa hasta un 30 % al utilizar los SHFF, y el uso de una señal extra también

implica una reducción del espacio de trabajo para la ubicación de otros componentes debido al enrutamiento de la señal de H hacia todos los FF, o viéndolo de otra manera implica que el área y tamaño del dispositivo sea mayor.

Una ventaja con respecto al Scan Design basico es la utilizacion de cualquier par de vectores, no es necesario que solamente 1 bit del total que componen a los vectores sea diferente.

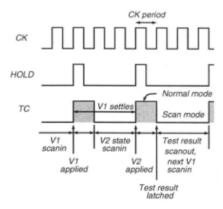

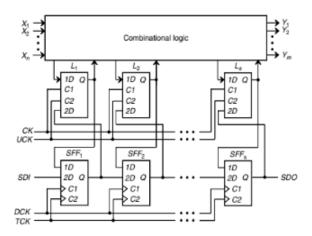

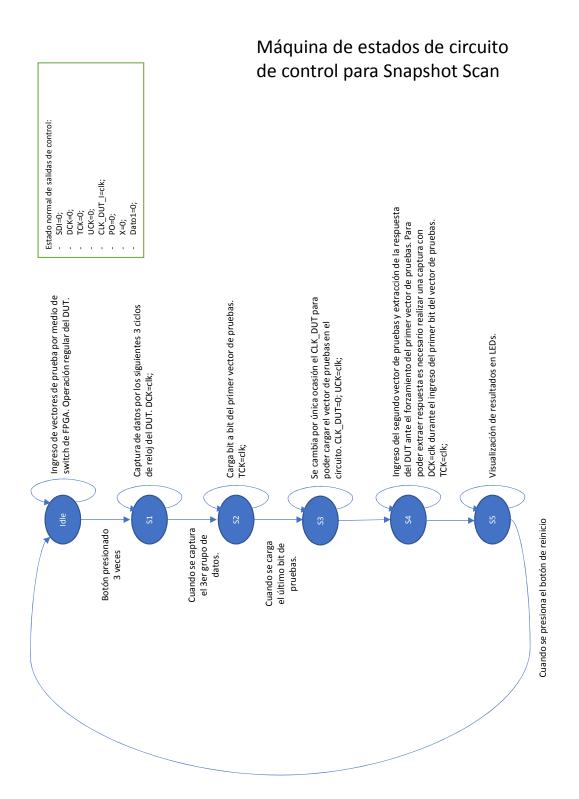

## 4.11. Snapshot Scan

Figura 12: Diagrama de señales de un circuito con Snapshot Scan. Tomado de [1]

Con el circuito diseñado a partir de esta técnica es posible conocer los estados de señales internas de elementos de almacenamiento en cualquier momento sin necesidad de interrumpir la operación funcional del circuito.

Para lograr esto es necesario agregar un SFF especial por cada elemento de almacenamiento de interés, y se conectan esos SFF en cadena para poder extraer la información del estado de ese elemento. Ademas, se colocan latches de 2 entradas entre las lineas que se encuentran entre los PPO de la logica combinacional y las entradas de los elementos de almacenamiento.

Se dice que se utilizan SFF especiales ya que cuentan con 2 señales de reloj, con lo que dependiendo de cual se encuentre en estado alto, el dato de entrada del pin correspondiente sera transmitido a la salida.

Los latches son utilizados para poder cargar en la lógica combinacional en cualquier momento los datos que se encuentran en las salidas de los SFF, esto durante la ejecucion de las pruebas; como se menciona anteriormente no es necesario inducir un estado de prueba en el circuito para lograr extraer la información de interés ya que con simplemente inducir un estado alto en la señal de reloj 1 del SFF se pueden cargar los datos previos a la llegada del flanco positivo de la señal de reloj.

Detallando un poco más, y utilizando como referencia la figura 12, se puede introducir y extraer datos por medio de los SFF y las señales de SDI y SDO utilizando la señal de TCK. Así como los datos pueden ser transferidos a los Latch del sistema (L1, Lx) en paralelo a través de su entradas 2D utilizando UCK. Los datos del sistema pueden ser cargados a los SFF por medio de la entrada 1D y utilizando DCK. El circuito puede operar en modo normal utilizando CK para capturar los valores de la lógica combinacional en los FF del sistema (Lx).

Lo interesante de esta técnica es cuando se capturan los datos que se encuentran en los FF del sistema, en el los SFF, esto se puede realizar en cualquier momento cuando DCK es aplicado. Seguidamente los datos pueden ser extraídos por medio de SDO.

Una característica de esta técnica es que puede cambiar datos de prueba a los FF del sistema para facilitar el diagnóstico y análisis de fallas cuando se aplica UCK. Su aplicación implica una gran mejora a la observabilidad de nodos que no son de almacenamiento. El mayor problema del uso es el gran aumento de sobrecalentamiento en un área específica del circuito debido al gran cambio de componentes, esto según se comenta en (Wang et al.,2006). Es de esta técnica que se desarrolló la arquitectura llamada LSSD, utilizada frecuentemente en la actualidad.

#### 4.12. Error-Resilient Scan

A pesar que en este proyecto no se va a desarrollar, se va a comentar su funcionamiento mas no es posible comprobarlo debido a su fuerte necesidad de contar con el dispositivo post manufactura para poder determinar la mejora en el diseño, además, del tipo de pruebas físicas a las que debería someterse.

Figura 13: Esquema de celda utilizada para Error-Resliente Scan. Tomado de [1]

Para iniciar hay que introducir el concepto de errores suaves o Soft Errors, los cuales son distorsiones de flancos de las señales internas causadas por diferentes tipos de radiación, como por ejemplo la radiación cósmica que afecta internamente a las memorias e incluso las particulas alpha que se pueden desprender del encapsulado de un chip. Estos problemas comienzan a tomar más importancia en la actualidad debido a la implementación de la tecnología en el rango de los nanometros y la alta frecuencia de operación.

El desarrollo de esta técnica se da debido al deseo de brindar protección a los chips de posibles cambios repentinos en los datos almacenados o de la deformación del trasiente en las entradas de la lógica combinacional del circuito. La mayoría de los errores en la manufactura de un dispositivo se da en la lógica combinacional y los elementos de almacenamiento, con un 60 por cien de los casos; por otro lado, en un 40 por cien de los errores se da en las memorias, (Wang et al.,2006).

Existen 2 modos de operación de este tipo de celda:

• Operacion normal: Durante esta operacion, siempre y cuando se mantenga la señal TEST en cero el elemento C funcionará como un comparador entre las señales de la porción de escaneo y el sistema de flip-flop y retendrá su estado anterior hasta que esas 2 señales sean iguales.

Para poder evitar lo anterior, es necesario mantener en cero las señales SCA, SCB y UPDATE, mientras CAPTURE se mantiene en 1, con ello, basta con operar normalmente la señal CLK para capturar y mantener la ruta de datos normal del circuito.

Además, es en este modo donde se corrige la falla causada por algún soft error, ya que si se da el caso que exista un error en PH2 o LA, O2 y O1 tendrán diferentes valores lógicos por lo que el elemento C mantendrá el estado anterior en la salida. De igual manera ocurre con PH1, PH2, LA y LB la saida Q conservará su estado anterior hasta el siguiente ciclo de reloj, si ya no existe el error.

■ Modo prueba: En este modo es donde se pueden extraer los datos de los elementos de almacenamiento requeridos y se encuentren dentro de la cadena. Una vez se active en alto la señal TEST se le indica al elemento C, que se puede apreciar en la figura 13, que active el transistor correspondiente y además permita el flujo de datos que provienen del latch LB de la parte de escaneo de la celda. En ese estado se pueden ingresar los vectores de prueba por medio de la entrada SI de LA y las señales SCB y SCA intercaladamente, siempre y cuando la señal CLK y CAPTURE se mantengan en cero.

Una vez finalizado el ingreso de todo el vector de prueba, se procede a enviar un pulso a la señal UPDATE para cargar el vector de datos en la logica combinacional del DUT.

Seguidamente se induce un estado de captura de datos, durante el cual se almacena la respuesta del circuito ante el vector ingresado anteriormente, para ello se establece un 1 en la señal CAPTURE y se activa la señal CLK para capturar la informacion en PH1, finalmente se intercalan las señales SCA y SCB hasta que se obtengan todos los bits de las celdas en SO.

# Capítulo 5

# Desarrollo de Solución

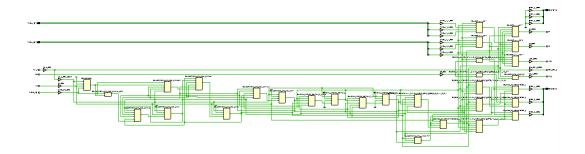

En esta sección se presentarán todos los circuitos utilizados durante la totalidad del proyecto. Desde los circuitos base u originales, hasta los diseños resultantes al realizar las modificaciones necesarias para mantener la operación original y la posibilidad de realizar las pruebas que se requieran, según la técnica de DFT que se utilizará.

Se cuenta con un circuito secuencial con el que se trabaja al inicio para poder comprender el funcionamiento de las modificaciones que se requieren implementar para las técnicas de DFT, a ese circuito original se le realizan simulaciones y se obtienen datos de consumo de potencia para poder tener datos bases de comparación cuando se implementen la técnicas ya descritas en secciones anteriores.

Al finalizar el estudio de las técnicas y comprendiendo su funcionamiento con la ayuda de ese circuito de pruebas, se procede a implementar las modificaciones necesarias a un microprocesador seleccionado aleatoriamente, del que no se tiene ningún criterio en especial para seleccionarlo.

Sin embargo, cabe resaltar que la implementación a ese microprocesador es teórica, ya que para poder implementar las técnicas de DFT, como se había mencionado antes, es necesario utilizarlas durante el diseño en sí del circuito, por lo que, al contar con un circuito y diseño ya finalizados, la complejidad de la implementación del DFT es muy alta, debido a que sería necesario estudiar y comprender completamente el comportamiento de todos los bloques que componen el circuito, lo cual requeriría una enorme cantidad de tiempo.

Considerando lo anterior, en este capítulo se detallarán los diseños y funcionamiento de un circuito original de pruebas, su respectivas modificaciones según el Scan Design, el Enhanced Scan y el Snapshot Scan; además de los circuitos de adquisición y generación de señales de control para pruebas del circuito de pruebas modificado con Scan Design, otro para Enhanced Scan y uno finalmente para Snapshot Scan.

De igual manera se muestran las modificaciones realizadas al microprocesador según Scan Design, Enhanced Scan y Snapshot Scan.

Se decide realizar circuitos por aparte de las técnicas y demás, por un tema de simplicidad y desconocimiento de operación del hardware generado por los rediseños. Una vez comprendido su funcionamiento al %100 se puede pensar en un diseño más robusto del circuito de adquisición y generación de señales de control, el cual en un solo circuito contenga todas las técnicas de DFT estudiadas, sin embargo, ese no es el objetivo principal del proyecto.

Se utilizan LEDs para mostrar resultados de pruebas como una versión inicial de detalle de resultados por su facilidad de utilización en HDL y ayuda para determinar de una manera más simple los resultados de las pruebas.

Todos los detalles de simulaciones, datos de potencia y area o elementos necesarios para la implementación, serán tocados en el siguiente capítulo.

## 5.1. Circuito de pruebas

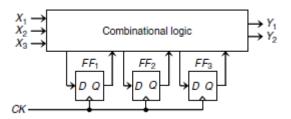

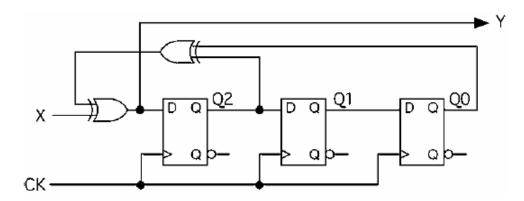

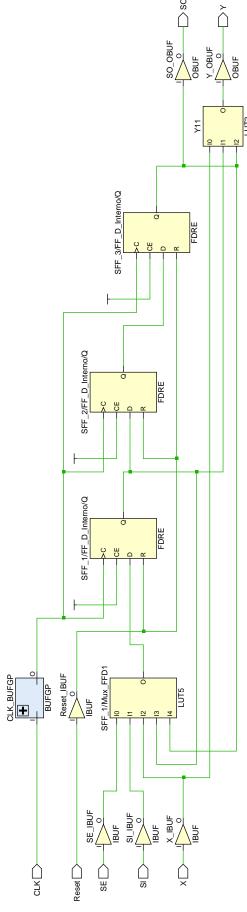

Como circuito de pruebas iniciales se utiliza el circuito tomado de [3] el cual es un ejemplo de circuitos secuenciales, el mismo se muestra en la figura 14.

Figura 14: Circuito inicial de pruebas. Tomado de [2]

$Q2^* = Y = X \oplus Q2 \oplus Q0$ ;  $Q1^* = Q2$ ;  $Q0^* = Q1$ ;

| Q2 | Q1 | Q0 | X=0   | X=1    | X=0 | X=1 |

|----|----|----|-------|--------|-----|-----|

| 0  | 0  | 0  | 000   | 100    | 0   | 1   |

| 0  | 0  | 1  | 100   | 000    | 1   | 0   |

| 0  | 1  | 0  | 001   | 101    | 0   | 1   |

| 0  | 1  | 1  | 101   | 001    | 1   | 0   |

| 1  | 0  | 0  | 110   | 010    | 1   | 0   |

| 1  | 0  | 1  | 010   | 110    | 0   | 1   |

| 1  | 1  | 0  | 111   | 011    | 1   | 0   |

| 1  | 1  | 1  | 011   | 111    | 0   | 1   |

|    |    |    | Q2* Q | 1* Q0* | •   | Y   |

Figura 15: Tabla de transiciones de circuito de pruebas. Tomado de [2]

Figura 16: Diagrama de estados de circuito de pruebas. Tomado de [2]

Este circuito consiste en una máquina de estados que tiene 1 entrada "X", y 1 salida "Y", la máquina avanzará entre sus 8 estados dependiendo de su señal de entrada. Su tabla de verdad y este comportamiento se puede ver en la tabla de la figura 15. La primer columna de la tabla indica el estado actual de las salidas de los flip-flop y con ello el estado actual e la máquina; la segunda columna indica el estado al que avanzará la máquina dependiendo del valor de "Xz la tercer columna indica el valor de la salida "Y"dependiendo del valor de "X".

Por ejemplo, en el estado 0, si "X.es igual a 0, se mantendrá el estado 0 y la salida "Y"será igual a 0, por lo contrario, si "X.es igual a 1 la máquina avanzará al estado 4 y la salida "Y"será igual a 1. Estado por estado se puede estudiar cada uno para entender el comportamiento de la máquina de estados.

Se determina el uso de este circuito debido a su simplicidad y al cumplimiento de un requisito primordial, contar con elementos de memoria de los cuales no es posible conocer la posicicón actual de la máquina, esto incluso conociendo los estados lógicos de su I/O. Es por ello que se requiere modificar el diseño del circuito para poder extraer esa información,

además de verificar su correcta funcionalidad, es decir, que avance al estado correcto y mantenga el valor correcto de la salida cuando se cumpla cierta condición.

Las modificaciones que se le realicen al circuito dependerá de la técnica de DFT a implementar, así como de la información requerida, sin tomar en cuenta que con todas las técnicas de DFT es posible el conocer los estados lógicos internos del circuito.

# 5.2. Uso de software para prueba de diseños HDL

El software ISE Design Suite cuenta con herramientas disponibles las cuales realizan un trabajo similar a la implementación de las técnicas de DFT. Una de estas herramientas es la aplicación llamada Chipscope Pro, el cual es utilizado para la depuración del código utilizado en la programación de FPGAs, según (Xilinx. UG029 (v14.3) October 16, 2012); con él es posible aplicar vectores de prueba en puntos deseados y ver el resultado de los mismos en las salidas, muy similar al DFT. Según la página web de Xilinx, desarrolladores del software, esta aplicación cuenta con un analizador lógico y diferentes componentes capaces de probar y realizar mediciones de hardware al circuito bajo prueba.

### 5.2.1. Chipscope Pro

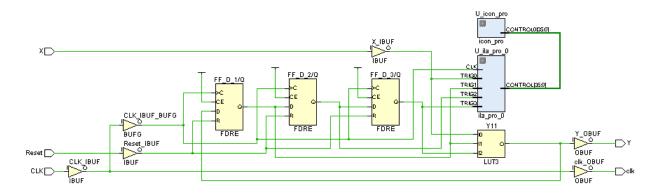

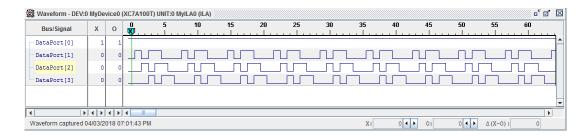

Al implementar el uso del software Chipscope Pro, se crea un core ILA (Integrated Logic Analyzer) el cual brinda ayuda para poder visualizar en un intervalo de tiempo el estado lógico de varios puntos del circuito implementado. A continuación se puede visualizar los bloques que agrega el software para poder realizar la captura de datos del circuito inicial de pruebas.

Figura 17: Circuito de pruebas modificado con Chipscope

Como se puede apreciar en la figura 17, los bloques agregados al diseño son U\_icon\_pro y U\_ila\_pro\_0 los cuales se encargan de realizar la captura de los datos, en este caso, de las salidas de los FF, las cuales indican el estado actual de la máquina de estados.

# 5.3. Diseño de circuito de adquisición y generación de datos

Se plantea el diseño de un circuito capaz de crear e incorporar al circuito de prueba (DUT, Device Under Test) los vectores de prueba que se le indiquen, así como la adquisición de los datos resultantes de la aplicación de estos vectores. Cabe aclarar que para cada tipo de tecnica se tendra un circuito de control.

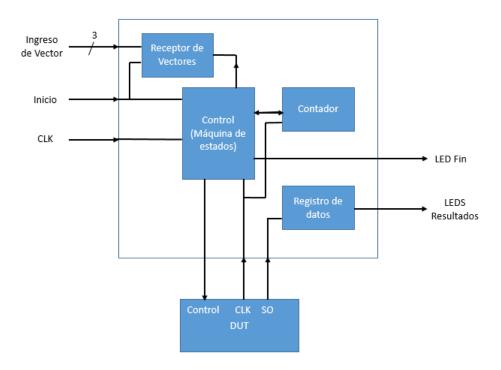

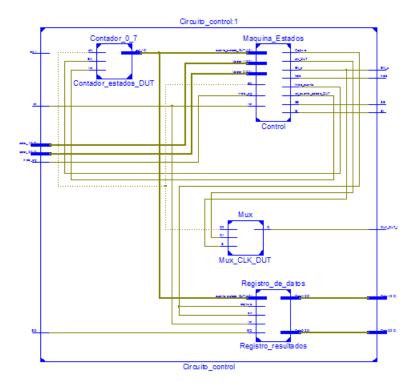

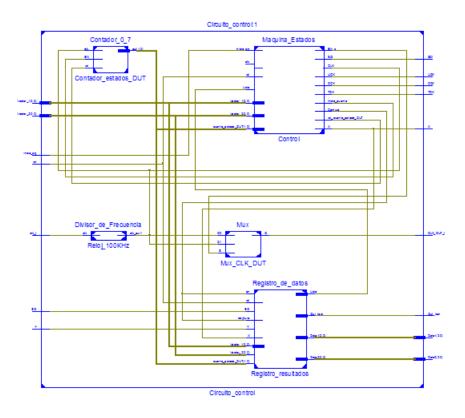

Figura 18: Diagrama de circuito de adquisicion y generación de datos.

El diagrama de bloques en el que se basa el diseño del circuito de adquisicion utilizado en las diferentes modificaciones del DUT original puede verse en la figura 18, el cual, generalmente está conformado por:

- Receptor de Vectores: Se encarga de recibir los vectores de prueba ingresados por el usuario que se utilizarán durante la prueba.

- <u>Control</u>: Se trata de una máquina de estados la cual se encarga de realizar en su totalidad todos los pasos necesarios para completar la prueba dependiendo del diseño de DFT utilizado, tareas como la generación de las señales de control (SI, SE, HOLD,etc) del DUT, la cuenta de los bits de los vectores enviados y el traslado de esos vectores de prueba desde el bloque Receptor de Vectores "hasta el DUT.

- <u>Contador</u>: Se encarga de llevar el registro de los ciclos de reloj que pasan durante la prueba, esto es necesario para que la máquina de estados envíe en el momento correcto los datos de control para poder ingresar los vectores de prueba así como el poder indicarle al registro de datos cuando almacenar datos.

• Registro de datos: Es necesario para poder almacenar los resultados despues de la prueba tomados del DUT y en este caso mostrar por medio de LEDs el estado actual de la máquina de estados cuando se realizó la carga de los vectores de pruebas.

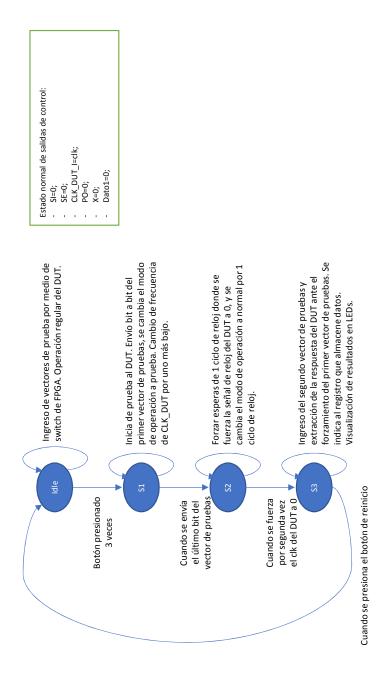

### 5.3.1. Circuito de control para Scan Design basico

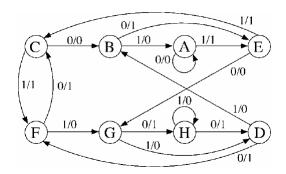

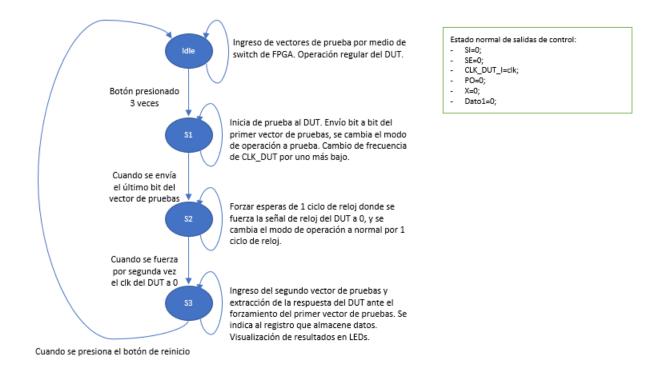

Figura 19: Diagrama de estados de control para Scan Design.

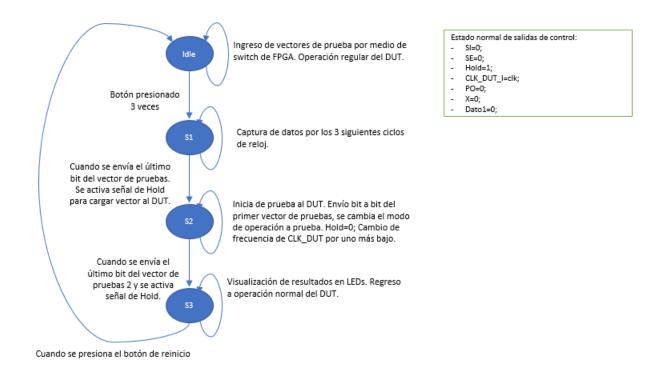

El anterior diagrama de estados describe el comportamiento de la máquina que se encarga de generar las señales de control para el DUT al que se le aplicara la técnica de Scan Design, así como se encarga de indicarle al registro de datos cuando debe iniciar la recolección de datos. Como se puede ver en la figura 19 la máquina normalmente está enviando las señales de control necesarias para que el circuito opere regularmente.

Una vez se desea iniciar la prueba, el usuario debe ingresar el primer vector de prueba por medio de los switch de la FPGA, presiona el pulsador central para indicar el almacenamiento del vector y seguidamente ingresa el segundo vector de prueba con los switch correspondientes, de nuevo, presiona el botón central y automáticamente se inicia la prueba.

Cuando se inicia la prueba, la máquina se encarga de realizar el cambio de señal de reloj al DUT por uno de menor frecuencia y cambia de estado la señal SE a 1. Esto le permite ingresar el vector 1 de prueba por medio de la señal SI, mientras transcurren n ciclos de reloj, donde n es el largo del vector de prueba, es decir, el largo de la cadena de celdas.

Cuando se finaliza el ingreso del vector 1, se le brinda una pausa de un ciclo de reloj al

DUT para que se distribuya correctamente el vector, seguidamente se le envía un pulso de reloj a la vez que se traslada a modo normal. Se realiza otra pausa de un ciclo de reloj para permitir la captura de las PO del DUT.

A continuación se procede a ingresar el segundo vector de pruebas y se realizan los mismos pasos que con el vector 1, a su vez se extraen los resultados generados por el vector anterior. Una vez que se finaliza el ingreso del vector 2, se tiene con certeza que se obtienen los resultados del vector 1, por lo que finaliza la prueba y se procede a indicar visualmente al usuario la finalización.

Los resultados de la prueba se mostrarán al usuario por medio de LEDs en la FPGA, dependiendo de si el largo de la cadena es menor a 16. Los n LEDs se ubicarán en orden de derecha a izquierda dependiendo del largo del vector de prueba, iniciando con el resultado del vector 1 y continuando con el vector 2.

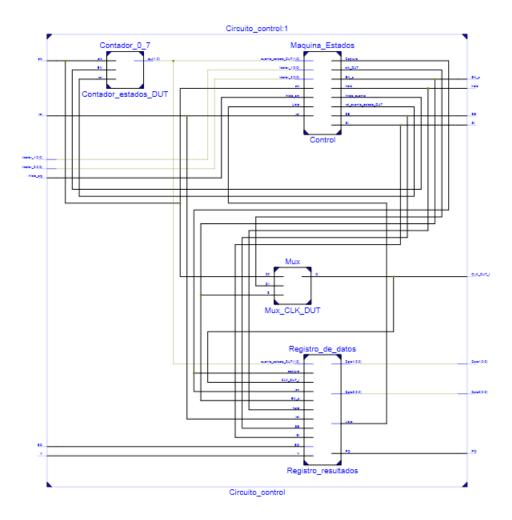

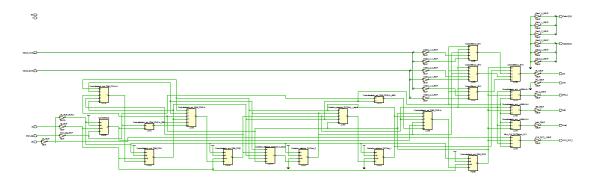

Figura 20: Esquemático de circuito de control para Scan Design.

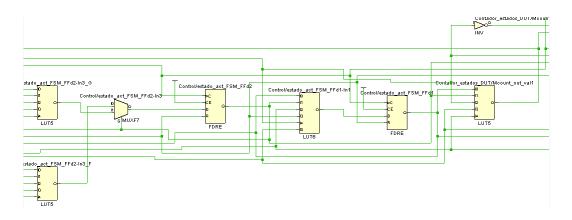

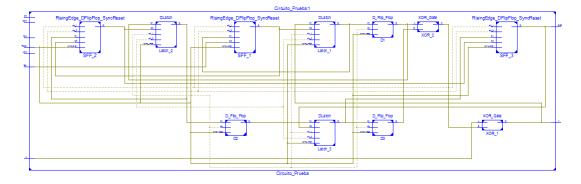

Figura 21: Esquemático Post synthesis de circuito de control para Scan Design.

Figura 22: Diagrama de tiempo para pruebas en Scan Design. Tomado de 2

Cuadro 1: Distribución de I/O para circuito de control para Scan Design

| Señal         | Tipo   | Función                                       |

|---------------|--------|-----------------------------------------------|

| inicio_sig    | Input  | Pulsador para iniciar la prueba               |

| clk           | Input  | Señal de reloj principal                      |

| rst           | Input  | Señal de reset general                        |

| Y             | Input  | Salida de PO del DUT                          |

| SO            | Input  | Salida de datos de DUT                        |

| Vector_1[2:0] | Input  | Ingreso de vector de pruebas 1                |

| Vector_2[2:0] | Input  | Ingreso de vector de pruebas 2                |

| SI            | Output | Entrada de datos de prueba del DUT            |

| SE            | Output | Señal de selección de datos del DUT           |

| CLK_DUT_I     | Output | Señal de reloj hacia el DUT                   |

| PO            | Output | Indicador de dato de salida principal del DUT |

| X             | Output | Señal de entrada para DUT                     |

| Dato1[2:0]    | Output | Bus de datos adquiridos del DUT               |

Tomando como base el diagrama de bloques de la figura 18 se construye el circuito de la figura 20, para el que se realizan ciertas modificaciones a la maquina de estados principal para poder cumplir con el diagrama de señales de la figura 22, tal y como se detalló anteriormente.

Dentro de los bloques que conforman este circuito se encuentra el contador de estados de DUT, el Registro de resultados, el multiplexor de la señal del CLK del DUT y el control general del circuito de adquisición. Cada uno realiza las funciones descritas anteriormente, con el ligero cambio en la máquina de estados encargada del control, a continuación se mostrarán ciertos detalles del esquemático resultante.

Contador de estados de DUT: Se encarga de contar los ciclos de reloj que han pasado después de ingresar un bit del vector de pruebas, es decir, lleva el control de los bits que se han ingresado al DUT; su salida forma parte de las condiciones de avance de la máquina de estados del control del circuito de adquisición.

Registro de resultados: Este bloque recibe las señales de control del DUT para evaluar los momentos en los que debe almacenar los datos que se muestren en la salida SO. Siempre y cuando se mantenga la señal Enable activa, cada vez que el registro determine la combinación indicada de las señales hold, SE, captura, SI y demás, almacenará los resultados del vector 2 de prueba, ya que es durante el ingreso de los bits del mismo que se pueden capturar los resultados del ingreso del primer vector.

Multiplexor de CLK: Este selector por medio de la señal EN\_s permite el ingreso de la señal CLK con la que comúnmente el DUT trabaja, o ingresa la señal de reloj que utiliza el circuito de control para realizar las pruebas.

Control general: Esta máquina de estado se encarga de generar las señales de control para el DUT cuando se active el modo de pruebas, las señales EN\_s, SI, SE, Inicia\_cuenta, rst\_cuenta y Captura son generadas para que el DUT opere normalmente o entre en modo de prueba.

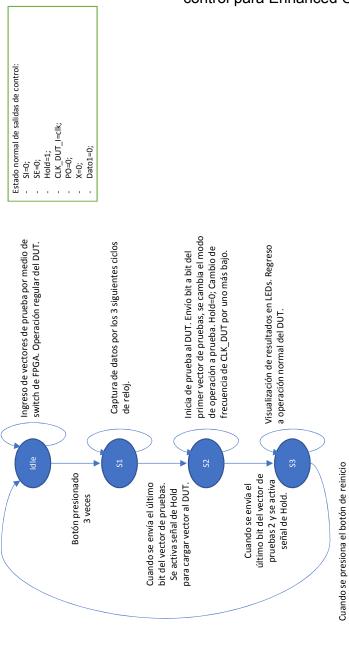

# 5.3.2. Circuito de control para Enhanced Scan

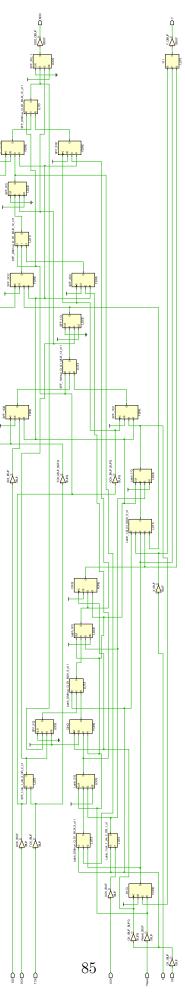

Figura 23: Esquemático de circuito de control para Enhanced Scan.

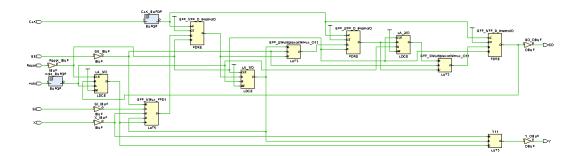

Figura 24: Esquemático Post synthesis de circuito de control para Enhanced Scan.

Figure 12.10: Enhanced-scan delay test application to sequential circuit.

Figura 25: Diagrama de tiempo para pruebas en Enhanced Scan. Tomado de 2

| Cuadro 2: Distribución de | [O] | para circuito d | de control | para Enhanced Scan |

|---------------------------|-----|-----------------|------------|--------------------|

|---------------------------|-----|-----------------|------------|--------------------|

| Señal         | Tipo   | Función                                       |

|---------------|--------|-----------------------------------------------|

| inicio_sig    | Input  | Pulsador para iniciar la prueba               |

| clk           | Input  | Señal de reloj principal                      |

| rst           | Input  | Señal de reset general                        |

| Y             | Input  | Salida de PO del DUT                          |

| SO            | Input  | Salida de datos de DUT                        |

| Vector_1[2:0] | Input  | Ingreso de vector de pruebas 1                |

| Vector_2[2:0] | Input  | Ingreso de vector de pruebas 2                |

| SI            | Output | Entrada de datos de prueba del DUT            |

| SE            | Output | Señal de selección de datos del DUT           |

| Hold          | Output | Señal de carga de datos en el DUT             |

| CLK_DUT_I     | Output | Señal de reloj hacia el DUT                   |

| PO            | Output | Indicador de dato de salida principal del DUT |

| X             | Output | Señal de entrada para DUT                     |

| Dato1[2:0]    | Output | Bus de datos adquiridos del DUT               |

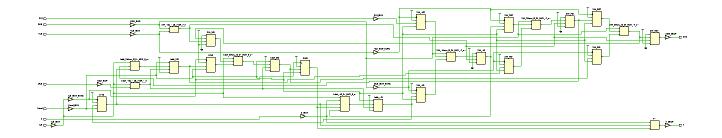

Para el caso del diseño del circuito de control para Enhanced Scan de la figura 23 también se toma como base el diagrama de bloques de la figura 18, al cual de igual manera que el circuito de control anterior, se le realizan modificaciones principalmente al bloque que contiene la máquina de estados para obtener el comportamiento esperado cuando se realice la extracción de datos internos del DUT. El resultado de la implementación post-synthesis es el que se puede apreciar en la figura 24, debido a que es difícil apreciar sus componentes, en la sección de Anexos se puede encontrar una versión ampliada del diagrama por si se desea percibir de mejor manera los bloques que lo componen.

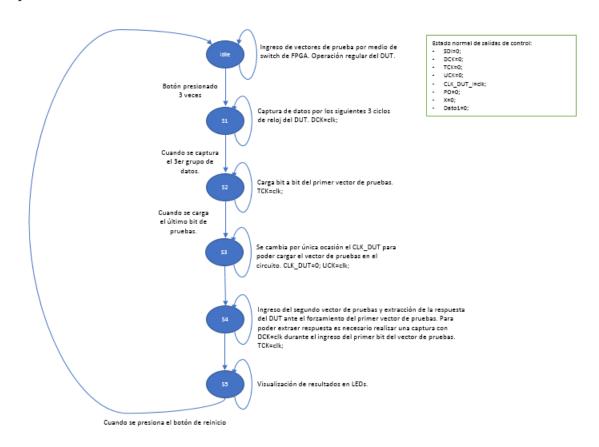

Hay que tener especial cuidado con la operación normal de los latches que se colocan a la salida de los SFF, ya que, para que el DUT opere regularmente debe mantenerse en alto la señal de HOLD, y cuando se realicen pruebas debe mantenerse en bajo hasta el punto que sea necesario. Tomando en cuenta esto, se construye la siguiente máquina de estados:

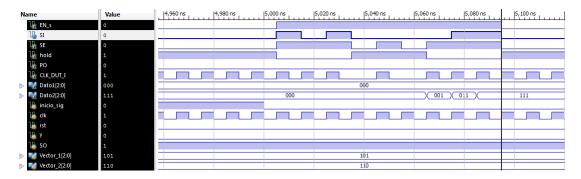

Figura 26: Diagrama de estados de control para Enhanced Scan.

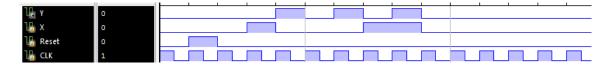

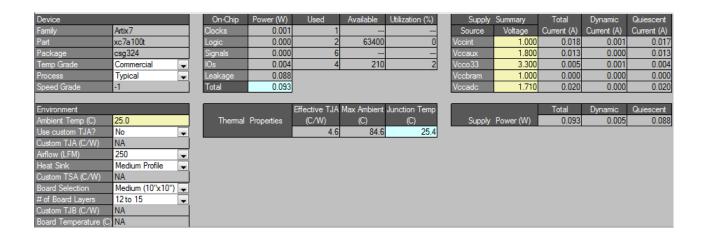

En el diseño de este circuito, al igual que en el utilizado para Scan Design y tomando como guia el diagrama de tiempos de la figura 25, se considera la necesidad de extraer datos del DUT mientras se ingrese el segundo vector de pruebas en la cadena de SFFs, con ello, mientras se está almacenando en los SFF el estado siguiente al que se desea llevar a la máquina, es decir, el vector 2; el circuito estabiliza en su lógica combinacional las señales que fueron ingresadas con el vector 1 y actualiza de inmediato el estado en el que se encuentra, el cual debe ser el estado consecutivo al vector 1 ingresado. Los bits que conforman el estado de la máquina, son extraídos uno a uno por medio del pin fisico SO, cada uno tarda 1 ciclo de reloj del circuito de control. Todo lo anterior se puede visualizar en la máquina de estados de la figura 26.