# Instituto Tecnológico de Costa Rica Escuela de Ingeniería Mecatrónica

Diseño de un modelo de inferencia energéticamente eficiente de un Vision Transformer implementado en FPGA para su aplicación en sistemas embebidos.

Informe de proyecto de graduación para optar por el título de Ingeniero en Mecatrónica con el grado académico de Licenciatura

Gabriel Eduardo Blanco Mora

2018149147

Cartago, febrero de 2025

Diseño de un modelo de inferencia energéticamente eficiente de un Vision Transformer implementado en FPGA para su aplicación en sistemas embebidos © 2024 by Gabriel Blanco se encuentra bajo la Licencia CC BY-NC-SA 4.0.

Declaro que el presente Proyecto de Graduación ha sido realizado enteramente por mi persona, utilizando y aplicando literatura referente al tema e introduciendo conocimientos propios.

En los casos en que he utilizado bibliografía, he procedido a indicar las fuentes mediante las respectivas citas bibliográficas.

En consecuencia, asumo la responsabilidad total por el trabajo de graduación realizado y por el contenido del correspondiente informe final.

Cartago, Costa Rica Febrero, 2025 Gabriel Eduardo Blanco Mora

Céd: 117880024

# INSTITUTO TECNOLÓGICO DE COSTA RICA PROGRAMA DE LICENCIATURA EN INGENIERÍA MECATRÓNICA PROYECTO FINAL DE GRADUACIÓN ACTA DE APROBACIÓN

El profesor asesor del presente trabajo final de graduación, indica que el documento presentado por el estudiante cumple con las normas establecidas por el programa de Licenciatura en Ingeniería Mecatrónica del Instituto Tecnológico de Costa Rica para ser defendido ante el jurado evaluador, como requisito final para aprobar el curso Proyecto Final de Graduación y optar así por el título de Ingeniero(a) en Mecatrónica, con el grado académico de Licenciatura.

Estudiante: Gabriel Euardo Blanco Mora

Proyecto: Diseño de un modelo de inferencia energéticamente eficiente de un Vision Transformer implementado en FPGA para su aplicación en sistemas embebidos

MSc/-Ing. (Jaime, Mora Meléndez)

Asesor

# INSTITUTO TECNOLÓGICO DE COSTA RICA PROGRAMA DE LICENCIATURA EN INGENIERÍA MECATRÓNICA PROYECTO FINAL DE GRADUACIÓN ACTA DE APROBACIÓN

Proyecto final de graduación defendido ante el presente jurado evaluador como requisito para optar por el título de Ingeniero(a) en Mecatrónica con el grado académico de Licenciatura, según lo establecido por el programa de Licenciatura en Ingeniería Mecatrónica, del Instituto Tecnológico de Costa Rica.

Estudiante: Gabriel Eduardo Blanco Mora

Proyecto: Diseño de un modelo de inferencia energéticamente eficiente de un Vision Transformer implementado en FPGA para su aplicación en sistemas embebidos

Miembros del jurado evaluador

Ing. Juan Luis Crespo Marino

Jurado

Ing. Ronald Loaiza Baldares

Jurado

Los miembros de este jurado dan fe de que el presente proyecto final de graduación ha sido aprobado y cumple con las normas establecidas por el programa de Licenciatura en Ingeniería Mecatrónica.

#### Resumen

En el presente informe se expone el diseño e implementación de un modelo de inferencia energéticamente eficiente basado en el algoritmo de clasificación de imágenes conocido como "Vision Transformer". Este modelo fue implementado en una FPGA y está orientado a aplicaciones de sistemas embebidos que demandan alta eficiencia energética.

El proceso de diseño inició con la identificación de las necesidades del cliente, lo cual permitió establecer los objetivos del sistema diseñado. A partir de estas necesidades se tomaron las decisiones pertinentes durante el desarrollo del modelo con el fin de garantizar los requerimientos en términos de precisión, eficiencia energética y tiempo de inferencia.

La optimización energética del modelo de inteligencia artificial se logró mediante técnicas de computación aproximada, específicamente a través de la cuantización directa de pesos y activaciones. En este caso, se utilizó la cuantización tipo FP16, implementada por medio del software Vitis 2023.2, lo que permitió realizar inferencias con mayor eficiencia energética y una pérdida de la precisión nula.

El correcto funcionamiento del diseño fue validado tanto mediante simulaciones realizadas en Vitis como mediante la toma de datos de manera directa al implementar el modelo optimizado en una FPGA. Los resultados obtenidos confirmaron que el sistema diseñado cumple con los requerimientos.

Palabras clave: FPGA, Cuantización, High Level Synthesis, eficiencia energética, precisión, Floating point 16.

## **Abstract**

This report presents the design and implementation of an energy-efficient inference model based on the image classification algorithm known as "Vision Transformer." This model was implemented on an FPGA and is aimed at embedded systems applications that require high energy efficiency.

The design process began with identifying the client's specific needs, which allowed the system's objectives to be defined. Based on these needs, the necessary decisions were made during the development of the model to ensure compliance with requirements in terms of accuracy, energy efficiency, and inference time.

The energy optimization of the artificial intelligence model was achieved through approximate computing techniques, specifically by directly quantizing the model's weights and activations. FP16 quantization was used, and it was implemented making use of Vitis 2023.2 software. Inference with higher energy efficiency and negligible loss of precision were achieved.

The design's correct functionality was validated through simulations carried out in Vitis and direct data collection by implementing the optimized model on an FPGA. The results confirmed that the designed system meets the client's requirements.

**Keywords**: FPGA, Quantization, High Level Synthesis, energy efficiency, precision, Floating Point 16

## **Dedicatoria**

Este proyecto está dedicado a mis padres Carlos Eduardo Blanco y Valeria Mora, mis hermanas Maripaz Blanco y Daniela Blanco, mi abuelita Mari y mi novia Catalina Muñoz, sin su apoyo y persistencia este proyecto de graduación no hubiese sido posible.

# Agradecimiento

Agradezco profundamente a Dios por la oportunidad de estudiar y todas las bendiciones que me ha dado. También quiero brindar mi más sincero agradecimiento a mis mentores durante este proyecto Luis León Vega y Jaime Mora Meléndez, así como a mi compañero del laboratorio ECAS Lab. Sin su apoyo incondicional y constante la confección de este proyecto no hubiese sido posible.

# Lista de Contenido

| Lista de Figuras                                                            | iii  |

|-----------------------------------------------------------------------------|------|

| Lista de Tablas                                                             | v    |

| Lista de Abreviaciones                                                      | vi   |

| 1. Introducción                                                             |      |

| 1.1 Entorno del proyecto                                                    | 1    |

| 1.2 Descripción del problema                                                | 1, 2 |

| 1.3 Síntesis del problema                                                   | 4    |

| 1.4 Objetivos                                                               | 4    |

| 1.4.1 Objetivo General                                                      | 4    |

| 1.4.2 Objetivos Específicos                                                 | 4    |

| 1.5 Estructura del documento                                                | 4, 5 |

| 2. Marco Teórico                                                            |      |

| 2.1 Transformadores de Visión                                               |      |

| 2.1.1 Patch Embedding                                                       |      |

| 2.1.2 Módulo de atención                                                    |      |

| 2.1.2 Módulo de Perceptrón multicapa                                        |      |

| 2.1.2 Patch Unembedding                                                     |      |

| 2.2 FPGA y High Level Synthesis                                             |      |

| 2.2.1 FPGA                                                                  |      |

| 2.2.2 High Level Synthesis                                                  |      |

| 2.3 Computación Aproximada y Cuantización                                   |      |

| 2.3.1 Cuantización Simétrica y Asimétrica                                   |      |

| 2.3.1 Cuantización Uniforme                                                 |      |

| 2.3.3 Dinámica y Estática                                                   |      |

| 2.3.4 Cuantización no Uniforme                                              |      |

| 2.3.4 PTQ (Post-Training Quantization) vs QAT (Quantization Aware Training) |      |

| 2.4 Estado del Arte y Cuantización en DNNs implementadas en FPGA            |      |

| 2.4.1 Cuantización INT8                                                     |      |

| 2.4.2 Cuantización de punto fijo                                            |      |

| 2.4.3 Cuantización Bfloat16                                                 |      |

| 2.4.4 Cuantización Posit                                                    |      |

| 2.4.5 Cuantización Logarítmica                                              |      |

| 2.4.6 Cuantización FP16                                                     |      |

| 2.5 Normativa en el área de aplicación ADAS                                 | 38   |

| 3. Marco Metodológico                                                       |      |

| 3.1 Planeación                                                              |      |

| 3.1.1 Insumos de SW necesarios                                              |      |

| 3.1.2 Insumos de HW necesarios                                              |      |

| 3.2 Identificación de necesidades del cliente                               |      |

| 3.3 Establecimiento de las especificaciones del producto                    |      |

| 3.4 Selección de conceptos                                                  | 47   |

| 3.4.1 Recomendaciones del asesor técnico-experto en el campo el doctor Luis León Vo | _  |

|-------------------------------------------------------------------------------------|----|

| 3.4.2 Revisión del estado del arte                                                  |    |

| 1) Activaciones                                                                     |    |

| 2) Pesos                                                                            | 50 |

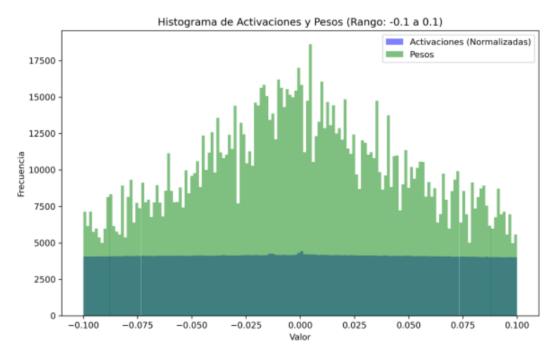

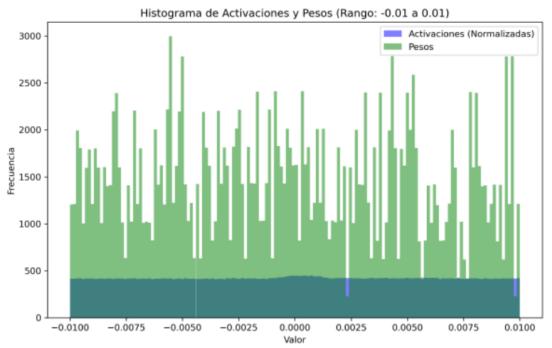

| 3) Histograma Combinado de activaciones y pesos                                     | 51 |

| 3.4.3 Distribución de valores de los tensores de los pesos y activaciones del ViT   | 48 |

| 3.4.4 Conceptos elegidos                                                            |    |

| 3.4 Selección del concepto ganador                                                  |    |

| 4. Diagnóstico del estado actual del modelo con los aceleradores del ECAS           | •  |

| Lab                                                                                 |    |

| 4.1 Desafíos enfrentados                                                            | 54 |

| 4.1 Precisión y tiempo de inferencia                                                | 55 |

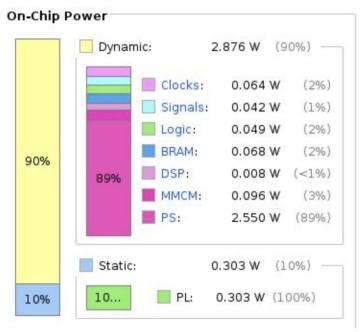

| 4.3 Potencia Disipada                                                               |    |

| 4.4 Recursos Computacionales                                                        | 57 |

| 5. Diseño e implementación de la solución                                           |    |

| 5.1 Modelo del ViT                                                                  |    |

| 5.2 Decisiones preliminares del diseño da la cuantización                           |    |

| 5.2.A Cuantización PTQ                                                              |    |

| 5.2.B Cuantización Estática                                                         |    |

| 5.3 Cantidad de bits de Mantisa y Exponente para FP16                               |    |

| 5.4 Implementación de la cuantización FP16 en el código del acelerador EW           | 64 |

| 6. Resultados y Anàlisis                                                            |    |

| 6.1 Pruebas de Validación de Precisión y tiempo de inferencia                       | 69 |

| 6.2 Simulación por medio de Vitis de potencia disipada por el acelerador            |    |

| 6.3 Resultados de precisión, Tiempo de inferencia, potencia disipada y Recursos     |    |

| computacionales utilizados                                                          |    |

| 6.3.A)Precisión                                                                     | 71 |

| 6.3.B)Tiempo de inferencia                                                          |    |

| 6.3.C)Recursos Computacionales                                                      | 73 |

| 6.3.D)Potencia Disipada                                                             | 74 |

| 6.3 Resultados de precisión, Tiempo de inferencia, potencia disipada y Recursos     |    |

| computacionales utilizados                                                          |    |

| 6.4 Cumplimiento de las especificaciones propuestas                                 |    |

| 6.5 Análisis Financiero                                                             |    |

| 6.5.A)Egresos                                                                       |    |

| 7.Conclusiones y Recomendaciones                                                    | 15 |

| 7.1 Conclusiones                                                                    | 81 |

| 7.2 Recomendaciones                                                                 |    |

| Referencias                                                                         |    |

| Apéndices v Anexos                                                                  | 87 |

# Lista de figuras

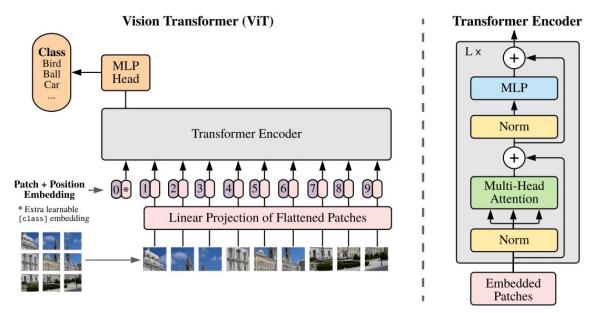

| Figura 1. Arquitectura de un Vision Transformer                                              | 8   |

|----------------------------------------------------------------------------------------------|-----|

| Figura 2. Arquitectura del primer módulo del ViT: Patch Embedding                            | 9   |

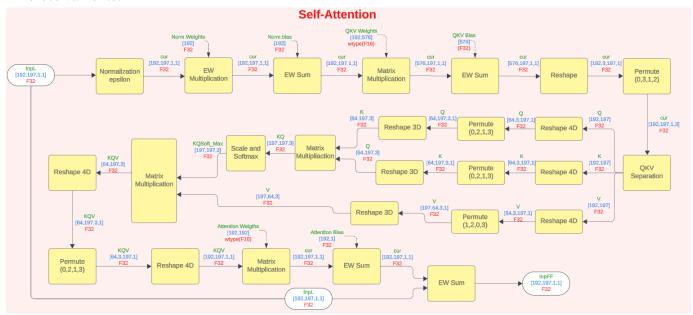

| Figura 3. Arquitectura del Segundo módulo del ViT: Self-Attention                            | 11  |

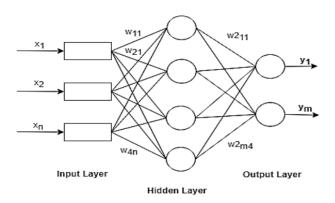

| Figura 4. Red neuronal MLP [9]                                                               | 15  |

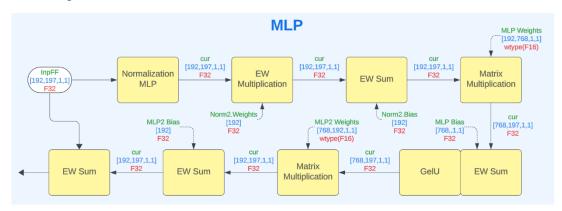

| Figura 5. Tercer módulo del ViT: MLP                                                         | 16  |

| Figura 6. Funciones GeLU, ReLU y ELU.                                                        | 16  |

| Figura 7. Módulo Final del ViT: Unembedding                                                  | 17  |

| Figura 8. Representación gráfica de los tipos de cuantización                                |     |

| Figura 9. Comparación gráfica entre cuantización uniforme (izquierda) y no uniforme (derect  |     |

| [17]                                                                                         |     |

| Figura 10. Mapeo de la cuantización simétrica (izquierda) y asimétrica (derecha) [17]        | 23  |

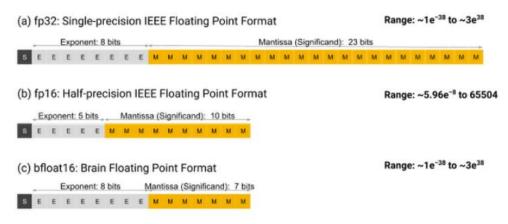

| Figura 11. Tres formatos de punto flotante [31]                                              | 31  |

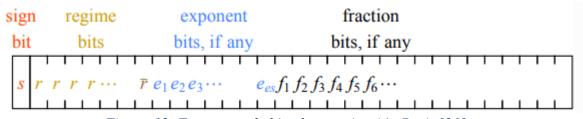

| Figura 12. Estructura de bits de cuantización Posit [36]                                     | 32  |

| Figura 13. Valor de "k" para distintas combinaciones de bits de régimen                      | 33  |

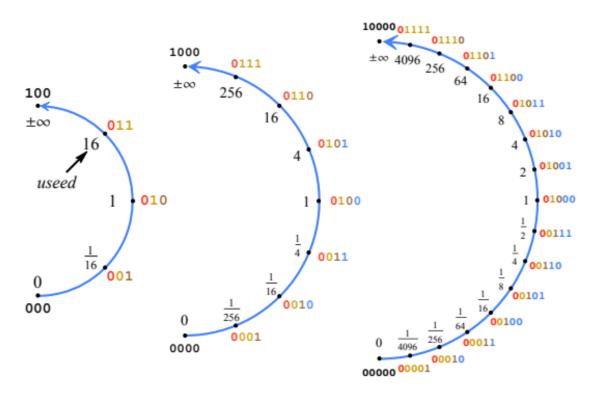

| Figura 14. Construcción de posit para 3, 4 y 5 bits con es=2 [36]                            | 34  |

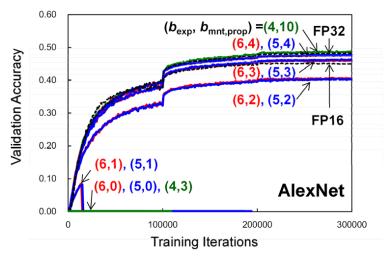

| Figura 15. Precisión top 1 de AlexNet para FP32 y FP16 para distintas cantidades de iteracio | nes |

| [41]                                                                                         | 37  |

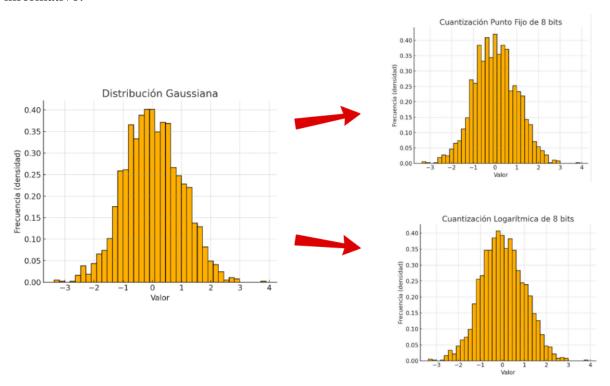

| Figura 16. Cuantización de punto fijo y logarítmica para una distribución uniforme           | 48  |

| Figura 17. Cuantización de punto Fijo y Logarítmica para distribución Gaussiana              | 49  |

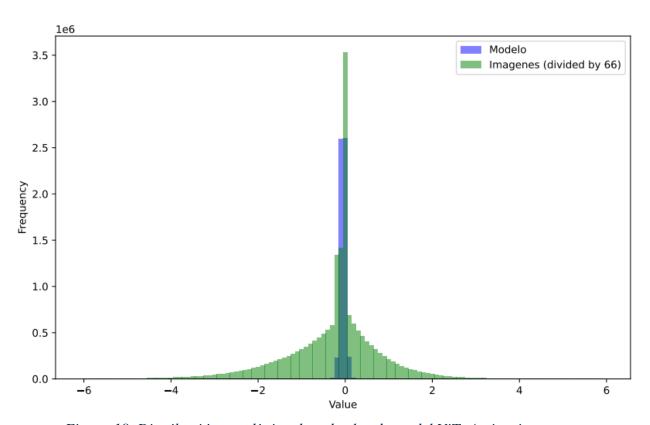

| Figura 18. Distribución estadística de todos los datos del ViT: Activaciones y pesos         | 51  |

| Figura 19. Resultados de precisión top1 y tiempo de inferencia promedio para el acelerador E | W   |

| FP32                                                                                         | 56  |

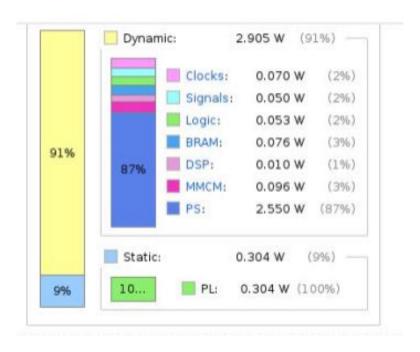

| Figura 20. Potencia disipada por el acelerador EW FP32.                                      | 57  |

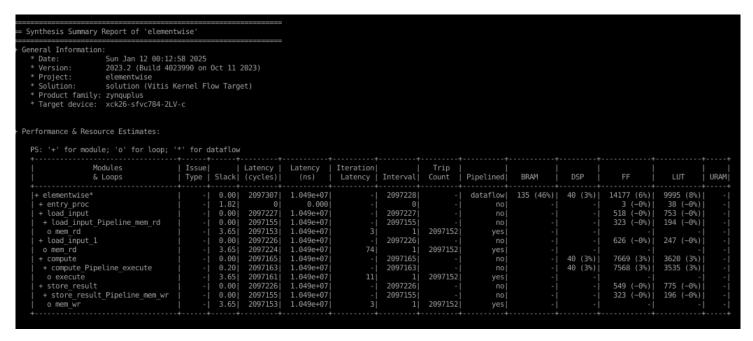

| Figura 21. Resumen de reporte de sintesis "Csynth.rpt" generado por Vitis para el acelerador |     |

| elementwise FP32                                                                             | 58  |

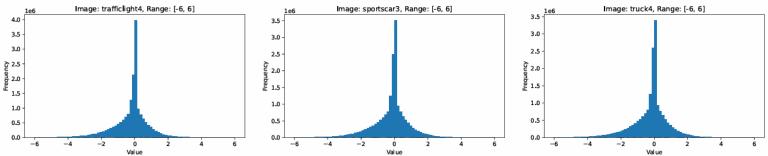

| Figura 22. Comparación de histograma de pesos y activaciones para 3 imágenes distintas       |     |

| relacionadas a ADAS del set de datos imagenet1k                                              | 61  |

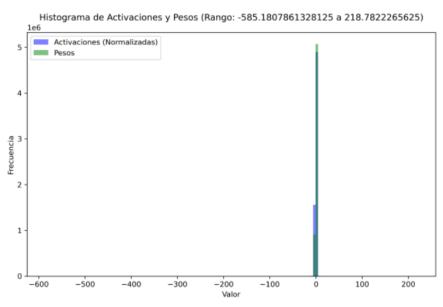

| Figura 23.Histograma de activaciones y pesos operandos de EW con rango igual al rango        |     |

| dinámico de los datos                                                                        | 62  |

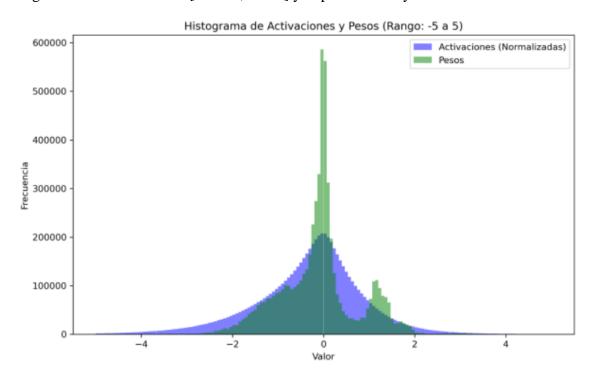

| Figura 24. Histograma de activaciones y pesos operandos de EW con rango de -5 a 5            | 63  |

| Figura 25. Histograma de activaciones y pesos operandos de EW con rango de -0.1 a 0.1        | 64  |

| Figura 26. Histograma de activaciones y pesos operandos de EW con rango de -0.01 a 0.01      | 65  |

| Figura 27. Funciones quantize, execute_multiply, execute_add y dequantise del código en C-   | ++  |

| del acelerador EW FP16                                                                       | 66  |

| Figura 28. Error de timing en la generación del bitstream para el acelerador EW FP16         | 67  |

| Figura 29. Función "process" del código en C++ del acelerador EW FP16                        | 68  |

| Figura 30. Función "compute" del código en C++ del acelerador EW FP16                        | 69  |

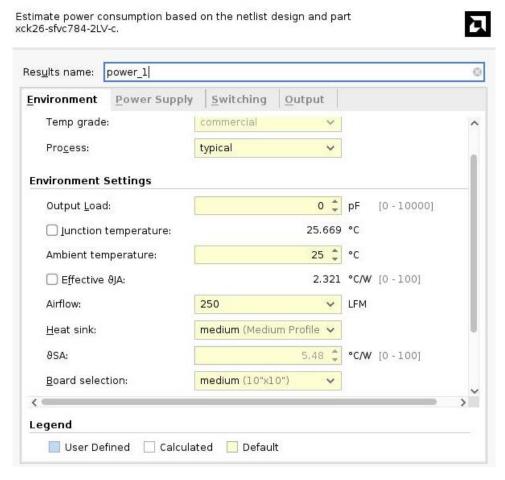

| Figura 31. Condiciones ambientales para simulación de la potencia disipada por el acelerador |    |

|----------------------------------------------------------------------------------------------|----|

| EW FP16                                                                                      | 71 |

| Figura 32. Resultados de precisión top1 y tiempo de inferencia promedio para la solución     |    |

| propuesta                                                                                    | 72 |

| Figura 33. Resumen de reporte de síntesis "Csynth.rpt" generado por Vitis para el acelerador |    |

| elementwise FP16                                                                             | 73 |

| Figura 34. Estimación de uso de potencia de la solución propuesta                            | 76 |

# Lista de Tablas

| Tabla 1. Características necesarias de CPU para ejecutar Vitis HLS y de la CPU del servidor | "xrp |

|---------------------------------------------------------------------------------------------|------|

| france" [1]                                                                                 | 42   |

| Tabla 2. Interpretación de las necesidades del cliente.                                     | 43   |

| Tabla 3. Especificaciones del producto por diseñar                                          | 46   |

| Tabla 4. Matriz de Selección del Concepto Ganador                                           | 53   |

| Tabla 5. Recursos Computacionales utilizados por el acelerador EW FP32                      | 58   |

| Tabla 6. Precisión y tiempo de inferencia de los 4 modelos                                  | 59   |

| Tabla 7. Recursos Computacionales de la solución propuesta.                                 | 74   |

| Tabla 8. Valor obtenido de la solución implementada para cada una de las especificaciones   | 77   |

| Tabla 9. Resumen de gastos del proyecto                                                     | 80   |

| Tabla 10. Resumen de ahorro económico y retorno de inversión para diferentes escalas de     |      |

| implementeación                                                                             | 81   |

# Lista de Abreviaciones

| 1.  | ECAS lab | Efficient Computing Across the Stack Lab |

|-----|----------|------------------------------------------|

| 2.  | FPGA     | Field Programmable Gate Array            |

|     | CPU      |                                          |

| 4.  | TPU      | Tensor Processing Unit                   |

| 5.  | GPU      | Graphics Processing Unit                 |

|     | DNN      |                                          |

| 7.  | FAL      | Flexible Accelerator Library             |

| 8.  | CNN      | Convolutional Neural Networks            |

| 9.  | ADAS     | Advanced Driver Assistance systems       |

| 10. | NLP      | Natural Language Processing              |

|     | ViT      |                                          |

| 12. | MLP      | Multilayer Perceptron                    |

| 13. | EW       | Element-Wise                             |

| 14. | IA       | Inteligencia Artificial                  |

| 15. | GeLU     | Gaussian Error Linear Unit               |

| 16. | HDL      | Harware Description Language             |

| 17. | RTL      | Register Transfer Logic                  |

| 18. | HLS      | High Level Synthesis                     |

| 19. | IP       | Intelectual Property                     |

| 20. | IOT      | Internet of things                       |

| 21. | HW       | Hardware                                 |

| 22. | SW       | Software                                 |

| 23. | LUTs     | Look-Up Tables                           |

| 24. | DSPs     | Digital signal Processors                |

| 25. | FFs      | Flip-Flops                               |

| 26. | ASICs    | Application Specific Integrated Circuits |

| 27. | PTQ      | Post-training Quantization               |

| 28. | QAT      | Quantization-Aware Training              |

| 29. | FP       | Floating Point                           |

| 30. | FPS      | Frames per second                        |

| 31. | NaN      | Not a number                             |

|     |          | Exact multiply and Accumulate            |

| 33. | BRAM     | Block Random access memory               |

| 34. | SD       | Sistema diseñado                         |

## 1. Introducción

## 1.1Entorno del proyecto

El proyecto se llevó a cabo en conjunto con el ECAS Lab (Efficient Computing Across the Stack Lab) perteneciente a la escuela de ingeniería electrónica del Instituto Tecnológico de Costa Rica. Este laboratorio se dedica a estudiar la optimización energética de modelos computacionales de inteligencia artificial desde una perspectiva holística, es decir, analiza métodos para obtener una mayor conservación de energía desde varias aristas. Se analiza como perfeccionar tanto el Software como el Hardware, y también como utilizar el Edge y el "Cloud Computing" en armonía para obtener el mejor rendimiento, junto al menor gasto de recursos posible [1] [2].

El laboratorio y sus investigadores se han enfocado en el desarrollo de distintos tipos de aceleradores de Hardware para operaciones que se utilizan frecuentemente en algoritmos de inteligencia artificial. Para la implementación de estos aceleradores de Hardware, las FPGAs se presentan como una alternativa más energéticamente amigable a otros tipos de Hardware, como las CPUs, TPUs (Tensor processing Unit) o las GPUs, las cuales poseen una demanda exorbitante en la industria hoy en día, y además no son muy eficientes en términos energéticos.

Por otra parte, el proyecto se realizó bajo la supervisión directa del MHPC Luis G. León Vega. En la actualidad, el máster León se encuentra en la Universidad de Trieste en Italia trabajando en su tesis doctoral [3]. León trabaja activamente con el ECAS Lab y su tesis de maestría consistió en el desarrollo de una serie de aceleradores de Hardware genéricos para redes neuronales profundas (DNN). Además, generó un "framework" denominado FAL ("Flexible Accelerator Library") el cual se enfoca en facilitar la implementación de nuevos aceleradores de Hardware.

Uno de los algoritmos que se han implementado utilizando estos aceleradores de Hardware en FPGA son los "Vision Transformers". Este algoritmo de inteligencia artificial sigue prácticamente al pie de la letra al famoso modelo de transformador que utilizan los "Large Language Models", con la diferencia de que la entrada del modelo será una imagen en lugar de una serie de palabras. Los llamados "Vision Transformers" han demostrado ser una alternativa altamente competitiva, y en muchos casos superior, a las clásicas redes neuronales convolucionales (CNN). Como se afirma en [4], esta arquitectura obtiene resultados de precisión muy similares a las CNN del estado del arte, pero requiere de un tiempo de entrenamiento mucho menor.

Aunque hasta el momento la investigación del máster Luis León ha obtenido resultados satisfactorios en términos de eficiencia energética y precisión, existen varias técnicas de

computación aproximada que podrían llegar a reducir aún más los recursos energéticos necesarios para la inferencia de estos algoritmos. [5]

## 1.2 Descripción del problema

La mayoría de los modelos de inteligencia artificial que en la actualidad están revolucionando a la sociedad utilizan computación en la nube debido a los altos requerimientos computacionales y energéticos que poseen, no solo para el proceso de entrenamiento, sino también para el de inferencia [6]. En ciertas aplicaciones implementadas en sistemas embebidos, como por ejemplo los sistemas avanzados de asistencia al conductor (ADAS), no se tiene esta posibilidad.

Los sistemas ADAS son de naturaleza crítica y, en la mayoría de las ocasiones, no pueden emplear la nube para procesar los datos debido a la posibilidad de encontrarse en zonas con conectividad limitada o a la necesidad de operar en tiempo real [1]. Por lo tanto, es necesario recurrir a la computación en el borde (Edge Computing). Además, en este contexto, es fundamental optimizar el consumo de energía durante el procesamiento de datos mediante inteligencia artificial para prolongar la duración de la batería y aumentar el alcance entre cargas.

Al reducir los recursos computacionales necesarios para procesar los datos en el borde, se incrementa el rango de los vehículos y se permite que los algoritmos se ejecuten en computadoras de menor costo. Esto contribuye tanto a la democratización como al acceso generalizado de estas tecnologías. Además, se reduce la huella de carbono asociada al funcionamiento de estos sistemas. Sin embargo, al disminuir los recursos energéticos, es común que se pierda precisión en el modelo, lo cual es poco deseable en este contexto donde la precisión es crítica, ya que de ello depende la seguridad e integridad humana.

Actualmente, los circuitos integrados que suelen utilizarse para implementar las redes neuronales son GPUs (Graphic processing Units). Aunque, debido a su capacidad de paralelización, las GPUs son en principio candidatas ideales para implementar algoritmos de inteligencia artificial, estas consumen altos niveles de energía. Además, en la actualidad, la oferta de este producto no es suficiente para la enorme demanda que poseen a nivel mundial. Por estas razones, este tipo de Hardware no es ideal para las aplicaciones relacionadas a sistemas embebidos que no tienen acceso a computación en la nube [3]. Un dispositivo que surge como candidato para solucionar esta problemática energética es el Field Programmable Gate Array (FPGA),

principalmente las de gama baja. Las FPGAs ofrecen un mayor rendimiento por unidad de energía consumida debido a su arquitectura configurable y la versatilidad en su implementación.

La tesis doctoral del MHPCH Luis G. León Vega se enfoca en el desarrollo de aceleradores de Hardware para operaciones matemáticas de uso común en DNN. En el marco de esta investigación, se presenta la problemática de que el proceso de inferencia de los algoritmos basados en atención aún no posee niveles de eficiencia energética ideales, lo cual es fundamental para las aplicaciones de ADAS. Este Proyecto toma como referencia el trabajo que ya ha sido realizado por el Máster Luis León Vega y optimiza el consumo energético a un grado aún mayor utilizando técnicas de computación aproximada.

## 1.3 Síntesis del problema

Las alternativas actuales para la aceleración de redes neuronales basadas en sistemas de atención del ECAS Lab implementadas en FPGA no obtienen niveles ideales de eficiencia energética, lo cual conlleva a dificultades de implementación en dispositivos con recursos energéticos restringidos.

# 1.4 Objetivos

## 1.4.1 Objetivo General

Desarrollar un acelerador energéticamente eficiente del proceso de inferencia de un Vision Transformer para su uso en sistemas embebidos con restricciones energéticas.

## 1.4.2 Objetivos Específicos

- Analizar el estado actual de los aceleradores de Hardware diseñados en el ECAS Lab con el fin de identificar oportunidades de mejora en términos energéticos.

- Diseñar una optimización del modelo Vision Transformer utilizando técnicas de computación aproximada para disminuir el gasto energético, manteniendo la precisión en las operaciones de inferencia

- Implementar en FPGA la optimización del modelo Vision Transformer diseñada.

- Validar que el modelo implementado mantiene la precisión de clasificación de imágenes al realizar la inferencia de un set de datos relacionado a sistemas de conducción autónoma.

#### 1.5 Estructura del documento

En el presente documento se describe detalladamente el proceso de diseño de un modelo de inferencia energéticamente eficiente de un Vision Transformer implementado en FPGA. El documento se divide en 7 secciones principales: Introducción, Marco Teórico, Marco Metodológico, Diagnóstico, Diseño de la solución, Resultados y Análisis y Conclusiones y Recomendaciones. A continuación se describe brevemente en que consiste cada uno de estos capítulos.

La introducción corresponde al primer capítulo y en ella se describen generalidades del proyecto tales como su contexto y entorno. Se describe de manera breve la organización con la cual se realiza el proyecto y cuáles son sus objetivos principales. También se presenta el problema de investigación y se determinan los objetivos que se buscan alcanzar para presentar una solución ante esta problemática.

El Marco Teórico define los conceptos ingenieriles que son necesarios tener claros para comprender el desarrollo del proyecto y las decisiones de diseño que se toman. Se tratan temas del funcionamiento interno y la arquitectura de los transformadores de visión, FPGAs y High Level Synthesis, y computación aproximada. Además se describe de manera detallada los distintos tipos de cuantización y los resultados del estado del arte con estos tipos de cuantización.

El Marco metodológico describe y aplica la metodología de diseño de productos conocida como Ulrich-Epinger. Se mencionan también las distintas etapas que conforman esta metodología, que corresponden a: Planeación, Identificación de las necesidades del cliente, establecimiento de las especificaciones del producto, selección de conceptos candidatos y selección del concepto ganador.

El cuarto capítulo se denomina Diagnóstico y detalla el estado actual de los aceleradores de HW diseñados por el ECAS Lab y como han sido implementados hasta el momento en el modelo de Inteligencia Artificial ViT. En este capítulo también se muestran el rendimiento actual del modelo con los aceleradores en términos de precisión de clasificación, cantidad de recursos computacionales, potencia disipada y tiempo de inferencia.

Posteriormente en el capítulo de Diseño de solución se detalla como se diseña e implementa la cuantización en el modelo con el fin de mejorar su eficiencia energética al mismo tiempo que se mantiene la precisión. Se exponen todas las decisiones de diseño tomadas y el razonamiento

ingenieril con el cual se llegó a estas decisiones. Además se expone un estudio de histogramas con el cual se tomaron decisiones de diseño.

El capítulo de resultados y análisis muestra el rendimiento del modelo ViT con la cuantización diseñada implementada. Primero se describen las pruebas de validación diseñadas y luego se muestran los resultados de cantidad de recursos computacionales utilizados, potencia disipada, latencia y precisión del modelo. Finalmente se evalúa si estos resultados cumplen con los requerimientos iniciales del cliente y se analiza las razones por la cuales estos requerimientos fueron alcanzados o no. El capítulo final de conclusiones y recomendaciones se resumen los resultados del proyecto y se dan recomendaciones generales para futuros trabajos relacionados.

## 2. Marco Teórico

#### 2.1 Transformadores de Visión

En el contexto de la inteligencia artificial, los transformadores consisten en un tipo de arquitectura de red neuronal profunda que introduce el mecanismo de atención. Este algoritmo fue introducido en el año 2017 por un equipo de investigadores de Google en el "paper" "Attention is all you need" y fue diseñado originalmente con el objetivo de destacarse en el área de procesamiento de lenguaje natural (NLP). El mecanismo de atención revolucionó el mundo de la inteligencia artificial ya que permite al modelo enfocarse en distintas partes de una secuencia de entrada de manera flexible. Esto se debe a que el modelo no se basa en un procesamiento secuencial, sino en uno en paralelo que busca relaciones e identifica dependencias complejas entre distintas secciones de la información que debe procesar [6].

En el año 2021 se introduce un "paper" denominado "An Image is worth 16x16 words". Esta investigación presenta un algoritmo que se basa fundamentalmente en la arquitectura del transformador, pero introduce unos cuantos cambios para poder enfrentarse a la tarea de clasificación de imágenes sin perder la capacidad de entendimiento de contexto que poseen los transformadores. Los Transformadores de Visión (ViT por su siglas en inglés presentan ciertas ventajas con respecto a otros algoritmos de visión de computadora, como por ejemplo las redes neuronales convolucionales. La principal de ellas es que, en tareas de clasificación de imágenes, el ViT puede alcanzar precisiones y resultados muy similares o ligeramente superiores que los otros algoritmos de vanguardia, pero requiere significativamente menos recursos computacionales en el proceso del preentrenamiento. Los ViT alcanzan estas precisiones especialmente cuando se entrenan con grandes conjuntos de datos [4]. A continuación, se explica a detalle la arquitectura de los ViT.

Los Vision Transformers (ViT) constan de cuatro secciones o módulos principales: "Patch Embedding", "Attention", "Multilayer Peceptron (MLP)" y "Unembedding". En el Patch Embedding, la imagen se divide en pequeños parches (patches), que se codifican en vectores de alta dimensionalidad, y se añade un "class token" que se utilizará para la clasificación final. En la fase de Attention, el modelo intercambia contexto entre los patches, permitiendo una comprensión global de la imagen. Luego, en la MLP, estos vectores se refinan a través de capas densas para extraer características más complejas. Finalmente, en la fase de Unembedding, se analiza el class token, que se multiplica por una matriz de pesos para producir un vector de probabilidades, que

determina la clase a la que pertenece la imagen. En la Figura 1 se muestra la representación de la arquitectura del ViT que fue presentada en el "paper" original [4]. A continuación, se explica a fondo cada uno de estos módulos del ViT, así como de las operaciones matemáticas que los componen.

## **2.1.1 Patch Embedding:**

Figura 1. Arquitectura de un Vision Transformer

En la Figura 1 se ilustra la arquitectura y las operaciones matemáticas del módulo "Patch Embedding". En esta, así como en las siguientes figuras, cada rectángulo simboliza una operación matemática del modelo, las flechas continuas indican el tensor de entrada a medida que avanza por todas las operaciones, y las líneas discontinuas corresponden a los tensores de parámetros entrenables, como los pesos y bias del modelo. En este primer módulo del ViT, la imagen se divide en patches de un tamaño determinado, que son simplemente secciones cuadradas de la imagen original. Al ingresar al modelo, la imagen se representa como un tensor con forma [HxWxC], donde H y W se refieren a las dimensiones de la imagen, y C corresponde al número de canales, que comúnmente es 3 en una representación RGB.

Esta imagen primero pasa por una operación de convolución que cumple con dos funciones principales. En primer lugar, al configurar un tamaño de "Kernel" y un "Stride" iguales a las dimensiones deseadas de los patches, y no aplicar "Padding", la convolución tiene la capacidad de separar la imagen en patches. En segundo lugar, los valores del Kernel son entrenados para que, simultáneamente con la separación en patches, el modelo genere los "embeddings" correspondientes a cada patch. Un embedding corresponde a una representación numérica de cada patch que capta sus características en un espacio de altas dimensionalidad.

Figura 2. Arquitectura del primer módulo del ViT: Patch Embedding

A continuación, se suma un término de Bias mediante una operación EW a cada patch, lo cual ajusta sus activaciones permitiendo al modelo capturar mejor las características de cada uno. Es importante mencionar que, a lo largo del proceso, se realizan operaciones como por ejemplo "permutes" o "reshapes" que no serán explicadas en este marco teórico, ya que estas solo se encargan de ajustar la forma de los tensores para que tengan el formato indicado para las operaciones matemáticas.

Luego, el class Token se concatena al tensor de entrada. Este Token es fundamental en los Vision Transformer porque representa una visión global o un tipo de "resumen" de todas las características todos patches. Durante el proceso de atención, el class token interactúa con todos los demás patches y genera una visión del contexto o el significado de la imagen entera. Como se muestra en la Figura 2 , la inicialización de sus valores se realiza durante el proceso de entrenamiento.

Finalmente, por medio de una operación de suma "element-wise" (EW), el tensor de positional embedding se une al tensor de la imagen. A diferencia de los transformadores aplicados

en Natural Language Processing (NLP), los valores del tensor positional embeding son completamente generados durante el proceso de entrenamiento, no se usa ningún tipo de codificación senoidal, como sí se hace en NLP. La función primordial del positional embedding es proporcionar información sobre la estructura espacial de cada patch al ViT, es decir, permite que el ViT entienda en qué posición de la imagen original se encuentra cada patch.

Como se observa en la Figura 2, la salida del módulo de Patch Embedding se copia en un tensor etiquetado como InpLL. Este tensor se reutiliza al final del módulo de atención, donde se suma a la salida de la capa de atención. Conceptualmente, este tensor representa una codificación numérica de cada parche de la imagen original, es decir, una lista de valores que encapsula tanto las características visuales como la ubicación espacial de cada sección de la imagen. Esta representación se ha formado a través de su interacción con los parámetros entrenables de la red, proporcionando una base para el procesamiento posterior en el modelo.

#### 2.1.2 Módulo de atención:

El módulo de atención es fundamental en los transformadores, ya que es quien permite que la entrada sea analizada de manera íntegra y completa, tomando en cuenta las relaciones y interacciones entre cada token y el resto, lo cual permite tener una idea contextualizada y global de los datos que se están analizando. En otras palabras, el mecanismo de autoatención permite que cada token de la entrada considere y brinde contexto a todos los demás tokens logrando captar relaciones complejas entre ellos de manera eficiente. En los enfoques y algoritmos de IA anteriores esto no era posible, ya que las relaciones entre los elementos de entrada estaban limitadas a sus vecinos inmediatos. El lograr entender un contexto global es lo que ha permitido que este algoritmo de IA sea tan poderoso y sea capaz de enfrentarse a tareas que hace unos años era inimaginables para modelos de IA.

Para entender esta función del mecanismo de autoatención, se puede analizar el siguiente ejemplo enfocado en NLP. Considérese, la palabra "banco". Esta palabra puede tener varios significados, y el significado que corresponde es comúnmente dado por el contexto. En la oración "Me senté en el banco" su significado se refiere a un asiento, pero en la oración "Deposité dinero en el banco" su significado es el de una institución financiera. En ambos casos, la definición de la palabra está dado por los tokens cercanos, sin embargo, si consideramos un texto más largo que finaliza con la oración "Me dirigí al banco", el significado de la palabra será uno si al inicio del texto dice "Me encontraba caminando en el parque" y otro si dice "Necesitaba pedir un préstamo". Este ejemplo subraya la importancia de entender la relación entre dos tokens que se encuentran lejanos entre sí, algo que el mecanismo de autoatención en los transformadores puede hacer muy efectivamente.

Figura 3. Arquitectura del Segundo módulo del ViT: Self-Attention

Se puede también plantear un ejemplo similar para el caso de los ViT. Se tienen dos imágenes que deben ser clasificadas de maneras distintas, pero que ambas tienen un patch muy similar o prácticamente igual. Por ejemplo, un patch que contiene un círculo rojo, puede corresponder al centro de la bandera de Japón o a un semáforo dependiendo del contexto. Aunque en ambos casos tenemos un círculo rojo, el significado de cada uno de estos es completamente distinto. Por esta razón, la capacidad del ViT para analizar relaciones globales entre los distintos patches es tan poderosa.

La Figura 3 muestra la representación gráfica del módulo de atención. Primero, la entrada de este módulo, que corresponde a la salida del módulo de Patch Embedding pasa por un proceso de normalización. Este proceso ajusta los datos del tensor de la imagen para que tengan un promedio de 0 y una varianza unitaria. Esta normalización se repite varias veces a lo largo de toda la arquitectura del ViT, y es fundamental para brindar estabilidad al modelo porque reduce la probabilidad de que los gradientes se vuelvan demasiado grandes o pequeños. Sin ella, los valores de los tensores podrían crecer o disminuir exponencialmente. En esta primera normalización del módulo de atención, se logra además que las características en la entrada tengan una escala consistente, al igual que las similitudes entre los vectores "Key" y "Query". A grandes rasgos, el proceso de normalización acondiciona la entrada para que el modelo de atención pueda procesarla de una manera más eficiente y precisa.

Posteriormente, la entrada pasa por una etapa que se asemeja mucho a una capa neuronal densa, en la cual se realiza una multiplicación EW entre esta entrada y un tensor de pesos entrenados, seguida de una suma EW con un bias entrenado. Básicamente, esta sección termina de acondicionar el tensor de entrada mediante una transformación lineal que termina de ajustar las activaciones antes de que pasen a las operaciones de atención. A continuación, el tensor de entrada se multiplica con tres matrices de pesos entrenados  $W_Q$ ,  $W_K$  y  $W_V$ , y se suman tres bias  $b_Q$ ,  $b_K$  y  $b_V$ , lo cual genera las matrices Key, Query y Vector K, Q y V, tal como se muestra en las ecuaciones 1, 2 y 3

$$Q = X * W_Q + b_c \tag{1}$$

$$K = X * W_K + b_K \tag{2}$$

$$V = X * W_V + b_V \tag{3}$$

Las matrices Query y Key se relacionan entre sí para que el modelo pueda la relación entre dos patches y cuál es la "intensidad" de esta relación, es decir, que tanto atiende un patch específico a otro. El tipo de relación entre patches se codifica en estas dos matrices. Al multiplicar la Matriz de entrada X por la matriz de pesos  $W_Q$ , el resultado se puede interpretar como una "pregunta" que busca entender como varía el significado de cada token en relación con los otros. Por otra parte, la

matriz K que se obtiene al multiplicar la entrada X por la matriz de pesos  $W_K$ , actúa como la "respuesta" o "llave" que responde a esa pregunta. Entender exactamente qué preguntas y respuestas codifican Q y K puede ser muy complejo para los humanos, sin embargo, como muchos otros modelos de Inteligencia artificial, esto realmente no es de nuestro interés. Solamente interesa que el modelo aprenda a través del entrenamiento y minimice la función de costo. Es algo similar a lo que sucede con las redes neuronales convolucionales, donde no siempre es fácil interpretar los mapas de activación, pero sabemos que estas activaciones son cruciales para dotar de "inteligencia" al modelo.

Para relacionar esta "pregunta" Q con su "llave" K se realiza una operación de producto punto entre las dos matrices. Cuanto mayor sea el resultado de esta multiplicación, más fuerte es la atención o la intensidad de la relación entre un token y otro, es decir, más relevante es cada palabra para actualizar el significado de las demás. Desde un punto de vista matemático, esto indica que los vectores Q y K se encuentran más alineados en el espacio multidimensional. Este resultado es luego normalizado por medio de la función "Softmax". Softmax es una función que convierte un conjunto de valores en un conjunto de probabilidades, donde cada valor se escala exponencialmente y luego se normaliza para que la suma total sea 1. Las ecuaciones 4 y 5 muestran los dos procesos matemáticos explicados en este párrafo, donde  $d_k$  representa la dimensión de los vectores Q y K y funciona como un factor de escalado para evitar que los valores resultantes sean demasiado grandes. I representa el vector de entrada a la función softmax y n es el número total de valores del vector.

$$KQ_{ij} = \frac{Q_i * K_j^T}{\sqrt{d_k}} \tag{4}$$

$$softmax(I_i) = \frac{\exp(I_i)}{\sum_{j=1}^{n} \exp(I_j)}$$

(5)

Una vez se ha computado la cantidad de atención que deben prestarse los tokens entre sí, el vector "Value", que se obtiene al multiplicar cada token por la matriz  $W_V$  generada en el proceso de entrenamiento. es el encargado de almacenar la información que se transmite de un token a otro.

Es decir, Value contiene las características o datos que el modelo utilizará para actualizar la representación de un token después de haber evaluado la importancia relativa de los demás tokens.

Desde un punto de vista en el espacio multidimensional, cada embedding representa un vector que será modificado para reflejar un token que incorpora el contexto de los demás tokens. La intensidad del cambio en la representación de este token es determinada por el producto punto KQ, mientras que la dirección de la modificación está influenciada por V. Para obtener el vector que se sumará al embedding original y así modificar su significado para incluir el contexto, se realiza una multiplicación entre el vector V y el resultado de aplicar "Softmax" a KQ. La ecuación 6 representa matemáticamente el proceso completo de atención. Esta ecuación se extrae directamente del paper original [6], y de hecho, las ecuaciones de la 1 a la 2 se derivan de 6

$$Attention(Q, K, V) = softmax\left(\frac{Q * K^{T}}{\sqrt{d_{k}}}\right) * V$$

(6)

El resultado del bloque de atención se suma al embedding original del patch, que en la Figura 3 está etiquetado como InpLL. De este modo, cada patch se modifica y se genera un nuevo vector que sigue codificando su significado original, pero que ahora también incorpora características del contexto global de la imagen. Antes de continuar con la explicación del próximo módulo del ViT, es importante mencionar que el mecanismo de atención no se limita a una sola operación, sino que se implementan múltiples cabezas de atención que se ejecutan en paralelo. Cada una de estas cabezas analiza distintas características de los patches de la imagen, lo cual permite que se capturen relaciones y contextos variados al mismo tiempo. Este enfoca mejora significativamente la precisión del ViT y su capacidad para captar al mismo tiempo el contexto general de la imagen y sus detalles específicos.

#### 2.1.2 Módulo de Perceptrón multicapa:

La red neuronal tipo perceptrón multicapa (MLP) es un estándar en la academia e industria de la inteligencia artificial y es implementada en la arquitectura de transformador a la salida del módulo de atención. Una MLP se compone de una capa de entrada, una de salida, y una o más capas ocultas. Estas capas se componen de varias neuronas tipo perceptrón, las cuales computan una suma ponderada de todas sus entradas, aplican esta suma ponderada por una función de

activación, y la salida de esta función corresponde a la salida de la neurona [7]. Las funciones de activación corresponden a "una función matemática que determina la salida de una neurona en una red neuronal, permitiendo la introducción de no linealidades en el modelo" [8].

Las redes neuronales MLP son densamente conectadas, lo cual significa que todas las neuronas de una capa están conectadas por medio de sus entradas con todas las neuronas de la capa anterior, y, del mismo modo, su salida se conecta con todas las neuronas de la siguiente [7]. Los parámetros entrenables de las MLP corresponden a los pesos del modelo, los cuales se utilizan para computar la suma ponderada de todas las entradas de una neurona, y los bias, los cuales se suman al resultado de esta suma ponderada. En la Figura 4 se muestra gráficamente las conexiones de una red neuronal MLP y en la ecuación 7 se representa matemáticamente este tipo de red neuronal densa. En esta ecuación, f representa la función de activación,  $w_{ij}^{(l)}$  representa la matriz de pesos que conecta la capa l con la capa l-1,  $a_i^{(l-1)}$  son las salidas o activaciones de la capa l-1 y  $b_i^l$  es el bias de la neurona j en la capa l.

Figura 4. Red neuronal MLP [9]

$$a_j^{(l)} = f(\sum_{i=1}^n w_{ij}^{(l)} a_i^{(l-1)} + b_j^{(l)}$$

(7)

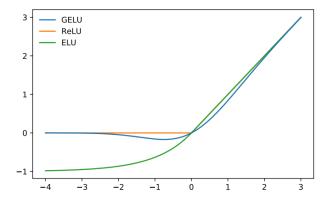

En el caso del ViT, la capa MLP tiene el objetivo de refinar la información que acaba de ser procesada por la capa de atención, la cual se etiqueta en la Figura 5 como InpFF. Una vez el módulo de atención ha captado el contexto de los patches, la MLP es capaz de captar características más complejas y abstractas. Esto se logra ya que la MLP introduce no linealidades al modelo por medio de la función de activación GELU. La función GELU es muy similar a la clásica ReLU, con la diferencia de que suaviza la transición entre valores positivos y negativos, lo que mejora la convergencia y el rendimiento en redes neuronales profundas [10]. La Figura 6 muestra la representación gráfica de la función GELU.

Figura 5. Tercer módulo del ViT: MLP

En el caso del ViT, la MLP consiste en una capa de normalización, y luego una red neuronal con dos capas ocultas, que se conectan entre sí por medio de la función de activación. En resumen, la capa MLP del ViT tiene una función muy similar a cualquier otra MLP que se utiliza en sistemas de visión: captar características espaciales de la imagen. La diferencia radica en que estas MLP utilizan como entrada un tensor que ya ha sido procesado por las capas de atención, lo que significa que contiene la información del patch individual pero también de su contexto.

Figura 6. Funciones GeLU, ReLU y ELU.

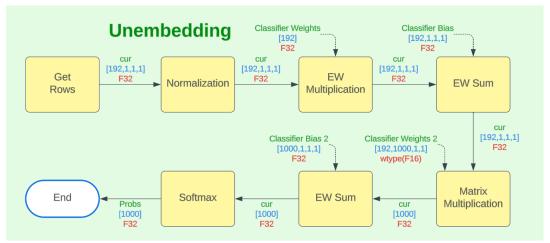

#### 2.1.4 Patch Unembedding

Finalmente, la salida de la MLP pasa al módulo de "Unembedding". Este módulo primero realiza la operación "get rows", la cual extrae del tensor de entrada la columna que representa el class token. Después de que la información ha sido procesada por varios ciclos de módulos de atención seguidos de MLP, el class token ya posee una idea global de todo el contexto de la imagen; codifica que simboliza cada uno de los patches así como la relación entre ellos.

A continuación, este class token es normalizado con el fin de obtener una distribución que tenga media de 0 y una desviación estándar unitaria. Al igual que las normalizaciones anteriores del ViT esto contribuye a la convergencia. Finalmente, el class token es escalado linealmente mediante dos operaciones EW, una multiplicación y una suma que se definen por parámetros entrenables de pesos y bias.

Luego, las siguientes operaciones se encargan de transformar la representación interna del token hacia un espacio en donde cada una de las dimensiones del vector corresponde a una clase específica de clasificación. La multiplicación matricial proyecta el token en el espacio de clases, y la adición del bias ajusta la predicción para cada clase. De esta manera, se obtiene un vector en el cual los valores más elevados representan probabilidades más altas de que la imagen original corresponda a la clase que representa este elemento del vector. Finalmente, se aplica la función Softmax, lo que genera un vector de probabilidades del 0 a 1 de estos valores.

Figura 7. Módulo Final del ViT: Unembedding

# 2.2 FPGA y High Level Synthesis

#### 2.2.1 FPGA

Las FPGA son dispositivos que consisten en arreglos de bloques de lógica reconfigurables conectados entre sí por medio de cables reprogramables. Estos bloques poseen grandes cantidades de Look-Up Tables (LUTs) y Flip-Flops, lo cual permite que la FPGA implemente cualquier tipo de función lógica o circuito secuencial que se desee. Las FPGAs modernas además incluyen bloques especializados como por ejemplo: multiplicadores, matrices de memoria RAM e incluso pequeños microprocesadores integrados [11].

Las FPGAs son altamente flexibles y reprogramables, debido a que permiten la reconfiguración de Hardware por medio de programación [1]. Por esta razón, las FPGAs son alternativas muy ventajosas para implementar unidades de procesamiento que efectúen tareas específicas y repetitivas. Al diseñar circuitos que no son de propósito general, sino que ejecutan operaciones específicas, se pueden obtener mejoras notables en términos de eficiencia energética y de tiempo de cómputo.

### 2.2.2 High Level Synthesis

El "High Level Synthesis" es una herramienta que permite la programación directa de módulos de Hardware por medio de lenguajes de alto nivel, como por ejemplo C o C++. Anteriormente, la programación de Hardware se debía realizar directamente por medio de lenguajes de descripción de hardware (HDL) como por ejemplo Verilog o VHDL. Estos HDLs al compilarse generan un archivo de lógica de transferencia de registros (RTL), los cuales describen como los datos se mueven entre registros y cuáles son las operaciones lógicas o aritméticas por medio de las cuales se transforman estos datos [1]. HLS permite a los programadores que tienen poco o nulo conocimiento en diseño de Hardware implementar redes neuronales en FPGAs a un nivel de abstracción mucho más elevado [12].

La reutilización de bloques en FPGAs ha sido posible por medio del uso de propiedades intelectuales (IP). Estos bloques de IP que normalmente están descritos en RTL tienen una gran desventaja, ya que deben ser optimizados manualmente si se desean implementar en un nuevo nodo, es decir, cada vez que estos bloques se ejecutan en una FPGA distinta, se deben de realizar muchos cambios para que el RTL sea compatible con el modelo específico de FPGA [13]. Las herramientas de HLS permiten solucionar este problema, ya que a la hora de compilar código de

alto nivel de abstracción, solo se debe especificar la plataforma objetivo y el archivo RTL para esta plataforma especifica es generado de manera automática [14].

### 2.3 Computación Aproximada y Cuantización

La computación aproximada es un conjunto de técnicas de cómputo que tienen como objetivo principal alcanzar una disminución en la cantidad de recursos energéticos y computacionales necesarios para ejecutar un algoritmo sin perder la precisión de este, o, perdiéndola en un nivel que no perjudique el objetivo fundamental del algoritmo. En lugar de buscar una ejecución completamente determinista, la computación aproximada tolera disminuciones en precisión y así logra un uso energético mucho más eficiente.

Tareas computacionales que han tomado mucha importancia en los últimos años como lo son el procesamiento de imágenes, audio y video, reconocimiento, minería de datos, y especialmente redes neuronales profundas, tienen la característica en común de que, con frecuencia, un resultado perfecto no es necesario, y un resultado aproximado menos es suficiente [15]. Las técnicas de computación aproximada se pueden aplicar en los distintos niveles de abstracción, a nivel de Software, a nivel de datos, a nivel de arquitectura e inclusive a nivel de circuitos. Algunas de las técnicas a nivel de datos son: Estructuras de datos aproximadas, muestreo de datos, compresiones y reducciones dimensionales y cuantización [16]. En la siguiente sección se profundiza sobre esta última técnica y su aplicación en DNN implementadas en FPGA.

La cuantización se refiere al "proceso de reducir la precisión de los datos numéricos en un programa, mapeando los valores a un conjunto más pequeño de valores discretos" [16]. La cuantización se utiliza comúnmente en modelos de aprendizaje automático para reducir los recursos computacionales y de memoria que requiere el modelo, lo cual es muy importante para la implementación de estos modelos en computación en el borde con recursos limitados. La mayoría de los estudios recientes relacionados a cuantización en el contexto de modelos de inteligencia artificial se han enfocado principalmente en el proceso de inferencia en lugar de en el de entrenamiento [16].

La elección del método de cuantización a implementar en modelos de aprendizaje automático conlleva siempre un equilibrio o "trade-off" entre la precisión de los cálculos y el uso de recursos computacionales y energéticos. La cuantización reduce significativamente los recursos computacionales al disminuir la cantidad de bits utilizados para representar los datos y parámetros del modelo. Sim embargo, este proceso conlleva un compromiso notable, ya que la reducción de la precisión en la representación de los operandos y operadores puede impactar la exactitud del modelo, y, por ende, su funcionalidad. Por ejemplo, utilizar valores enteros de baja precisión en 4 bits en lugar de la representación de punto flotante en 32 bits tiene la capacidad de reducir la latencia y el uso de memoria en un factor de hasta 16x [17].

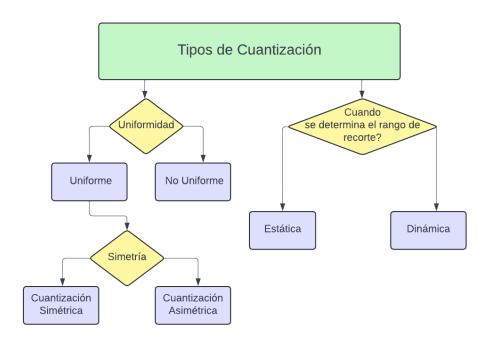

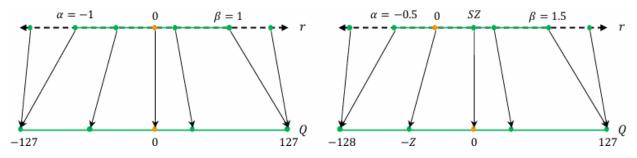

Figura 8. Representación gráfica de los tipos de cuantización

En aplicaciones en las cuales es necesario que los resultados sean altamente precisos, como por ejemplo, en sistemas médicos de detección de enfermedades o en sistemas de seguridad, se prefiere utilizar métodos de cuantización más precisos que por ende utilizan más recursos computacionales, como la cuantización de 16 bits entera (INT16) o en punto flotante reducido (bfloat16) o incluso en Punto flotante de 16 bits (FP16). Por otro lado, en las aplicaciones en las que la precisión no es crítica, y más bien se prefiere un bajo consumo energético, como por ejemplo dispositivos del internet de las cosas (IOT), sensores, o dispositivos embebidos de hogares inteligentes, se opta por cuantizaciones más agresivas como INT8, INT4 o inclusive en casos con requerimientos energéticos críticos cuantización binaria.

A continuación, se presenta la clasificación de categorías de cuantización. Estas categorías son utilizadas en la actualidad en el contexto de aceleradores de HW para modelos de DNN. En la Figura 8 se exponen esta clasificación de manera gráfica, según su división con respecto a simetría, momento de determinación del rango de recorte y uniformidad.

#### 2.3.1 Cuantización Uniforme

La cuantización uniforme toma un set de datos y mapea cada uno de estos a un espacio discreto en el cual cada uno de los valores son equidistantes entre sí. Este tipo de cuantización se implementa en aplicaciones en las cuales se busca simplicidad en los niveles de cuantización y esta simplicidad no afecta en gran medida a la calidad de la señal, como por ejemplo en ciertos sistemas de comunicación [17].

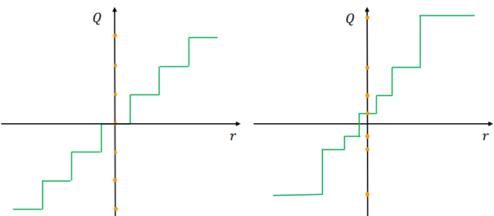

La cuantización uniforme es óptima para distribuciones en las cuales los valores se encuentran distribuidos de manera equitativa a través de todo el rango de datos. En estos casos, los niveles de cuantización equitativamente espaciados resultan ser suficientes para representar los datos sin causar grandes errores de cuantización [18]. En la Figura 9 se compara la cuantización uniforme y la no uniforme de manera gráfica. En este caso específico, la cuantización no uniforme que se ilustra posee mayor precisión cuando los valores a cuantizar se encuentrn más cercanos a cero.

Figura 9. Comparación gráfica entre cuantización uniforme (izquierda) y no uniforme (derecha) [17]

La cuantización uniforme se puede describir matemáticamente como se muestra en las ecuaciones 8 y 9. En la ecuación 8, x representa el valor flotante a cuantizar y Q es la función de

cuantización,  $\alpha$  es el valor mínimo del rango de recorte o "clipping range". Por otra parte, S representa el factor de escalado, que de hecho corresponde a la magnitud de los intervalos de cuantización, y Int corresponde a una función de redondeo. Además, en la ecuación 9,  $\beta$  es el valor mayor del rango de recorte y b representa el número de bits utilizados para la cuantización [17]. El punto cero o "zero point" Z se presenta en la ecuación 10, este se refiere al valor cuantizado que corresponde al valor cero real. Este valor toma especial importancia al explicar la cuantización simétrica y asimétrica en la siguiente sección

$$Q(x) = Int\left(\frac{x-\alpha}{S}\right) = Int\left(\frac{x}{S}\right) - Z \tag{8}$$

$$S = \left(\frac{\beta - \alpha}{2^b - 1}\right) \tag{9}$$

$$Z = Int\left(\frac{-\alpha}{S}\right) \tag{10}$$

El rango de recorte corresponde a el intervalo de valores dentro del que los datos se recortan, evitando que los valores atípicos o extremos que se encuentran fuera de ese intervalo sean representados en el proceso de cuantización. El rango de recorte es de hecho un parámetro del proceso de cuantización, es decir, el diseñador del algoritmo de cuantización elije estos valores como más convenga. En general, un rango de recorte más elevado permite que los valores extremos sean truncados, pero puede reducir la precisión en la representación de los valores intermedios y aumentar el uso de recursos computacionales.

### 2.3.2 Cuantización Simétrica y Asimétrica

Como se mencionó en el párrafo anterior, el rango de recorte es un parámetro del proceso de cuantización. Al proceso de elegir los valores de  $\beta$  y  $\alpha$  se le conoce como calibración. La práctica más común es utilizar el mínimo y máximo del set de datos como rango de recorte. En este caso, se produce una asimetría en el proceso de cuantización, ya que es probable que el valor de  $\alpha$  no sea igual al valor de  $-\beta$ . La cuantización asimétrica normalmente genera un rango de recorte más ajustado, y es comúnmente utilizada cuando los datos presentan asimetría, como por ejemplo en las activaciones a la salida de funciones como ReLU o Softmax [17].

Por otro lado, la cuantización simétrica se puede considerar como un caso "simplificado" de la cuantización asimétrica, en la cual el "zero point" Z corresponde a cero [19]. Este tipo de cuantización es más utilizado cuando los datos se distribuyen de manera simétrica, como por

ejemplo en distribuciones que poseen un comportamiento gaussiano. En este caso, el valor mínimo del rango de recorte  $\alpha$  sí es igual al valor de  $-\beta$ . La decisión más popular en este tipo de cuantización corresponde a elegir la magnitud de  $\beta$  y  $\alpha$  (que sería la misma) en función de la magnitud máxima de los valores del set de datos, tal como se muestra en la ecuación 11.

$$-\alpha = \beta = \max(|r_{max}|, |r_{min}|) \qquad (11)$$

La cuantización simétrica posee la ventaja de que, debido a que el valor Z siempre corresponde a cero, se obtiene una reducción del costo computacional de la inferencia en DNN, y además hace que la implementación en Hardware sea mucho más directa y sencilla. Al ser Z=0, en la ecuación 8 se observa que el HW solamente tendría que dividir el valor real entre el factor de escalado y redondear el resultado para obtener el valor cuantizado. De hecho, "el cálculo de pesos por medio de cuantización asimétrica incurre en un gasto extra de energía del 10% al 15%" [20]

En la Figura 10 se muestra la representación gráfica de la cuantización simétrica y asimétrica. En esta se puede apreciar como el valor de cero real es mapeado a cero en la cuantización simétrica y mapeado a Z en la cuantización asimétrica.

Figura 10. Mapeo de la cuantización simétrica (izquierda) y asimétrica (derecha) [17]

#### 2.3.3 Cuantización Dinámica y Estática

Otra división de los diversos tipos de cuantización se basa en cuando se determinan los parámetros de cuantización, como por ejemplo el rango de recorte, el punto cero o el número de bits. Cuando un modelo de inteligencia artificial es entrenado, sus pesos son determinados y no cambiarán de valor a la hora de utilizar el modelo para realizar inferencia. Por otro lado, las entradas del modelo de IA sobre las cuales se realiza la inferencia cambian constantemente, por lo que todas las activaciones del modelo también. En la cuantización estática, después de entrenar el

modelo, se determinan los parámetros de cuantización, y estos se mantienen estáticos al realizar la inferencia de distintas entradas [17].

Un método popular para realizar cuantización estática consiste en elegir una muestra de las posibles entradas del modelo, y obtener las activaciones de estas muestras. Estas activaciones se computan y, basándose en los valores de todas estas, además de en los valores de los pesos del modelo, se determinan los parámetros de cuantización. Esto significa que el punto cero, el rango de recorte y demás parámetros no varían cada vez que el modelo realiza inferencia a una entrada distinta. Este método resulta en menor exactitud comparado con la cuantización dinámica pero utiliza menos recursos computacionales.

Por otra parte, la cuantización dinámica ajusta de manera cíclica los parámetros de cuantización para cada una de las entradas. De manera automática, el modelo estudia la distribución de los valores de cada una de las entradas y optimiza los parámetros de cuantización para obtener el mayor grado de precisión posible [17]. En este caso, se incurre en una carga computacional adicional o "overhead" porque se requiere computo en tiempo real de las características estadísticas del set de datos, como por ejemplo de su mínimo, máximo, promedio y desviación estándar, y además optimizar los parámetros de cuantización.

Si se busca realizar la implementación del modelo de IA en HW programable como FPGA, esta técnica también introduce varios inconvenientes, como por ejemplo la necesidad de lógica adicional que puede aumentar significativamente la complejidad del diseño y requerir de más recursos lógicos como LUTs, Flip-Flops o DSPs, lo cual a su vez incrementa el consumo energético. También la dificultad de implementación aumenta porque hay que tomar en cuenta que se deben modificar los factores de escalado a medida que los datos atraviesan el pipeline de la FPGA.

#### 2.3.4 Cuantización no Uniforme

Como se mencionó brevemente en la sección 2.3.1, la cuantización no uniforme permite que los niveles de cuantización no estén espaciados de manera uniforme entre sí. El objetivo principal de este tipo de cuantización es utilizar niveles de cuantización más pequeños, lo cual equivale a un mayor nivel de precisión, en los rangos de la distribución que posean una mayor densidad de datos. Esto permite que, para una cantidad de bits específica, en comparación a la cuantización uniforme, la cuantización no uniforme capture de manera más precisa o leal la

distribución de datos original. La cuantización no uniforme es la ideal, por su misma naturaleza, para representar sets de datos que no poseen una distribución uniforme.

Matemáticamente, la cuantización no uniforme se puede describir mediante la ecuación 12. Esta ecuación es muy similar a la ecuación 8, con la importante diferencia de que el factor de escalado en este caso no es una constante, sino otra función que depende del valor a cuantizar "x". El valor más común para S(x) corresponde a una función logarítmica, sin embargo hay muchas funciones distintas que han sido implementadas con éxito para cuantizar un set de datos.

$$Q(x) = Int\left(\frac{x - \alpha}{S(x)}\right) \tag{12}$$

Como se ha mencionado en los párrafos anteriores, la cuantización no uniforme permite representar de manera más precisa cualquier set de datos que no tenga una distribución completamente uniforme, siempre y cuando la función de factor de escalamiento sea elegida de manera correcta. A pesar de esto, la cuantización no uniforme posee una desventaja muy notable. Este tipo de cuantización es difícil de implementar en HW de computación general, como las GPUs y las CPUs [17]. Esto se debe a que este tipo de HW está diseñado y optimizado para realizar taras que involucren operaciones uniformes y acceso regular a la memoria. La necesidad de realizar cálculos con datos no uniformes y acceso a memoria irregular introduce ineficiencias que son difíciles de tratar en este tipo de HW. La capacidad de paralelización y versatilidad de HW programable como FPGAs o ASICs pueden ser opciones viables para implementar este tipo de cuantización.

#### 2.3.4 PTQ (Post-Training Quantization) vs. QAT (Quantization Aware Training)

En todos los esquemas de cuantización explicados hasta el momento, se ha supuesto que este proceso ocurre después del entrenamiento de la red neuronal, lo cual se conoce como cuantización después del entrenamiento o PTQ por sus siglas en inglés. "Los algoritmos PTQ toman una red pre entrenada en punto flotante de 32 bits y la convierten directamente en una red de punto fijo sin necesidad del proceso de entrenamiento original. Estos métodos pueden o no requerir datos adicionales o necesitar un pequeño conjunto de calibración, que frecuentemente es de fácil acceso" [21].

Este método posee varias ventajas, como por ejemplo que el "overhead" o sobrecarga computacional es muy baja al compararse con QAT [17]. Además, este método es más práctico ya

que se puede aplicar en situaciones en las cuales el set de datos es limitado o no es de fácil acceso. En este caso, tampoco se necesita acceso al proceso de entrenamiento, lo cual permite que aunque el diseñador de la cuantización no tenga mucho conocimiento en el área del Deep learning, aun así pueda optimizar el modelo en términos de eficiencia.

Por otro lado, el QAT implementa el proceso de cuantización durante el entrenamiento de la red neuronal. En general, el algoritmo busca simular las condiciones de baja precisión numérica a las cuales se enfrentará la red neuronal desde el proceso de entrenamiento. Esto se logra al cuantizar los pesos y las activaciones del modelo en cada iteración de la propagación hacia adelante ("forward-pass") del proceso de entrenamiento. Es importante mencionar que aunque el "forward-pass" es cuantizado, la retro propagación del error se ejecuta con el nivel de precisión más elevado, que normalmente corresponde a F32, lo cual evita acumulaciones de error significativas y permite que el modelo ajuste los pesos con precisión [21].

De este modo, se calcula la función de pérdida en condiciones a las que se verá enfrentado el modelo en el proceso de inferencia. Los parámetros y el tipo de cuantización que utiliza el proceso de entrenamiento son las mismas que el modelo utilizará en el proceso de inferencia. Por ejemplo, si el modelo utilizará en la inferencia cuantización de 4 bits asimétrica con un rango de recorte de [1,5], el "forward-pass" del proceso de entrenamiento también será cuantizado haciendo uso de estos parámetros De manera intuitiva, este tipo de cuantización se puede interpretar como que el modelo "aprende" a manejar la reducción de precisión durante el proceso de entrenamiento [21].

En resumen, el QAT reduce de manera efectiva y notable el impacto de la baja precisión en el rendimiento de la red neuronal, lo cual es de suma importancia para aplicaciones en dispositivos con recursos limitados. Además, los modelos generados por QAT son más robustos a la cuantización, lo cual genera un rendimiento más predecible en el HW destino. Estas mejoras en la precisión, rendimiento y predictibilidad se obtienen a costas de un mayor costo de tiempo y recursos computacionales. El entrenamiento de la red neuronal requiere de mucho más tiempo ya que la cuantización debe ser simulada en cada iteración, lo cual puede ser perjudicial especialmente en modelos grandes. En términos generales, el QAT es una mejor opción en casos en los que tanto una alta eficiencia energética como una precisión muy similar al modelo sin cuantizar son fundamentales.

### 2.4 Estado del Arte y Cuantización en DNNs implementadas en FPGA

En esta sección se presenta un resumen del estado del arte en cuanto a las técnicas de cuantización empleadas para optimizar la eficiencia energética y preservar la precisión en redes neuronales profundas (DNN) implementadas mediante aceleradores de HW en FPGAs. Es importante destacar que este es un campo en constante evolución; desde 2019 hasta la fecha se han desarrollado nuevas técnicas de cuantización que alcanzan resultados cada vez más prometedores. Algunas de estas técnicas se combinan para obtener mejoras adicionales, impulsando futuras investigaciones. Las técnicas de cuantización abordadas en esta sección serán posteriormente comparadas entre sí, con el objetivo de diseñar una solución basada en una o varias de estas metodologías.

#### 2.4.1 Cuantización INT8

La cuantización de 8 bits corresponde a uno de los tipos de cuantización más comunes en optimización de DNN en FPGAs. Además, es una de las técnicas más sencillas de implementar [22] [23] [24]. Corresponde a una cuantización uniforme, tal como la presente en la ecuación 8. En esta cuantización, se transforman los datos de FP32 a enteros de 8 bits espaciados de manera homogénea. Normalmente, las implementaciones de este tipo de cuantización son PTQ y simétricas [22] [23] [24].

Según el estado del arte, el "secreto" para que la precisión de la red disminuya muy poco con respecto a su contraparte no cuantizada, corresponde en realizar un análisis estadístico de cada capa de la DNN, y según esta distribución de los datos, elegir un rango de recorte apropiado [22] [23] [24]. De esta manera, aunque toda la red se cuantiza utilizando 8 bits, el parámetro de cuantización del rango de recorte, y, en consecuencia, el factor de escalamiento, varían para cada tensor.

Un aspecto crucial que considerar en este tipo de cuantización, y en cualquier otra, son las posibles situaciones de desbordamiento que pueden ocurrir durante la inferencia al cuantizar el modelo. Una de las principales ventajas del formato FP32 es su capacidad, al ser una representación de punto flotante con muchos bits, para representar valores extremadamente grandes. Sin embargo, al cuantizar el modelo usando INT8, pueden surgir limitaciones significativas. Por ejemplo, en una cuantización de 8 bits, el valor máximo que se puede representar

es 127. Si en algún momento una operación suma 125 con 124, el resultado superará 127 y no podrá ser representado correctamente, generando un desbordamiento. Esto puede afectar la precisión y el comportamiento del modelo durante su ejecución.

Por esta razón, los diseños de cuantización implementan distintos algoritmos para lidiar con este tipo de situaciones. Por ejemplo, En el caso de [23] se utiliza saturación fija y saturación escalada. La saturación fija corresponde a que siempre que haya un desbordamiento, ese dato desbordado se recorta al límite del rango, lo cual correspondería en el ejemplo del anterior párrafo a representar el resultado de la suma como 127. La saturación escalada corresponde a multiplicar el valor que se encuentra en el rango por el valor más común del histograma, el cual normalmente se encuentra entre 0 y 1, lo cual generalmente causa que el valor vuelva a estar dentro de los rangos permitidos.

Al implementar una arquitectura que solamente utiliza enteros de 8 bits en todas las operaciones de las redes neuronales, se logran obtener mejoras notables en términos de eficiencia energética, velocidad de inferencia y utilización de recursos computacionales. Esto sucede porque se simplifica el flujo de datos en HW y se evitan conversiones adicionales que serían costosas en términos de latencia [23].

En [22] se obtiene una caída de la precisión en la tarea de clasificación de imágenes de solamente un 0.4% y en tareas de detección de prácticamente un 0%, El tiempo de inferencia disminuye notablemente y se alcanzan 70 inferencias por segundo (FPS) en la implementación en FPGA [22]. A modo de comparación, en la actualidad, CPUs de alta gama logran alcanzar entre 2 a 5 FPS [25]. Este estudio también concluye que, para poder mantener la precisión con cuantizaciones de aún una menor cantidad de bits, como INT2 o INT4, una cuantización QAT sería necesaria. Por otra parte, [23] obtiene una pérdida de precisión mínima en tareas de clasificación: un promedio de 1% para distintas DNN. Al mismo tiempo, se obtienen velocidades de 12 FPS. En [24] también se observa un aumento de la eficiencia energética.

#### 2.4.2 Cuantización de punto fijo