### INSTITUTO TECNOLÓGICO DE COSTA RICA ESCUELA DE INGENIERÍA EN ELECTRÓNICA

# TEC Tecnológico de Costa Rica

CONVERSIÓN ANALÓGICA-DIGITAL DE ALTA VELOCIDAD PARA ESPECTROSCOPIA POR IMPEDANCIA ELÉCTRICA

POR

ALVARO DIONISIO CAMACHO MORA

INFORME DE PROYECTO DE GRADUACIÓN PARA OPTAR POR EL TÍTULO DE INGENIERO EN ELECTRÓNICA CON EL GRADO ACADÉMICO DE LICENCIATURA

CARTAGO, JUNIO DEL 2016

## INSTITUTO TECNOLÓGICO DE COSTA RICA ESCUELA DE INGENIERÍA ELECTRÓNICA PROYECTO DE GRADUACIÓN ACTA DE APROBACIÓN

Defensa de Proyecto de Graduación Requisito para optar por el título de Ingeniero en Electrónica Grado Académico de Licenciatura Instituto Tecnológico de Costa Rica

El Tribunal Evaluador aprueba la defensa del proyecto de graduación denominado Conversión Analógica-Digital de Alta Velocidad para Espectroscopia por Impedancia Eléctrica, realizado por el señor Alvaro Dionisio Camacho Mora y, hace constar que cumple con las normas establecidas por la Escuela de Ingeniería Electrónica del Instituto Tecnológico de Costa Rica.

Miembros del Tribunal Evaluador

Ing. Hayden Anthony Phillips Brenes

Ing. Leonardo Sandoval Cascante

Profesor lector

Profesor lector

Dr.-Ing. Renato Rimolo Donadio

Profesor asesor

Cartago, Costa Rica, 17 de junio del 2016

Declaratoria de Autenticidad

Declaro que el presente Proyecto de Graduación ha sido realizado, en su totalidad, por

mi persona, utilizando y aplicando literatura referente al tema e introduciendo conocimientos

propios.

En los casos en que he utilizado material bibliográfico, he procedido a indicar las fuentes

mediante citas bibliográficas.

En consecuencia, asumo la responsabilidad total por el trabajo de graduación realizado

y por el contenido del correspondiente informe final.

Alvaro Dionisio Camacho Mora

Cédula: 304730491

Cartago, 17 de junio del 2016.

3

#### Resumen

La Espectroscopia por Impedancia Eléctrica es una técnica emergente con muy diversas aplicaciones, como la detección de enfermedades realizando un análisis en la impedancia de las células para conocer su morfología y así poder detectar cambios que signifiquen algún tipo de enfermedad en las personas. A través de la inyección de ondas armónicas de corriente y voltaje a diferentes frecuencias es que se puede crear un mapa de la impedancia de cada muestra. En el Instituto Tecnológico de Costa Rica se está diseñando un circuito integrado que implementa esta técnica bajo un barrido en frecuencia de hasta 10 GHz, empleando circuitos analógicos que logren el cometido de adquirir los datos de impedancia de las células. El sistema requiere convertir estas señales analógicas de impedancia a un formato digital que pueda ser comprendido por un computador que sea capaz de procesar los datos adquiridos.

Es por esto que, el presente documento explica el diseño de un convertidor analógico-digital (ADC) de 8 bits de resolución para una aplicación de alta velocidad. Este ADC es implementado en la tecnología CMOS 0.13 µm IBM 8RF y se basa en un flujo de diseño a la medida de un circuito integrado en el que se inicialmente se diseña la vista esquemática, después una implementación física del esquemático (layout) y concluyendo con simulaciones postlayout que ratifiquen el funcionamiento del ADC a nivel de implementación física.

La arquitectura del ADC propuesta está basada en una arquitectura Flash con interpolación y plegado que produce una reducción del hardware utilizado en un 87% menos comparadores, 75% menos latches y 48% menos resistencias en comparación con una arquitectura Flash tradicional que no implementa las técnicas de interpolación y plegado. El área utilizada por el ADC es de 0.39875 mm² y la potencia consumida es de aproximadamente 2.2447 mW. La velocidad de conversión de señales analógicas a digitales alcanzada por esta implementación es de 143 MS/s (Mega muestras por segundo).

Palabras claves: Espectroscopia por Impedancia Eléctrica, Convertidor Analógico Digital, Arquitectura Flash, Interpolación, Plegado, CMOS.

#### **Abstract**

Electrical Impedance Spectroscopy is an emergent technique with different applications, like the detection of diseases by performing an analysis of the cell impedance with the purpose of knowing its morphology, which enables the ability to detect changes that could mean some disease in the people. A map of impedance of each sample is created through the injection of harmonic waves of current and voltage in different frequencies. At the Instituto Tecnológico de Costa Rica a design of an integrated circuit that implemented this technique is being developed by using analog circuits that allow to get cell data impedance. It is required then to convert these signals to a digital in order to process the signal information with conventional computer systems.

It is for this reason that in this work the design of an 8-bit analog-digital converter (ADC) for a high-speed application is addressed. This ADC is implemented in 0.13 µm IBM8RF CMOS technology. Furthermore, it is based in an integrated circuit custom design flow, that initially is designed in the schematic, then to proceed with the physical implementation of the schematic (layout), and it concludes with a post-layout simulation to evaluate the performance of the ADC.

The ADC architecture proposed it is based on a Flash architecture that uses interpolation and folding techniques. By using these techniques, the hardware reduction was optimized in an 87% less of comparators, 75% less of latches and 48% reduction of resistors when compared to a traditional Flash architecture. The area used for the ADC is 0.39875 mm<sup>2</sup> and the power consumption calculated is of an approximate of 2.2447 mW. The conversion speed of analog to digital signal obtained by this design has been 143 MS/s.

Key words: Electrical Impedance Spectroscopy, analog-digital converter, flash architecture. Interpolation, Folding, CMOS.

#### Dedicatoria

A mis padres Alvaro y Maricel, primeramente, por darme la vida y después hacerme la persona que soy hoy. Enseñarme los valores de la responsabilidad, honestidad, esfuerzo y perseverancia que sin estos valores tan importantes alcanzar este objetivo tan importante en mi vida hubieran sido imposibles. Además de ser ese soporte cuando más lo he necesitado.

A mis hermanos Michael, José y Catherine que siempre en los momentos difíciles me han ayudado a salir adelante.

Y a toda mi familia, que siempre me han apoyado a seguir adelante y poder alcanzar este objetivo en mi vida.

A todos ellos, gracias.

#### Agradecimiento

Al Dr.-Ing. Renato Rimolo Donadio, por su guía y ayuda por más de un año desde que empecé a ser su asistente y más aún en este semestre que realicé el proyecto de graduación.

A mis amigos del TEC que en estos 5 años y medio de carrera hicieron que cada momento valiera la pena al crear experiencias inolvidables. Sin ellos llegar a este objetivo de presentar este proyecto de graduación hubiese sido más complicado.

Y a todas las personas que de alguna u otra forma han contribuido a llegar a este objetivo final que es presentar este proyecto de graduación.

## Índice

| Lista de Acı                     | rónimos                                                       | 13 |

|----------------------------------|---------------------------------------------------------------|----|

| Capítulo 1:                      | Introducción                                                  | 14 |

| 1.1 Or                           | ganización del Documento                                      | 16 |

| Capítulo 2:                      | Marco Teórico                                                 | 17 |

| 2.1. Espe                        | ctroscopia por Impedancia Eléctrica                           | 17 |

| 2.2 Conv                         | ertidor Analógico-Digital                                     | 21 |

| 2.2.1.                           | Fundamentos de Conversión Analógica-Digital                   | 21 |

| 2.2.2.                           | Otros Conceptos                                               | 25 |

| 2.3 Flujo                        | de Diseño IC                                                  | 26 |

| 2.3.1.                           | Tecnología de Diseño                                          | 26 |

| 2.3.2.                           | Metodología de Diseño                                         | 29 |

| Capítulo 3:                      | Propuesta de Diseño                                           | 32 |

| 3.1. Ar                          | quitecturas de ADCs de Alta Velocidad de Conversión           | 32 |

| 3.1.1.                           | Arquitectura Flash                                            | 34 |

| 3.1.2.                           | Registro de Aproximaciones Sucesivas (SAR)                    | 36 |

| 3.1.3.                           | Interpolación y Plegado (Folding and Interpolation)           | 37 |

| 3.2. Es                          | cogencia de la Arquitectura ADC                               | 41 |

| 3.2.1.                           | Criterios de escogencia                                       | 41 |

| 3.2.2. Análisis de arquitecturas |                                                               | 42 |

| Capítulo 4 I                     | Diseño de la Arquitectura                                     | 44 |

| 4.1. Mo                          | ódulos de la Arquitectura                                     | 46 |

| 4.1.1.                           | Escalera Resistiva (Resistive Ladder)                         | 46 |

| 4.1.2.                           | Selección de los voltajes de referencia para los comparadores | 49 |

| 4.1.3.                           | Circuito Muestreador/Retenedor                                | 61 |

| 4.1.4.                           | Comparación                                                   | 63 |

| 4.1.5.                           | Decodificador                                                 | 80 |

| 4.1.6.                           | Banco de Inversores                                           | 83 |

| 4.2. Ar                          | quitectura completa del ADC                                   | 86 |

| Canítulo 5 ·                     | Presentación y Discusión de Resultados                        | 92 |

| Capítulo 6 : Conclusiones y Recomendaciones                                 |     |

|-----------------------------------------------------------------------------|-----|

| Bibliografía                                                                | 100 |

| Anexo 1: Tabla con valores de referencia de salida de la escalera resistiva | 103 |

## **Índice de Figuras**

| Figura 2.1. Respuesta en frecuencia para la permitividad de una célula. Adaptada de [9]           | 18         |

|---------------------------------------------------------------------------------------------------|------------|

| Figura 2.2. Diagrama simplificado de un sistema de Espectroscopia por Impedancia Eléctrica.       | Adaptada   |

| de [10]                                                                                           | 20         |

| Figura 2.3. Bloques básicos de un Convertidor Analógico-Digital                                   | 21         |

| Figura 2.4. Esquema de funcionamiento del S/H. Adaptada de [3]                                    | 22         |

| Figura 2.5. Cuantización de una señal analógica. Adaptada de [3]                                  | 24         |

| Figura 2.6. Muestra el Error de Cuantización. Adaptada de [3]                                     | 24         |

| Figura 2.7. Stack-up utilizado para la implementación Física                                      | 27         |

| Figura 3.1. Gráfico de velocidad de conversión versus bits de resolución para diferentes topo     | logías de  |

| ADC. Adaptada de [1]                                                                              | 33         |

| Figura 3.2. Estructura típica de un ADC Flash. Adaptado de [2]                                    | 35         |

| Figura 3.3. Arquitectura SAR ADC. Adaptada de [3]                                                 | 36         |

| Figura 3.4. Interpolación entre la salida de dos preamplificadores. Adaptado de [4]               | 38         |

| Figura 3.5. Implementación de la interpolación. Adaptado de [5]                                   | 39         |

| Figura 3.6. (a) Características de entrada/salida de dos preamplificadores, (b) suma de las carac | terísticas |

| en (a). Adaptado de [4]                                                                           | 40         |

| Figura 3.7. Aplicación de la técnica de plegado. Adaptado de [5]                                  | 40         |

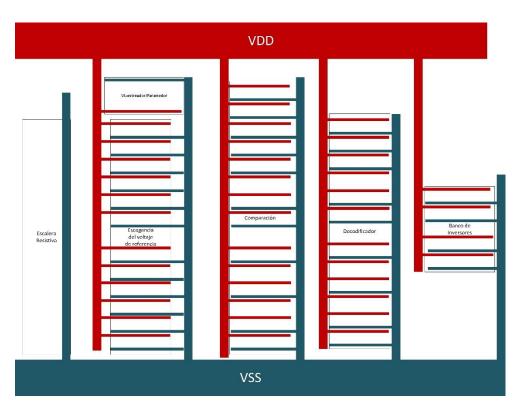

| Figura 4.1. Arquitectura ADC propuesta                                                            | 44         |

| Figura 4.2. Diagrama esquemático de la escalera resistiva. Adaptada de [5]                        | 47         |

| Figura 4.3. Muestra una parte del layout de la escalera resistiva                                 |            |

| Figura 4.4. Muestra la simulación postlayout de la escalera resistiva                             | 49         |

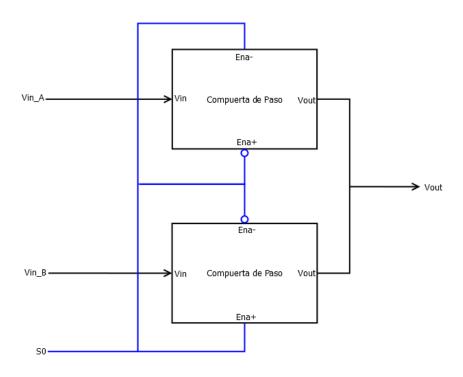

| Figura 4.5. Esquemático de la compuerta de paso                                                   | 50         |

| Figura 4.6. Layout de la compuerta de paso                                                        | 51         |

| Figura 4.7. Diagrama esquemático del MUX2x1                                                       | 52         |

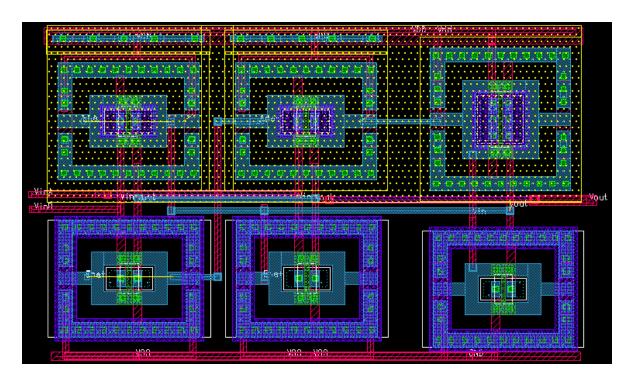

| Figura 4.8. Muestra la vista de layout para el MUX2x1                                             | 53         |

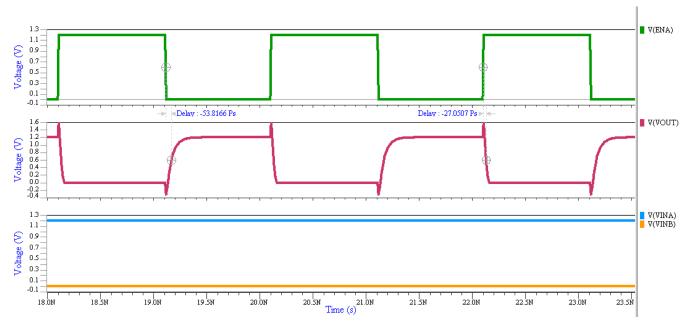

| Figura 4.9. Simulación postlayout del MUX2x1                                                      | 53         |

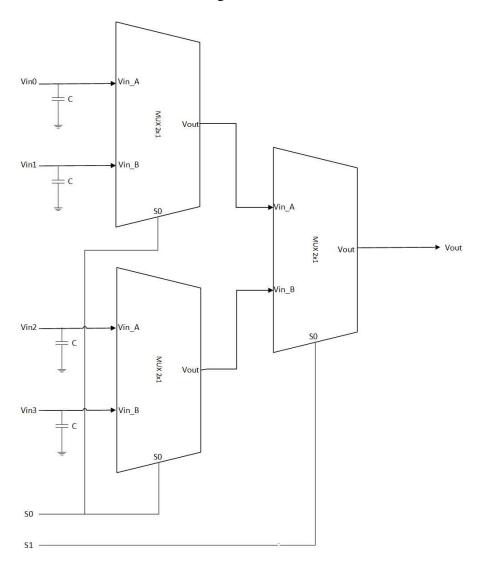

| Figura 4.10. Diagrama esquemático para el MUX4x1                                                  | 54         |

| Figura 4.11. Muestra el layout para el MUX4x1                                                     | 56         |

| Figura 4.12. Simulación postlayout del MUX4x1                                                     | 57         |

| Figura 4.13.Diagrama esquemático de la macrocelda de selección de voltaje de referencia           | 59         |

| Figura 4.14. Sección del layout de la macrocelda de selección de voltajes de referencia           | 60         |

| Figure 4.15. Diagrama esquemático del circuito muestreador/retenedor                              | 62         |

| Figura 4.16. Simulación postlayout de la Compuerta de Paso para S/H                               | 62         |

| Figura 4.17. Implementación física de la compuerta de paso para S/H                               | 63         |

| Figure 4.18. Esquemático de la compuerta NAND                                                     | 63         |

| Figura 4.19. Implementación física para la compuerta NAND                                         | 64         |

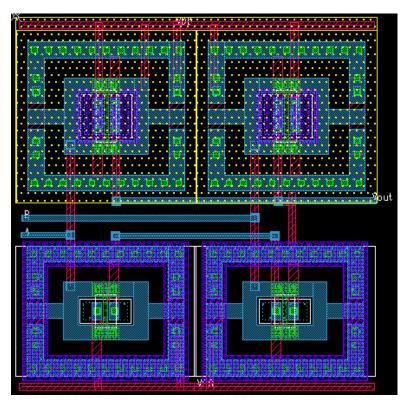

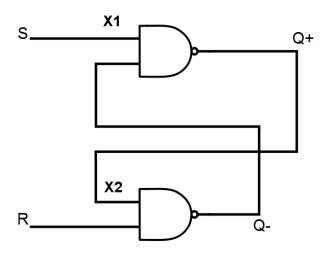

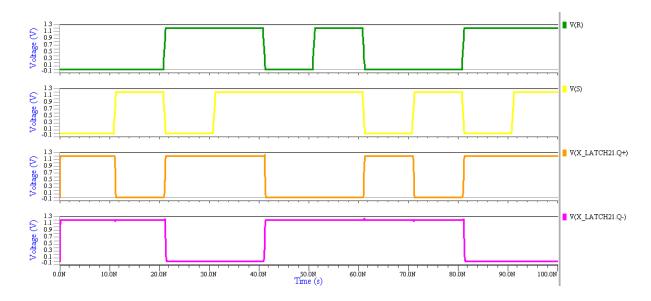

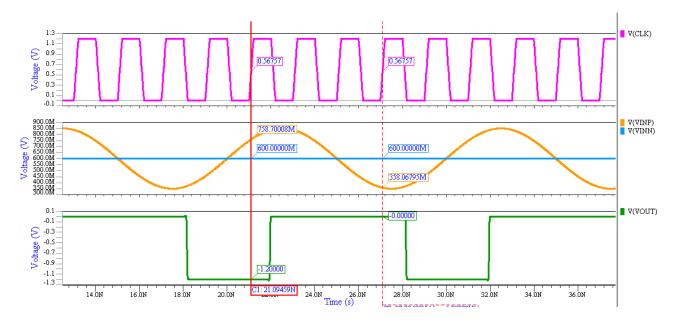

| Figura 4.20. Esquemático del latch                                                                | 65         |

| Figura 4.21. Simulación postlayout del latch                                                      | 66         |

| Figura 4.22. Implementación física del Latch                                                      | 66         |

| Figura 4.23. Esquemático del inversor                                                             | 67         |

| Figura 4.24. Implementación física del Inversor Lógico                                            | 68         |

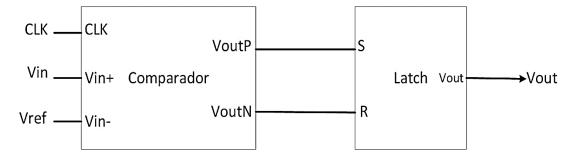

| Figura 4.25 Esquemático del comparador                                                            | 69         |

| Figura 4.26. Implementación física del comparador                              | 71 |

|--------------------------------------------------------------------------------|----|

| Figure 4.27. Esquemático del comparador-latch                                  | 72 |

| Figura 4.28. Implementación física del comparador-latch                        | 72 |

| Figura 4.29. Simulación postlayout del comparador-latch                        | 73 |

| Figure 4.30. Esquemático comparador $\frac{\text{Vref}}{2}$                    |    |

| Figura 4.31. Implementación física del comparador $\frac{\text{Vref}}{2}$      | 74 |

| Figura 4.32. Simulación del comparador Vref                                    | 75 |

| Figura 4.33. Esquemático de la interpolación                                   | 76 |

| Figure 4.34. Esquemático macrocelda de comparación                             | 77 |

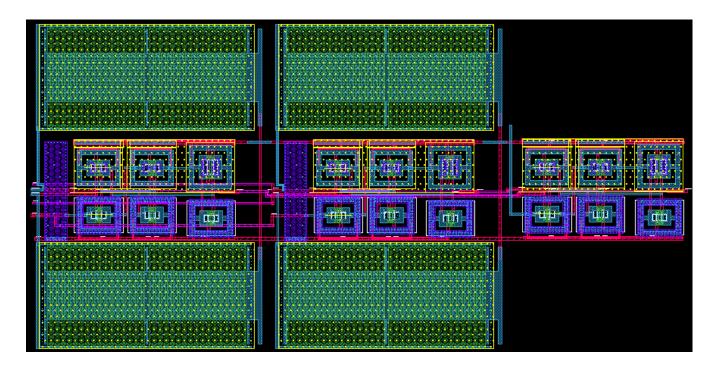

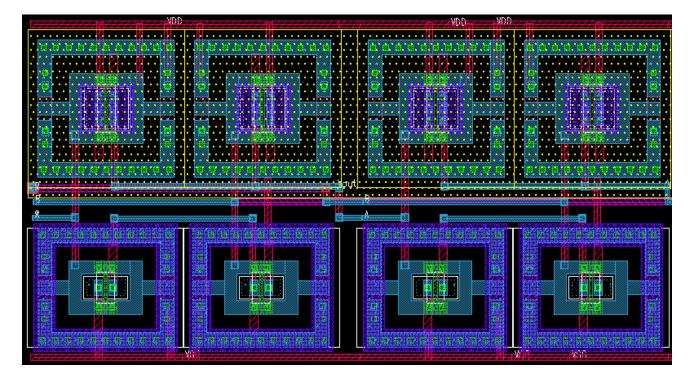

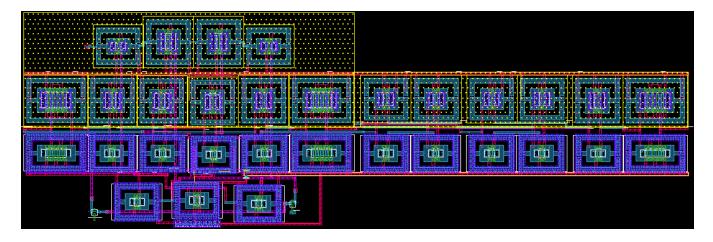

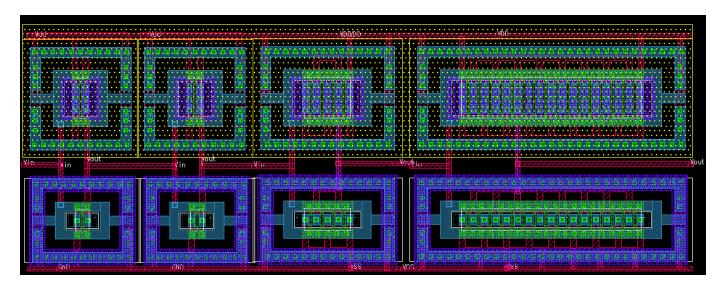

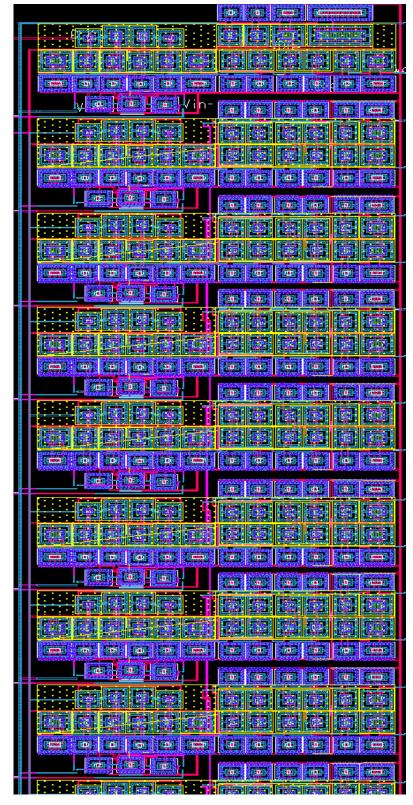

| Figura 4.35. Implementación física de una sección de la etapa de comparación   | 79 |

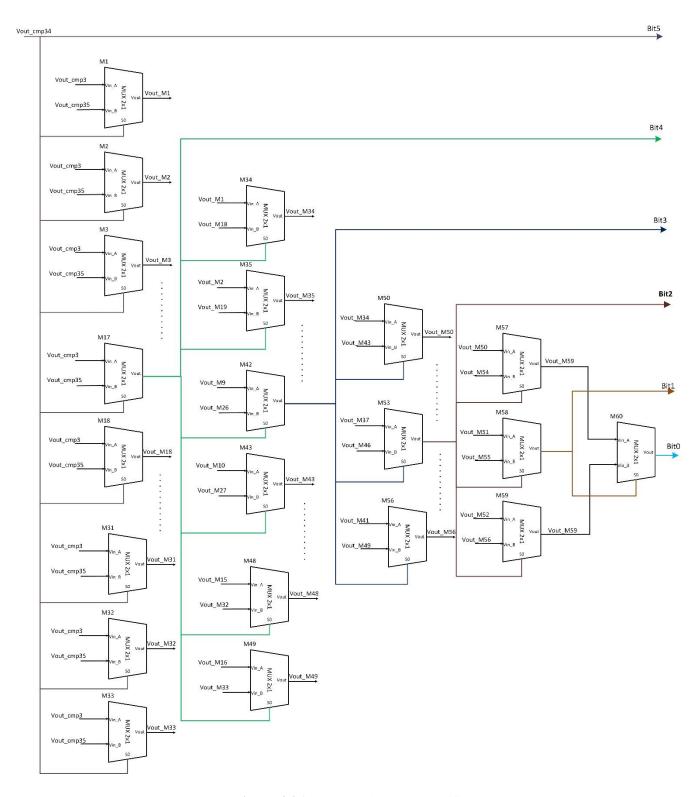

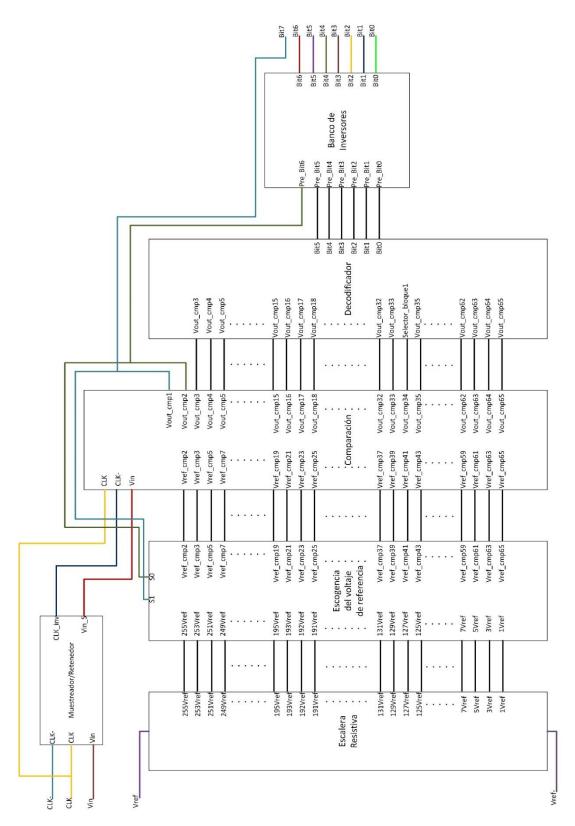

| Figure 4.36. Esquemático del decodificador                                     | 81 |

| Figura 4.37. Porción de la implementación física del decodificador             | 82 |

| Figura 4.38. Simulación del decodificador                                      | 83 |

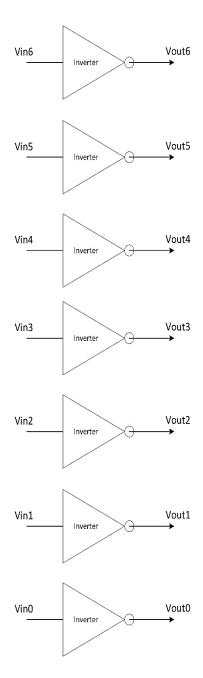

| Figure 4.39. Esquemático del banco de inversores                               | 84 |

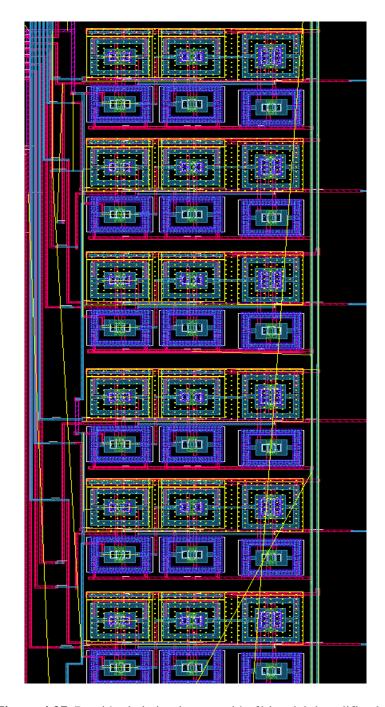

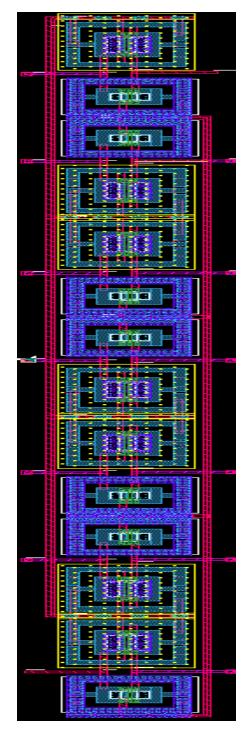

| Figura 4.40. Implementación física del banco de inversores                     | 85 |

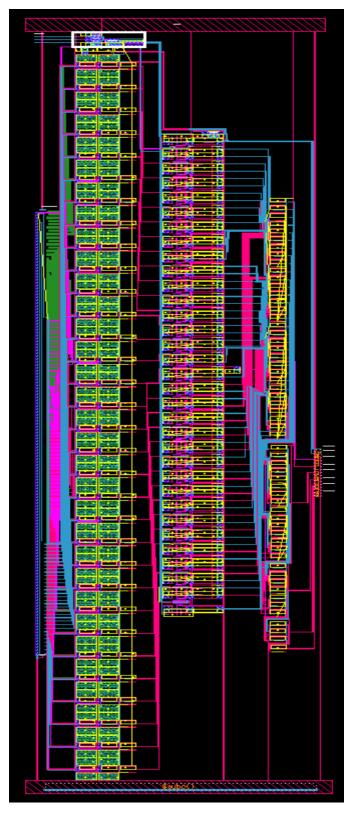

| Figure 4.41. Esquemático de la arquitectura de ADC implementada                | 87 |

| Figura 4.42. Implementación física del ADC                                     |    |

| Figure 4.43. Distribución de energía en el layout del ADC                      | 90 |

| Figura 4.44. Muestra el proceso de llenado para un sector de la implementación |    |

| ADC                                                                            |    |

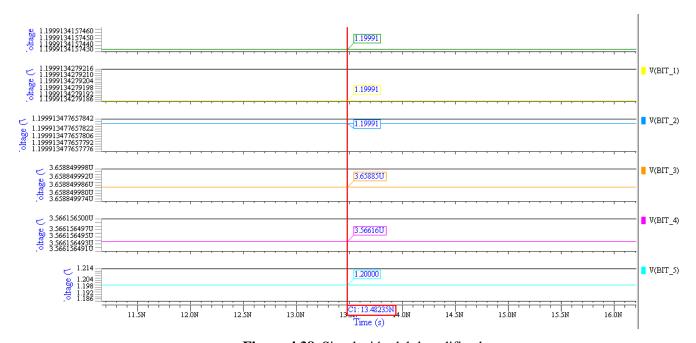

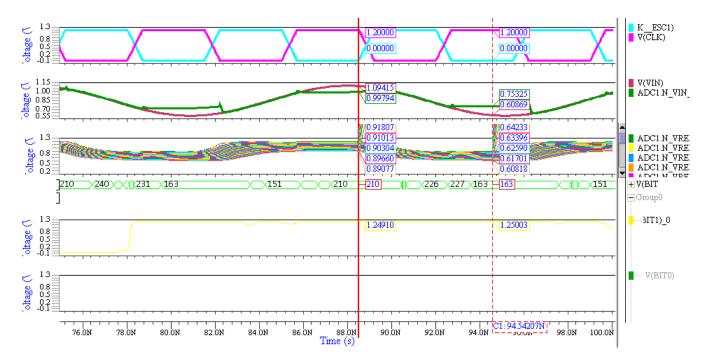

| Figura 4.45. Simulación de la arquitectura completa                            | 93 |

## **Índice de Tablas**

| Tabla 2.1. Descripción de las capas utilizadas en la implementación física           | 28 |

|--------------------------------------------------------------------------------------|----|

| Tabla 4.1. Tabla de verdad para el MUX4x1                                            | 56 |

| Tabla 4.2. Dimensiones de los transistores para la Compuerta NAND.                   |    |

| Tabla 4.3. Tabla de verdad del Latch                                                 | 65 |

| Tabla 4.4. Dimensiones de los transistores del comparador.                           | 70 |

| Tabla 5.1. Diferencias entre arquitectura Flash tradicional y arquitectura propuesta | 95 |

| Tabla A-1. Contiene los voltajes de referencia generados en la escalera resistiva    |    |

#### Lista de Acrónimos

**ADC** Convertidor Analógico-Digital (Analog-Digital Converter)

**CMOS** MOS Complementario (Complementary MOS)

DAC Convertidor Digital-Analógico (Digital-Analog Converter)DRC Revisión de las Reglas de Diseño (Design Rules Checking)

**EIE** Espectroscopia por Impedancia Eléctrica

**FET** Transistor de Efecto de Campo (Field-Efect Transistor)

**FSR** Rango de escala completa (Full-scale range)

IC Circuito Integrado (Integrated Circuit)

ITCR Instituto Tecnológico de Costa Rica

L Largo del transistor (Transistor Length)

**LSB** Bit menos significativo (Least significant bit)

LVS Layout versus Esquemático

LVTNFET NFET de bajo voltaje de umbral (Low Voltage Threshold NFET)LVTPFET PFET de bajo voltaje de umbral (Low Voltage Threshold PFET)

MOS Metal Oxido Semiconductor (Metal Oxide Semiconductor)

MOSIS Servicio de Implementación MOS (MOS Implementation Service)

**NFET** FET tipo N

NMOS MOS tipo N

**PEX** Extracción de Parasíticos (Parasitic Extraction)

**PFET** FET tipo P**PMOS** MOS tipo P

**RC** Resistivo-Capacitivo

**RF** Radiofrecuencia

**ROM** Memoria de solo lectura (read-only memory)

**SAR** Registro de Aproximaciones Sucesivas (Successive approximation register)

**S/H** Muestreo y Retenedor (Sample-and-Hold)

**VLSI** Integración a muy gran escala (Very-Large-Scale-Integration)

W Ancho del transistor (Transistor Width)

#### Capítulo 1 : Introducción

La espectroscopia por Impedancia Eléctrica (EIE), es una técnica de la que se pueden derivar gran cantidad de aplicaciones entre las que destacan la caracterización de materiales, dispositivos de estado sólido, corrosión de los materiales, fuentes de potencia electroquímica (baterías, celdas de combustible) [6]. Al tratarse de una técnica que tiene diferentes aplicaciones, recientemente se está empezando a utilizar como una forma de detección de enfermedades analizando muestras de células o tejidos bajo las premisas de ser una aplicación no invasiva y de bajo costo que ha sido posible con la miniaturización de los circuitos electrónicos en circuitos integrados.

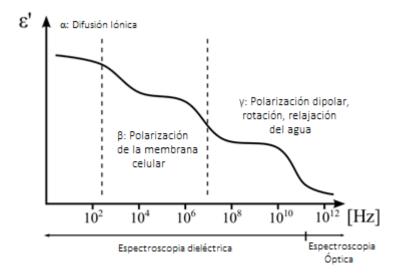

La EIE se basa en la respuesta en frecuencia obtenida del tejido que este bajo análisis, en el cual se buscan características que demuestren cambios morfológicos en la composición del tejido y las células que lo constituyen como lo son: hidratación, volumen de fluidos corporales, volumen intracelular y extracelular, porcentaje de grasa, entre otras [24]. Además, se ha determinado con el estudio de la dinámica molecular que envuelve esta técnica que se tiene un ancho de banda para la aplicación de la EIE de 10<sup>-6</sup> Hz a 10<sup>12</sup> Hz, sin embargo, existe un límite para la implementación con circuitos eléctricos que ronda los 10<sup>11</sup> Hz, después de este límite se deben utilizar circuitos ópticos para poder implementar la espectroscopia.

Bajo este panorama es que en la Escuela de Ingeniería en Electrónica del Instituto Tecnológico de Costa Rica se está realizando la implementación de un circuito integrado que tendrá como objetivo principal la medición de impedancia eléctrica en células que puedan presentar algún riesgo o modificación en su comportamiento que indique la presencia de cierta enfermedad, detectable bajo la excitación de las células con señales armónicas de corriente y voltaje de hasta 10 GHz.

Este circuito integrado está compuesto por varios módulos o subcircuitos que permiten un funcionamiento acorde con lo deseado. Uno de estos módulos logra la comunicación con un computador que permitirá postprocesar la información obtenida del tejido que se está analizando, convirtiendo de un formato analógico a uno digital que podrá ser entendido por un

computador. Este submódulo es un convertidor analógico-digital (ADC) que dentro de sus principales características esta que debe ser un convertidor con alta velocidad de conversión que permita una sinergia con los otros módulos del sistema.

La conversión de señales es un tema que concierne a aquellos diseñadores que trabajan con sistemas en señal mixta, es decir, señales que están en el dominio analógico y digital, y que dadas las características de los sistemas se debe tener una comunicación o transferencia de datos entre ambos dominios. En cuanto a los convertidores analógicos-digitales, convierten una señal del dominio analógico o continuo a un dominio discreto o digital que es el dominio en el que trabajan los computadores y es aquí donde se presenta la importancia de este tipo de conversión, pues se realiza esta conversión para que la señal analógica pueda ser entendida y procesada por un computador. Muchos autores han realizado implementaciones de ADCs de alta velocidad, pero dada su complejidad, se limitan a implementaciones que no sobrepasan los 5 bits de resolución [7] [8] [5].

En este documento se presenta el proceso de diseño de un ADC a nivel de circuito integrado con una resolución de 8 bits que sea capaz de convertir señales analógicas a digitales con la velocidad más alta que permite la tecnología CMOS 0.13 µm IBM8RF. Como antes ha sido mencionado, la implementación de un ADC de 8 bits, presupone un reto mayor comparada a otras implementaciones en cuando a velocidad final de conversión, área y potencia consumida.

El ADC se diseñará e implementará siguiendo un esquema típico que se sigue en el diseño a la medida (custom IC design) en microelectrónica, iniciando con un análisis de topologías de ADCs de alta velocidad que cumplan con el requerimiento de 8 bits de resolución. Una vez concluido el análisis de topologías a nivel teórico, se pretende abordar la implementación en esquemático de la arquitectura que concluirá cuando se tenga un diseño funcional de la arquitectura en cuestión.

Lo anterior permitirá avanzar a la etapa de la implementación física o layout, en donde se construirá la etapa física de la arquitectura escogida, en la que se ofrecerá un modelo real tanto de funcionamiento, área y potencia consumida para la arquitectura antes escogida.

Por lo tanto, este documento pretende conducir al lector por todo el proceso de diseño de este ADC, llevándolo desde las cuestiones teóricas que envuelven el entorno y desarrollo de este proyecto como lo son los pormenores de la técnica de Espectroscopia por Impedancia Eléctrica, cuestiones teóricas de las arquitecturas ADC y las diferentes etapas de diseño e implementación, sin olvidar la presentación de resultados obtenidos con la arquitectura ADC implementada.

#### 1.1 Organización del Documento

El presente documento se dividirá en capítulos para que el lector tenga una mayor fluidez en la lectura de este informe final de proyecto de graduación.

El capítulo 2 estará enfocado en un análisis teórico de los principales conceptos que involucra este proyecto como lo es la Espectroscopia por Impedancia Eléctrica, conceptos de interés para el entendimiento de los circuitos convertidores de señales analógicos a digital y posteriormente se ofrecerán detalles sobre la metodología que se siguió en el proceso de diseño.

El capítulo 3 mostrará en sus primeros apartados un análisis de las principales arquitecturas que se utilizan en la actualidad para implementar ADCs de alta velocidad, un análisis teórico de dichas arquitecturas y los criterios que llevaron a la escogencia de la arquitectura.

Posteriormente, en el capítulo 4 se ofrecerán detalles sobre el diseño a nivel de esquemático de cada uno de los submódulos que comprende la arquitectura escogida junto con los detalles sobre la implementación del diseño del ADC en su etapa física (layout).

En el capítulo 5 de este documento se ofrecerán detalles sobre la presentación y discusión de resultados arrojados por la arquitectura final del ADC.

Finalmente, en el capítulo 6 de este documento se presentarán las conclusiones a las que se han llegado con el diseño planteado y las recomendaciones pertinentes de este proyecto de graduación.

#### Capítulo 2 : Marco Teórico

#### 2.1. Espectroscopia por Impedancia Eléctrica

La técnica de EIE se basa en la excitación con ondas electromagnéticas de cierto tejido o grupo de células para obtener un espectro en frecuencia del comportamiento de la impedancia eléctrica de dicha muestra [21]. Estando bajo el efecto de un campo eléctrico  $\vec{E}$ , se produce un flujo eléctrico  $\vec{D}$  en el material bajo estudio, resultando en:

$$\vec{D} = \varepsilon^* \varepsilon_0 \vec{E} \tag{2.1-1}$$

Donde  $\varepsilon_0$  es la permitividad en el vacío y  $\varepsilon^*$ se define como la permitividad compleja, definida como:

$$\varepsilon^* = \varepsilon'(\omega) - i \varepsilon''(\omega) \tag{2.1-2}$$

Donde  $\mathcal{E}''$  representa las pérdidas y  $\mathcal{E}'$  es la permitividad del material, que, a su vez será la variable en importancia pues tiene una variación con la frecuencia que permitirá determinar la zona de frecuencia en la que se encuentra el material y poder determinar sus características y si existe alguna alteración. El  $\vec{E}$  aplicado, también inducirá una densidad de corriente  $\vec{J}$  definida como:

$$\vec{J} = \sigma^* \vec{E} \tag{2.1-3}$$

En la que se define  $\sigma^*$  como la conductividad compleja. En la figura 2.1 se puede observar dichas zonas  $\alpha$  (difusión iónica),  $\beta$  (Polarización de la membrana celular) y  $\gamma$  (Polarización dipolar, rotación y relajación del agua). Cada una de las zonas presenta diferentes características que pueden ser asociadas a anomalías o comportamientos normales en las células del tejido en análisis.

Figura 2.1. Respuesta en frecuencia para la permitividad de una célula. Adaptada de [9].

Si se hace un modelado de la célula como un circuito RC [24], se puede expresar la impedancia equivalente como:

$$Z_{eq} = R - jX_{\mathcal{C}} = \frac{A}{\sigma \cdot l} + j\frac{l}{\omega \varepsilon' \epsilon_0 A}$$

(2.1-4)

Si a la muestra bajo análisis se le aplica una señal armónica de voltaje con una frecuencia  $\omega$ ;  $\varepsilon'$  y  $\sigma$  se pueden determinar de la siguiente forma:

$$\varepsilon' = \frac{I_{imag} \cdot l}{U \cdot A \cdot \omega \cdot \varepsilon_0} \tag{2.1-5}$$

$$\sigma = \frac{I_{real} \cdot A}{U \cdot l} \tag{2.1-6}$$

Donde  $I_{real}$  es la componente real de la corriente aplicada,  $I_{imag}$  la componente imaginaria de la corriente aplicada, U la magnitud del voltaje, l el largo de la muestra y A el área transversal de la muestra [21].

Ahora bien, la recuperación de datos obtenidos como respuesta de la excitación realizada al tejido bajo análisis, se debe hacer en un computador con el fin de almacenar la información y realizar un procesamiento efectivo de los datos, donde se pueda determinar qué características poseen las células analizadas y con esto determinar si tienen un estado normal, si poseen algún tipo de enfermedad o mutación que, si es detectada en etapas tempranas, pueda salvar vidas o prevenir efectos que agraven la calidad de vida de las personas.

Ahora bien, en el proyecto de investigación que se está desarrollando actualmente en el Instituto Tecnológico de Costa Rica sobre Espectroscopia por Impedancia Eléctrica se pretende diseñar un circuito integrado capaz de hacer mediciones de impedancia sobre múltiples canales en un rango de barrido de frecuencia hasta 10 GHz para obtener un espectro con suficiente información de las zonas de penetración celular (Figura 2.1), que permita tener datos con suficiente precisión y confiabilidad para brindar un diagnostico aceptable sobre lo que le suceden a las células que están siendo analizadas.

Los presupuestos de área que se cuentan para implementar el sistema de Espectroscopia por Impedancia Eléctrica son limitados. Por lo que realizar un módulo de conversión analógica-digital permite optimizar el uso del área disponible, reducir el consumo de potencia al no tener que realizar un procesamiento nativo por métodos analógicos que dificultaría el tratamiento de los datos pues no se tienen las facilidades de software que ofrecería un computador, aumentaría el área destinada para el chip por tener que incluir etapas de procesamiento y se perdería la capacidad de almacenaje y portabilidad de la información obtenida en el barrido de frecuencia hecho al tejido bajo análisis.

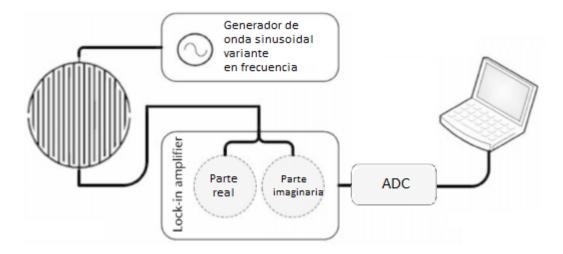

Por tanto, se muestra como es de preponderante importancia la implementación de un sistema conversor de señales analógicas a digital para mejorar el procesamiento de los datos obtenidos por parte del barrido en frecuencia aplicado a las células bajo estudio. La figura 2.2 muestra un diagrama de bloques básico de una posible implementación de un sistema de EIE. Donde se muestra el bloque generador de la señal para el barrido en frecuencia, el tejido bajo análisis, el bloque de retención y eliminador de ruido (Lock-In Amplifier) y por último el ADC que funciona para la transmisión de datos a un computador.

**Figura 2.2.** Diagrama simplificado de un sistema de Espectroscopia por Impedancia Eléctrica. Adaptada de [10].

Ahora bien, se pretende realizar un ADC en circuito integrado en conjunto con los demás módulos del sistema de EIE. Para esto se utilizará la tecnología de fabricación CMOS 0.13 µm IBM8RF pues cumple con las características requeridas para poder llegar a generar una señal de excitación a la frecuencia máxima que se tiene como objetivo (10 GHz).

Además, se debe tener en cuenta la resolución que tendrá el ADC, esto pues a mayor cantidad de bits de resolución, se tendrá una representación cada vez más exacta de la señal analógica en un formato digital. Sin embargo, con el aumento de la cantidad de bits de resolución se tienen problemas asociados y como principal compromiso la velocidad de conversión que será capaz de manejar el ADC.

Otro aspecto a considerar es el área que se estará utilizando ya que, en arquitecturas de alta velocidad como la Flash, un aumento en la resolución equivale a un aumento exponencial del área consumida [11]. El aumento del área también tendrá repercusiones en el aumento de la potencia ya que, al tener una mayor cantidad de transistores, el consumo estático y dinámico de todo el módulo ADC se verá incrementado.

Es por esto que, bajo esta perspectiva, se decide realizar la implementación del ADC con una resolución de 8 bits, que está en el límite alto de implementaciones recomendables para ADCs de alta velocidad de conversión [12]. Además, 8 bits de resolución implican 256 formas de representación de la señal analógica en formato digital que se presupuesta como una cantidad suficiente para validar los resultados obtenidos de la excitación del tejido que este bajo análisis por la técnica de Espectroscopia por Impedancia Eléctrica.

#### 2.2 Convertidor Analógico-Digital

#### 2.2.1. Fundamentos de Conversión Analógica-Digital

Como ya se ha tratado en este documento, la meta principal de este proyecto es el diseño e implementación de un ADC de alta velocidad con una resolución de 8 bits que permita tener una representación de la señal analógica lo suficientemente precisa en un formato digital. Para esto se presentan conceptos necesarios para entender las arquitecturas y el proceso de conversión analógica digital.

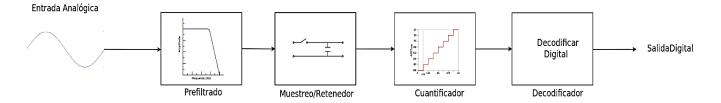

En primera instancia, en la figura 2.3 se muestra la arquitectura básica de un ADC:

Figura 2.3. Bloques básicos de un Convertidor Analógico-Digital.

En la anterior figura se muestra como primer bloque un filtro denominado antireplicador (antialising filter) que tiene como objetivo limitar el ancho de banda de la señal a digitalizar, para evitar el ruido que pueda generarse al muestrear la señal y servir como estabilizador de la señal analógica de entrada para disminuir el riesgo de replicación (aliasing). Además, como se mencionó este filtro tiene la función de eliminar cualquier tipo de ruido que la señal de interés contenga en sus componentes espectrales. La segunda etapa es en la que se realiza el muestreo de la señal de interés, cuando se habilita el interruptor permite que se cargue un capacitor que mantendrá el valor actual de la señal por un periodo de muestreo. Esta función se realiza por parte de un circuito llamado *Sample-and-Hold o Track-and-Hold*.

El siguiente eslabón dentro de la arquitectura del ADC es la cuantización que se refiere a la conversión de valores continuos en series de valores discretos o muestreo en amplitud. Por último, se tiene la etapa de decodificación que es la etapa en la cual se codifica el resultado de la cuantización a un formato binario, que sería la salida del ADC y la representación digital de la señal analógica. A continuación, se detallarán cada una de las etapas antes mencionadas a mayor profundidad.

#### 2.2.1.1. Muestreo y Retención (S/H)

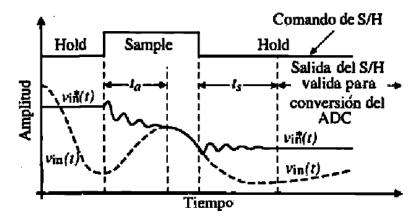

Esta sección es quizás uno de los puntos clave en cualquier arquitectura ADC ya que no solamente aísla la etapa de la entrada con el interior del ADC, sino que también proporciona estabilidad en la señal de entrada para que la conversión de la señal a digital se realice de forma adecuada. La figura 2.4 muestra un esquema típico del comportamiento de un circuito S/H.

**Figura 2.4**. Esquema de funcionamiento del S/H. Adaptada de [3].

En la anterior figura se puede ver como el *tiempo de adquisición* destacado como  $t_a$ , se define como el tiempo en el que el S/H debe permanecer en muestreo para asegurar que la señal analógica pueda ser muestreada de forma correcta por parte del circuito de muestreo, esto asegura que se tenga un nivel confiable para la subsecuente etapa de retención.

El *tiempo de estabilización* se destaca como  $t_s$  y se refiera al intervalo de tiempo entre el cierre del periodo de muestreo y el transitorio producido en la salida que produce oscilaciones en la salida del S/H, este tiempo se debe cumplir para asegurar que la señal que está tomando el ADC como valor de conversión este estable y no produzca conversiones falsas a causa de este

transitorio [3].

Por tanto, para cumplir con los criterios de temporización antes mostrados, el tiempo mínimo de S/H debe ser:

$$T_{muestreo} = t_s + t_a (2.2-1)$$

La ecuación 2.2-1 indica, por lo tanto, que la frecuencia máxima de muestreo del ADC será dada por:

$$f_{muestreo} = \frac{1}{T_{muestreo}} \tag{2.2-2}$$

Cabe destacar que esta frecuencia de muestreo indicada por la ecuación 2.2-2 debe cumplir con el Teorema de Nyquist que indica a grandes rasgos que, para poder reconstruir la señal muestreada, la frecuencia de muestreo debe ser al menos el doble de la frecuencia máxima de la señal de interés.

#### 2.2.1.2. Cuantización

El cuantificador es el encargado de convertir una sucesión de muestras de amplitud continua a una sucesión de valores discretos preestablecidos. En esta etapa la señal muestreada por el S/H es convertida por acción de circuitos como comparadores a valores digitales que crean una representación digital preliminar del valor en amplitud que representa la señal analógica en cuestión. En general, esta etapa se implementa con comparadores que bajo la comparación de la amplitud de la señal analógica y valores de voltajes de referencia crean la decisión del circuito comparador. La salida de esta etapa será un código termómetro que será la entrada de la etapa de decodificación.

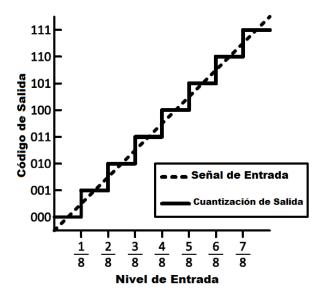

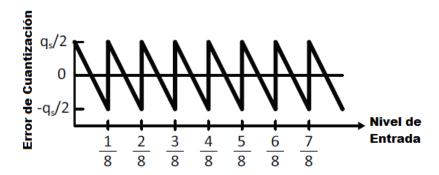

La cuantización crea una representación discreta de la señal que no se adapta a la perfección a la señal analógica como se puede observar en la figura 2.5 que representa un ADC ideal de 3 bits [13]. Este efecto crea un error de cuantización que es un efecto intrínseco de la discretización de una señal continua, ya que no se tiene la suficiente resolución para hacer una representación fiel de la señal analógica. Este efecto de la resolución se puede ver con claridad en la figura 2.6, en donde  $q_s$  se define como paso de cuantización o *quantization step* que indica los paso que se dan ante la entrada de la figura 2.5. Aquí se observa como para un ADC de 3

bits los pasos que se deben dar son muy grandes y no son suficientes para poder seguir a la señal analógica.

Figura 2.5. Cuantización de una señal analógica. Adaptada de [3].

Figura 2.6. Muestra el Error de Cuantización. Adaptada de [3].

Cabe mencionar que la salida de esta etapa de cuantización será un codigo semibinario o código termómetro que permitirá determinar el valor binario que tendrá la señal muestreada.

#### 2.2.1.3. Decodificación

Por último, se tiene la etapa de decodificación que tendrá como entrada el código generado por el cuantificador y dará la salida digital que corresponde al valor muestreado de la señal analógica. Esta etapa básicamente se compone de un decodificador que traduce el código termómetro resultante de la etapa de cuantización a un formato binario que es la salida del ADC.

Esta etapa se puede implementar como un circuito digital ya que el nivel de voltaje del código termómetro se puede tratar como digital, es decir como 1s y 0s pues son salidas de comparadores.

#### 2.2.2. Otros Conceptos

Algunos otros conceptos importantes que se deben conocer para el diseño del ADC [14] son los siguientes:

- ➤ FSR: se refiere al rango máximo que se tiene disponible para crear los voltajes de referencia, es decir, si por ejemplo el voltaje de referencia máximo es 1.2 V, el FSR será 1.2 V.

- ➤ LSB: se refiere al ancho de cada uno de los pasos que se da en el proceso de cuantización. se refiere a la cantidad de pasos que se pueden dar en el proceso de cuantización. Este concepto está asociado a la resolución del ADC y se puede calcular de la siguiente forma:

$$1 LSB = \frac{FSR}{2^{N} - 1} \tag{2.2-3}$$

Donde N en la cantidad de bits de resolución que tenga el ADC.

#### 2.3 Flujo de Diseño IC

En esta sección se explica la metodología que se seguirá en el diseño de este ADC, teniendo en cuenta que el resultado final será una implementación que será construida en un circuito integrado bajo las reglas y técnicas que envuelven un diseño VLSI.

#### 2.3.1. Tecnología de Diseño

Como ya se ha mencionado en varias ocasiones, la tecnología utilizada para la implementación del ADC en sus diferentes etapas de diseño es la de 0.13 µm IBM8RF.

#### 2.3.1.1. Características de la Tecnología

Esta tecnología ofrece las siguientes características que la hacen propicia para la implementación del ADC y los diferentes módulos que componen el IC para la EIE.

- ✓ La Escuela de Ingeniería en Electrónica del ITCR tiene un convenio universitario con MOSIS que le permite fabricar un IC con un área de 4 mm². Uno de los kits de diseño que está dentro de este programa de fabricación gratuita es el de 0.13μm IBM8RF lo que ofrece una ventaja competitiva muy grande frente a otros kits de diseño.

- ✓ La Escuela de Ingeniería en Electrónica tiene una licencia académica del software Mentor Graphics que es el software utilizado para diseñar con el kit 0.13 μm IBM8RF.

- ✓ La tecnología 0.13 μm IBM8RF esta optimizada para aplicaciones de alta velocidad pues es un kit enfocado a aplicaciones en radiofrecuencia.

- ✓ La tecnología 0.13 μm IBM8RF ofrece el rendimiento necesario para poder realizar la generación de la señal de excitación de las células para el proyecto de EIE a frecuencias cercanas y/o superiores a los 10 GHz.

Ahora bien, como el lector de este documento comprenderá el uso de la tecnología 0.13 µm IBM8RF está ligada al uso confidencial de la información expuesto en las hojas de datos de dicha tecnología, por lo que compartir información como anchos mínimos, largos mínimos, tolerancias, capacitancias de las difusiones y otros parámetros eléctricos está prohibido. Si el

lector tiene acceso a los manuales de diseño puede revisar dicha información que podrá ser encontrada en [9].

#### 2.3.1.2. Capas de Metal Utilizadas (Stack-up)

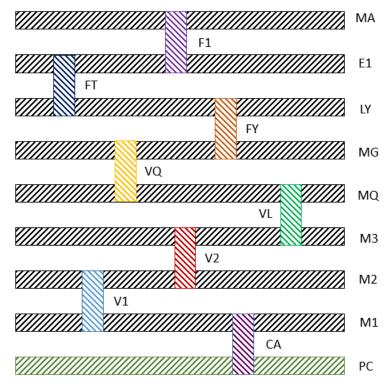

Cuando se realice la implementación física del ADC (layout), se deberá tener en cuenta las capas de metal que se utilizarán para realizar el ruteo entre los diferentes módulos e interconexiones entre los transistores que componen el ADC. En la figura 2.7 se muestra el acomodo de las capas que se van a utilizar en la implementación física.

Figura 2.7. Stack-up utilizado para la implementación Física

Cada uno de los acrónimos de la figura 2.7 se denominan máscaras y corresponden a máscaras utilizadas en el proceso de fabricación. La tabla 2.1 ofrece más detalles sobre esto.

Tabla 2.1. Descripción de las capas utilizadas en la implementación física.

| Nombre de la Máscara | Descripción                                             |

|----------------------|---------------------------------------------------------|

| PC                   | Polisilicio, conecta las compuertas de los transistores |

| CA                   | Conecta PC con M1                                       |

| M1                   | Primer nivel de metal                                   |

| V1                   | Via 1, conecta M1 con M2                                |

| M2                   | Segundo nivel de metal                                  |

| V2                   | Via 2, conecta M2 con M3                                |

| M3                   | Tercer nivel de metal                                   |

| VL                   | Conecta M3 con MQ                                       |

| MQ                   | Primer nivel de metal para cableado                     |

| VQ                   | Conecta MQ con MG                                       |

| MG                   | Segundo nivel de metal para cableado                    |

| FY                   | Conecta MG con LY                                       |

| LY                   | Antepenúltimo nivel de metal                            |

| FT                   | Conecta LY con E1                                       |

| E1                   | Penúltimo nivel de metal                                |

| F1                   | Conecta E1 con MA                                       |

| MA                   | Última capa de metal                                    |

Dado el *stack-up* de la figura 2.7 y la descripción dada en la tabla 2.2, para la implementación del ADC se utilizarán las capas de metal y vias que llegan hasta MG, ya que las capas y vias superiores a MG se utilizaran para el ruteo entre este módulo y los demás módulos del IC que se construirá para el proyecto de EIE.

#### 2.3.2. Metodología de Diseño

Primeramente, se realizó una investigación bibliográfica de topologías de ADC de alta velocidad, esto para asegurar que se cumplan los requerimientos mínimos de resolución, área y velocidad de conversión a los que se debe ajustar el proyecto como parte de un proceso de fabricación en el que se deben cumplir requerimientos muy exigentes. Es por esto que además de lo anterior, la investigación que se realizó, tuvo temas concernientes al proceso de fabricación, pues permitió conocer los pormenores de la tecnología de fabricación 0.13 µm IBM8RF en cuanto a la implementación de los dispositivos que son necesarios en la arquitectura del ADC como lo son: transistores que brinden un rendimiento óptimo, resistencias y sus diferentes parámetros de fabricación. Además, en esta sección es de importancia conocer las reglas de diseño de la tecnología para agilizar la implementación de etapas posteriores como lo es la implementación física o *layout*. El proyecto se realizará a nivel de software, lo que indica que se debe tener un entrenamiento previo en cuanto al uso del software de diseño llamado Mentor Graphics. Este software es el que la Escuela de Ingeniería en Electrónica tiene acceso para el kit de la tecnología 0.13 µm IBM8RF.

Ahora bien, una vez que se tienen las bases teóricas que involucran el proyecto, se seleccionaran al menos tres topologías de ADC que cumplan con los criterios establecidos. A cada una de estas arquitecturas, se le realizará un análisis a nivel teórico que permitirá estimar propiedades de cada una de ellas como lo es área, complejidad en la implementación física y velocidad de conversión.

Una vez seleccionada la arquitectura, se realizara un análisis teórico del ADC, correspondiente a la primer etapa de diseño, pues aquí se conocen las características reales que presenta y puede llegar a tener el ADC en cuanto a velocidad y confiabilidad de conversión ya que, se puede evaluar retardos de los transistores, efectos no lineales intrínseco a cualquier arquitectura ADC, niveles de potencia que se manejaran en las diferentes etapas y dimensionamiento de componentes pasivos (resistencias, capacitores) y activos (transistores), que tiene la arquitectura seleccionada. Seguidamente, en Mentor Graphics se creará la vista en esquemático de la arquitectura del ADC, esta representa la primera etapa de la implementación

del diseño propuesto pues se tienen las herramientas necesarias para realizar la verificación funcional a nivel de esquemático del ADC. Para esto se utilizará el simulador integrado a Mentor Graphics llamado EldoSpice, en el que se evaluara la funcionalidad completa de los diferentes módulos que componen la arquitectura, para posteriormente realizar una simulación de la arquitectura completa en la que se evaluará el rendimiento, velocidad y eficacia de la conversión de señales analógicas a digital. Cabe destacar que esta etapa es de las más importantes pues se debe cumplir con los requerimientos planteados antes de poder seguir con las etapas posteriores.

Con la funcionalidad de la arquitectura a nivel de esquemático, el siguiente paso es la implementación del diseño a nivel físico del ADC o layout. Parte de las estrategias que se siguen está la confección de un plano en el que se planeara la disposición de las celdas que garanticen un mejor rendimiento. Entre los factores que rigieron este rendimiento están: rutas cortas, compartir difusiones para disminuir capacitancias parasitas, disminución del área utilizada, utilización de la menor cantidad de niveles de metal, entre otras. Seguidamente se realizará la disposición de las celdas con ayuda de Pyxis Layout, herramienta disponible en Mentor Graphics para la creación de la vista de layout.

Ahora bien, una vez finalizada la implementación física (layout), se deberá verificar dicha implementación, para lo cual se debe cumplir las Reglas de Diseño (DRC) haciendo uso de Calibre DRC (herramienta interna de Mentor Graphics). El DRC se tiene que pasar sin errores para asegurar el éxito de las etapas posteriores del flujo de diseño, pues si existe algún error, quiere decir que se pueden producir corto-circuitos, interferencias entre señales, etc.

La etapa posterior, es validar la comparación entre layout y esquemático (LVS), esta acción se realiza con la herramienta Calibre LVS que igualmente forma parte de Mentor Graphics. Esta prueba es de suma importancia pues si no es aprobada, quiere decir que el layout no corresponde a lo que se implementó a nivel de esquemático y como en una etapa anterior se revisó que el esquemático funcionara correctamente, el layout es quien tiene errores. Entre las posibles causas de error pueden estar: errores de conexión, escogencia de dispositivos, dimensionamiento, etc.

La etapa posterior consiste en la estimación de los elementos parásitos que tenga el layout, tarea realizada con ayuda de Calibre PEX. Los elementos parásitos a los que se hacen mención

son resistencias y capacitancias que aparecen en la implementación del layout y que contribuyen a ser una carga mayor al caso ideal, aportando en consumo de potencia y retrasos en tiempos de llegada de las diferentes señales como principales efectos. Con lo anterior se pretende tener un modelo más real de las condiciones y elementos que podrían aparecer cuando se fabrique el ADC. Es por esta razón que nuevamente se debe realizar una validación de la arquitectura del ADC, ya que con la aparición de elementos parásitos el funcionamiento del circuito cambia (se espera que estos cambios sean mínimos) y por eso la importancia de esta etapa que permite evaluar y tener una arquitectura final funcional. Esta simulación postlayout se realiza nuevamente con EldoSpice y mide el rendimiento final del ADC antes de la fabricación, pues al ser una simulación a nivel de implementación física, se están tomando en cuenta los modelos parásitos y mayores retardos o problemas que podría llegar a presentar el ADC.

#### Capítulo 3 : Propuesta de Diseño

#### 3.1. Arquitecturas de ADCs de Alta Velocidad de Conversión

Como el lector de este documento ya conoce, parte del desafío de este proyecto es la implementación de un ADC con una arquitectura que demuestre una velocidad de conversión de señales analógicas a digitales lo más alta posible para asegurar que el ADC no represente un cuello de botella al final de la arquitectura del chip que se está diseñando para la aplicación de la técnica de EIE.

Además, se debe tener en cuenta la resolución del ADC, que como se ha detallado, debe ser de al menos 8 bits para que cumpla con los requerimientos planteados y se tenga una representación adecuada de la señal de respuesta de la célula o el tejido bajo análisis en un formato digital que reúna la información necesaria para poder determinar la condición de la muestra.

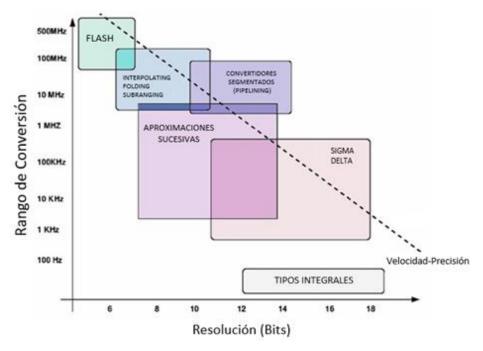

Bajo este panorama, la figura 3.1 ofrece realizar un escrutinio inicial de que arquitecturas se pueden tomar en cuenta como base para el diseño del ADC ya que en dicha figura se realiza una comparación entre una velocidad estimada de conversión y la resolución que cada una de las arquitecturas tenga.

**Figura 3.1**. Gráfico de velocidad de conversión versus bits de resolución para diferentes topologías de ADC. Adaptada de [1].

Dado un análisis inicial del rendimiento que se puede obtener de cada una de las arquitecturas se puede estimar que entre las arquitecturas que tienen la propiedad de alta velocidad se tienen: *Flash, Interpolating-F*olding *Subranging, Convertidores Segmentados* y Aproximaciones *Sucesivas* que a su vez pertenecen a la escala de *Nyquist ADC* [6]. Estas son las arquitecturas más utilizadas para altas velocidades de conversión.

Implementar ADCs con alta velocidad de conversión limita la resolución a la que los convertidores puedan llegar a tener como ya ha sido visto en la figura 3.1, es por esto que se ha estimado, diseñar un ADC con una resolución de 8 bits, pues permite tener una representación binaria de la señal analógica lo suficientemente confiable para permitir llegar a conclusiones validas una vez que se ha procesado la información proveniente de la muestra bajo estudio por parte de la EIE. Es por esto que bajo este panorama a continuación se presenta un análisis de tres topologías de ADC de alta velocidad que pueden ser implementables en este proyecto.

#### 3.1.1. Arquitectura Flash

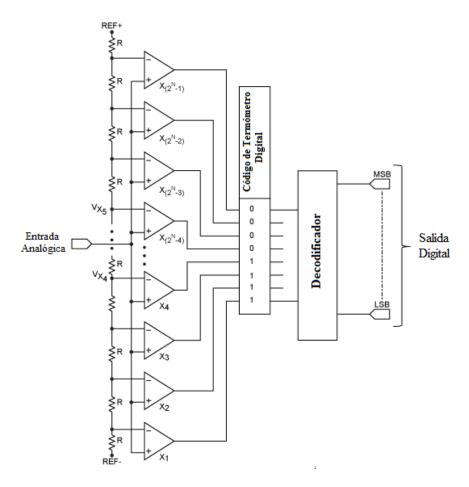

Desde el punto de vista teórico esta arquitectura es la más simple y presenta un potencial para tener una velocidad de conversión superior a todas las demás arquitecturas ya que se basa en el paralelismo y muestreo paralelizado para alcanzar altas velocidades de conversión [15]. La figura 3.2 muestra un ejemplo típico de cómo es la implementación de esta arquitectura, en donde se muestran en un alto nivel los principales bloques funcionales de una arquitectura de ADC tipo Flash.

Esta arquitectura se basa en tres etapas básicas: una primera etapa implementada con una escalera de divisores resistivos que proporcionan la referencia para los comparadores de la siguiente etapa. Esta escalera de divisores resistivos proporciona 2<sup>N</sup> referencias igualmente espaciadas, donde N es la resolución del ADC.

La etapa de cuantificación es implementada con comparadores en los que se dispara una salida "digital" cuando el valor de la señal de entrada sobrepasa al de la referencia que es generada en la escalera de divisores resistivos. Esta etapa es quizás la más crítica de toda la arquitectura pues los comparadores no solamente tienen que responder a una gran velocidad, sino que también deben ser estables pues ante cambios en las señales de entrada (ruido) no se debe permitir cambios en el resultado de la comparación.

Figura 3.2. Estructura típica de un ADC Flash. Adaptado de [2].

Esta arquitectura no necesita S/H pues los comparadores realizan un muestreo paralelizado, es decir, cada comparador realiza el muestreo y la cuantización en una sola etapa, lo que permite una mayor velocidad de conversión al no necesitar etapas que ralentizan el proceso. Uno de los problemas que tiene esta arquitectura es que necesita 2<sup>N</sup>-1 comparadores, donde N es la resolución del ADC [6]. Esto indica que para un ADC con una resolución de 8 bits se necesitan 255 comparadores, lo que es prácticamente inviable por requerimientos de área. Además, desde el punto de vista de potencia consumida es más elevada que otras arquitecturas ya que en general los comparadores de alta velocidad consumen más potencia que comparadores de aplicaciones de baja velocidad.

La última etapa es un decodificador, que recibe el código termómetro generada por los comparadores de la etapa anterior. Esta sección del ADC genera el código binario que identifica el valor discreto de la señal analógica que ha sido muestreada. Esta etapa en general recibe un código binario de entrada por lo que se puede construir y diseñar con técnicas de diseño digital combinacional por lo que se tendrá que diseñar teniendo en cuenta la velocidad de propagación de esta etapa combinacional que tendrá un impacto directo en la velocidad de conversión.

#### 3.1.2. Registro de Aproximaciones Sucesivas (SAR)

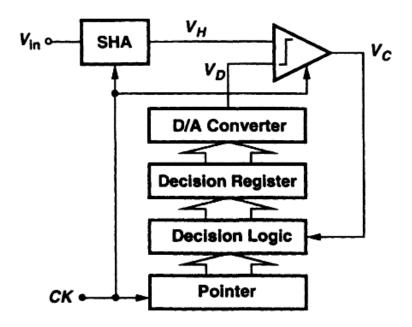

Esta arquitectura de ADC está basada en una combinación entre un ADC y un DAC pues en el diagrama de la arquitectura que se muestra en la figura 3.3, se puede observar dicha combinación. Esta arquitectura es una de las arquitecturas más deseadas cuando se necesita un ADC con resolución y velocidad media pues en comparación con una arquitectura 100% Flash, es N+1 veces más lenta, donde N es la resolución del ADC.

**Figura 3.3**. Arquitectura SAR ADC. Adaptada de [3].

Como la figura 3.3 lo muestra esta arquitectura cuenta con un S/H, comparador con arquitectura de alta velocidad, registro de desplazamiento, lógica de decisión, registro de decisión y un DAC lo que representa en general una arquitectura con una complejidad de implementación menor comparado a otras arquitecturas.

El funcionamiento de esta arquitectura se basa en múltiples comparaciones sucesivas ya sean ascendentes o descendentes según corresponda la salida del DAC que es el encargado de realizar dicho cambio en la comparación para poder igualar la tensión de la señal de entrada. Inicialmente el registro de desplazamiento comienza en cero y en el primer ciclo de reloj se pone un 1 en el MSB, dejando los demás bits del registro en cero. Este valor es convertido a una señal analógica que es comparada con la señal de entrada, si dicha señal es menor a V<sub>in</sub> se agrega un 1 al MSB del registro de desplazamiento quedando en 110...00; en caso contrario si la señal es mayor a V<sub>in</sub> se agrega un 0 al valor MSB del registro quedando como 010...00. El proceso continúa de la misma manera hasta poder alcanzar el valor LSB y este código final será la salida del ADC SAR.

# 3.1.3. Interpolación y Plegado (Folding and Interpolation)

Esta arquitectura se basa en dos mejoras que se la hace a la arquitectura del ADC Flash para reducir la cantidad de comparadores que se deben utilizar. Esta arquitectura es la más utilizada cuando se desea implementar ADC de alta velocidad pues permite velocidades de muestreo similares a las alcanzadas con la arquitectura Flash, pero con la ventaja de hacer un uso más eficiente del área utilizada en la implementación [6].

#### 3.1.3.1. Interpolación

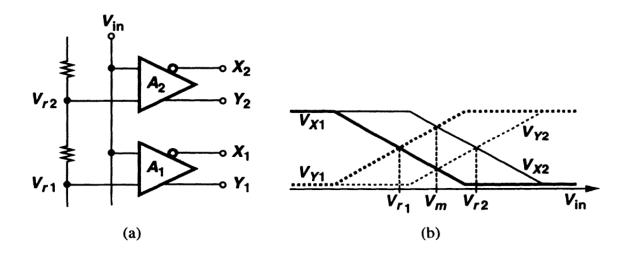

Para poder realizar el proceso de reducción de comparadores, la diferencia entre la señal analógica de entrada y el voltaje de referencia puede ser cuantizada a la salida de los preamplificadores. Esto es posible gracias a que los preamplificadores usados son de ganancia finita.

Este concepto puede ser ilustrado por medio de la figura 3.4. En la figura 3.4 (a), los preamplificadores  $A_1$  y  $A_2$  comparan la entrada analógica con  $V_{r1}$  y  $V_{r2}$ , respectivamente. En la figura 3.4 (b), la entrada/salida característica de  $A_1$  y  $A_2$  son presentadas en donde se asume que

no hay offset en ambos preamplificadores, por tanto, se puede ver que  $V_{x1}=V_{y1}$  si  $V_{in}=V_{r1}$  y  $V_{x2}=V_{y2}$  si  $V_{in}=V_{r2}$ . Más importante aún,  $V_{x2}=V_{y1}$  si  $V_{in}=V_{m}=$   $(V_{r1}+V_{r2})/2$ , por tanto, la polaridad de la diferencia entre  $V_{x2}$  y  $V_{y1}$  es la misma que la diferencia entre  $V_{in}$  y  $V_{m}$  [15].

Visto de otra forma el proceso de interpolación lo que hace es crear nuevos voltajes de referencia posterior a los preamplificadores lo que reduce la cantidad de comparadores que se utilizan. Las ventajas de la interpolación es que primeramente se reduce el área utilizada lo que repercute en una disminución en la potencia consumida y además trae consigo una disminución en la capacitancia de entrada del ADC.

**Figura 3.4.** Interpolación entre la salida de dos preamplificadores. Adaptado de [4].

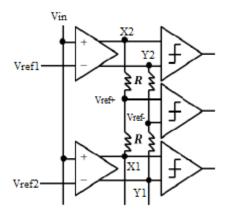

Ahora bien, una forma de implementar la interpolación es la interpolación 2R como se puede observar en la figura 3.5, que utiliza divisores resistivos para crear los nuevos voltajes de referencia, que como se puede ver de las ecuaciones 3.1-1 y 3.1-2 la interpolación 2R lo que genera es un promedio entre los voltajes de los nodos bajo interés. Los nuevos voltajes de referencia para los nodos  $V_{ref+}$  y  $V_{ref-}$ , entradas del comparador del medio, se calculan como lo muestran las ecuaciones 3.1-1 y 3.1-2.

$$V_{ref+} = \frac{V_{x1} + V_{x2}}{2} \tag{3.1-1}$$

$$V_{ref-} = \frac{V_{Y1} + V_{Y2}}{2} \tag{3.1-2}$$

Figura 3.5. Implementación de la interpolación. Adaptado de [5].

### 3.1.3.2. Plegado (Folding)

Como ya se analizó anteriormente, la arquitectura Flash provee conversiones en un paso sin necesitar un preprocesamiento analógico, pero con el agravante de sufrir de gran capacitancia de entrada, gran disipación de potencia y área. La arquitectura Folding realiza un preprocesamiento analógico para reducir el hardware mientras mantiene la característica de conversión en un paso de la arquitectura flash original.

El principio básico es el de generar un voltaje de residuo a través de un preprocesamiento analógico y subsecuente digitalización de los residuos para obtener el LSB. El MSB se obtiene utilizando una etapa ordinaria de la arquitectura Flash que operará en paralelo con el circuito de plegado y por lo tanto muestrear la señal en aproximadamente el mismo tiempo que se da el muestreo del residuo.

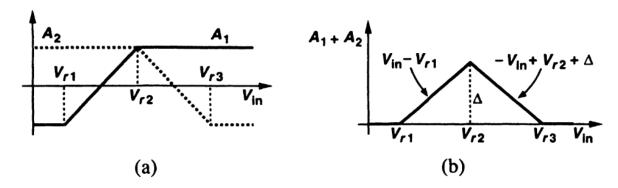

Ahora bien, considere dos preamplificadores  $A_1$  y  $A_2$  con característica de entrada/salida mostrada en la figura 3.6 (a). La región activa de uno de los preamplificadores está centrada alrededor de  $(V_{r1} + V_{r2})/2$  y para el otro alrededor de  $(V_{r2} + V_{r3})/2$  y  $V_{r3}$  -  $V_{r2} = V_{r2}$  -  $V_{r1}$ .

Cada amplificador tiene ganancia unitaria en la región activa y ganancia de cero en la región de saturación. Si la salida de los dos preamplificadores es sumada, la característica de plegado se muestra en la figura 3.6 (b), resultando una salida igual a  $V_{in}$  -  $V_{r1}$  para  $V_{r1}$  <  $V_{in}$  <  $V_{r2}$  y - $V_{in}$  +  $V_{r2}$  +  $\Delta$  para  $V_{r2}$  <  $V_{in}$  <  $V_{r3}$ , donde  $\Delta$  es el valor de la suma en  $V_{in}$  =  $V_{r2}$ . Por lo tanto, si  $V_{r1}$ ,  $V_{r2}$ ,  $V_{r3}$  son voltajes de referencia de un ADC entonces estas dos regiones pueden ser vistas

como una característica de residuo del ADC para  $V_{r1} < V_{in} < V_{r3}$  [15].

**Figura 3.6**. (a) Características de entrada/salida de dos preamplificadores, (b) suma de las características en (a). Adaptado de [4].

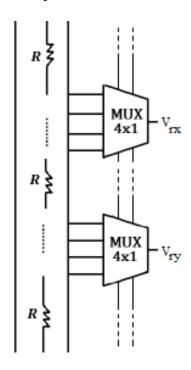

Ahora bien, una forma de implementar esta técnica de plegado es con el uso de multiplexores que generan los voltajes de resido al tener diferentes voltajes de entrada que corresponden a salidas de escaleta resistiva. La figura 3.7 muestra esta implementación donde los voltajes de residuo que están etiquetados como  $V_{rx}$  y  $V_{ry}$  serán utilizados en la etapa siguiente como voltajes de referencia para los comparadores.

**Figura 3.7.** Aplicación de la técnica de plegado. Adaptado de [5].

## 3.1.3.3. Folding and Interpolation

Anteriormente se han analizado por separado las características de mejora que la técnica de interpolación y plegado ofrecen para la arquitectura ADC Flash tradicional. Ahora bien, estos dos métodos pueden ser combinados para ofrecer una mejora superior en cuanto al uso del área, potencia consumida y capacitancia de entrada sin inhibir a la arquitectura general de la conversión de señales analógicas a digitales en un solo paso, ya que los elementos que se agregaran no dependen de una señal de reloj que agregue pasos a la conversión.

Sin embargo, se compromete en cierto punto la velocidad ya que dichos elementos que se van a agregar incrementan la velocidad de propagación de la señal, principalmente en el preprocesamiento hecho por la técnica de plegado. Esto se debe tomar en cuenta al momento de la escogencia de la frecuencia de reloj con la que trabajaran los comparadores. Otro aspecto es que al agregar elementos a la arquitectura la simplicidad intrínseca de la arquitectura Flash en su etapa de implementación se va a perder pues agregar elementos complica su implementación final en todas sus etapas (diseño de los elementos extra, esquemático de la arquitectura, layout, verificación y validación).

# 3.2. Escogencia de la Arquitectura ADC

# 3.2.1. Criterios de escogencia

En la sección anterior se han presentado tres arquitecturas generales de ADC de alta velocidad en las que se han presentado, además, las principales características y una explicación general del funcionamiento de cada una de ellas. Con base en esto los siguientes criterios serán tomados en cuenta en la escogencia de la arquitectura final.

- ➤ Área

- > Potencia consumida

- Velocidad de conversión

## 3.2.2. Análisis de arquitecturas

Según los criterios antes mencionados, se presenta un análisis de cada una de las arquitecturas tomando en cuenta los criterios antes señalados.

#### Flash

Esta arquitectura tiene como característica principal la de poder convertir la señal analógica en digital en un solo ciclo de reloj, maximizando la velocidad de conversión que se pueda tener ya que al tener solamente 3 etapas principales (escalera resistiva, cadena de comparadores y decodificador), el ancho del pulso de reloj puede verse minimizado, conllevando a una mayor frecuencia de muestreo. En cuanto a presupuestos de área, esta arquitectura es la que posee mayores problemas ya que la cantidad de comparadores aumenta exponencialmente con la resolución, esto hace que esta arquitectura ocupe una mayor área.

Un aspecto a rescatar es que arquitecturas de alta velocidad implican una conmutación más acelerada de los transistores que componen la arquitectura que conlleva a un consumo de corriente más elevado. Además, por la cantidad de transistores que en general se utilizaran, el consumo de potencia será alto con respecto a otras arquitecturas que utilizan menos hardware.

#### Registro de Aproximaciones Sucesivas

Esta arquitectura tiene la ventaja que el hardware que se utilice será menor en comparación con otras arquitecturas por lo que en cuento a área es la arquitectura con mejores prestaciones que se van a extender a la potencia consumida, ya que en general al tener menos hardware en su arquitectura, menos potencia será consumida.

El aspecto que quizás más impacta esta arquitectura es el hecho de utilizar varios ciclos de reloj para poder realizar la conversión de la señal analógica, lo que impacta directamente en el rendimiento esperado por el ADC que se estará utilizando en el proyecto de EIE.

#### Interpolación y Plegado

Esta arquitectura como ya se ha analizado antes, es una modificación de la arquitectura Flash. El principal objetivo de estas modificaciones es la reducción del hardware utilizado en la arquitectura, principalmente buscando la reducción de la cantidad de comparadores que se necesitan para realizar la comparación sin comprometer la característica principal de la arquitectura Flash que es la de realizar la conversión de la señal analógica en un solo pulso de reloj.

Esto implica que, en cuento a velocidad sigue siendo una arquitectura veloz, menos que la Flash original por la adición en hardware extra que impacta en la reducción de los comparadores, pero con frecuencias de muestreo superiores a otras arquitecturas como la de Registro de Aproximaciones Sucesivas.

Otro aspecto importante, es que, al disminuir la cantidad de comparadores, se logra realizar una disminución en el área necesaria para implementar el ADC, lo que estaría impactando directamente en la potencia total consumida por el circuito.

Dado el análisis anterior, se puede ver que la arquitectura de Interpolación y Plegado arroja un balance entre los tres aspectos considerados para la escogencia de la arquitectura pues es capaz de convertir a altas velocidades, similares a la arquitectura Flash y superiores a la SAR. Utiliza un área mayor que la SAR pero menor a la Flash y este aspecto impacta directamente en la estimación de potencia consumida relacionándola directamente con la cantidad de área necesaria para la implementación del ADC.

Por tanto, se escoge implementar una arquitectura de **ADC con Interpolación y Plegado** que sacrifica velocidad de conversión, pero ofrece un balance entre velocidad de conversión, potencia consumida y área necesaria para la implementación del ADC.

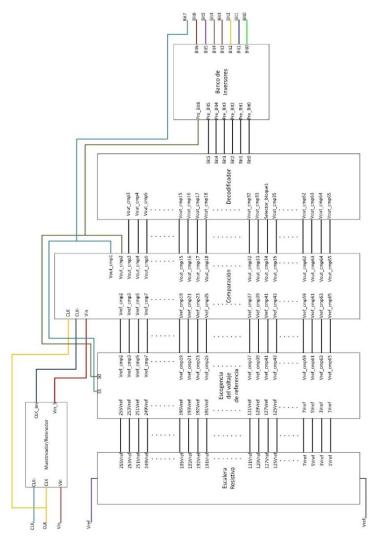

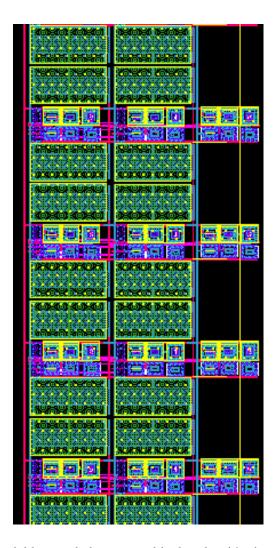

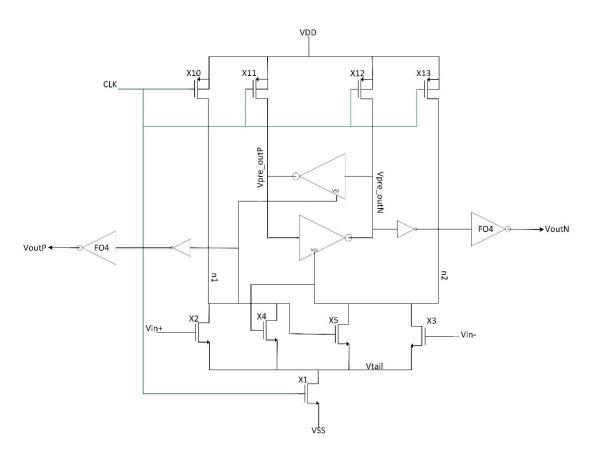

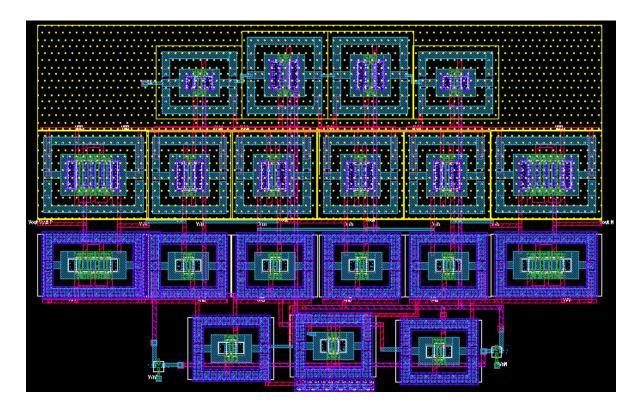

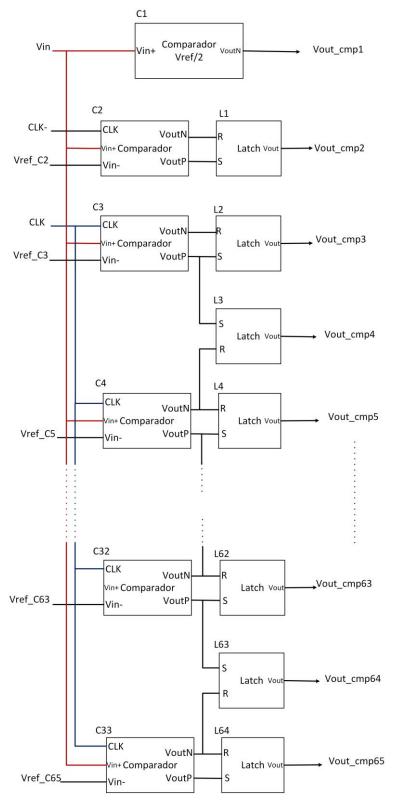

# Capítulo 4 Diseño de la Arquitectura

Como se analizó en la sección anterior, se realizará la implementación y diseño de un ADC que toma en cuenta las técnicas de interpolación y plegado para optimizar la arquitectura en cuanto al área utilizada, esto porque al aplicar estas técnicas se reduce la cantidad de comparadores en comparación de una arquitectura Flash tradicional. A lo largo de esta sección se discutirán los diferentes módulos que conllevarán a obtener una arquitectura de ADC completa y funcional como lo muestra la figura 4.1, en la que se muestra la implementación a nivel de bloques funcionales del ADC propuesto. Estos bloques funcionales serán explicados en este capítulo.

Figura 4.1. Arquitectura ADC propuesta.

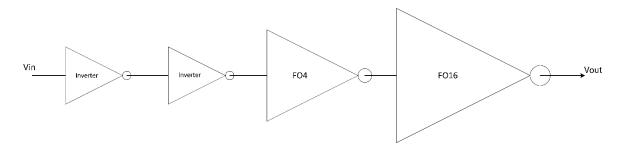

Además de lo anterior, en esta sección se discutirá el paso de las subceldas diseñadas a nivel de esquemático a una etapa física en la que se deben tener en cuenta varias características del diseño VLSI para obtener un comportamiento similar al mostrado en la implementación del esquemático. Algunos de los aspectos básicos que se tomaran en cuenta para toda la construcción del layout son las siguientes:

- Diseño basado en celdas estándar, es decir celdas con altura establecida que beneficia y aligere el ruteo de los rieles de alimentación (poder y/o tierra). La altura estándar para cada una de las celdas será 10.22 μm.

- Uso de capas de metal de niveles inferiores que ayuden a reducir las capacitancias parasitas que se puedan generar al cambiar de niveles de metal superiores.

- Distribución de potencia simétrica, es decir en la arquitectura final los rieles de alimentación deben estar distribuidos por todo el layout para facilitar conexión de las celdas.

- Colocar las celdas y macroceldas tan cercanas como sea posible para optimizar el área que se esté utilizando.

- Pasar cada uno de los flujos de revisión del layout (DRC, LVS, PEX).

Cabe destacar que el kit de la tecnología 0.13 µm IBM8RF contiene transistores RF (radiofrecuencia), los cuales son transistores especializados que entre otras características tiene un mejor manejo de las señales de alta frecuencia que es de especial importancia para este ADC, es por esto que la mayoría de transistores que se han utilizado son transistores RF [16] [17]. Además, se han utilizado transistores de bajo voltaje de umbral (low voltage threshold), pues este tipo de transistores ofrecen la característica de conmutar con una velocidad mayor en comparación con transistores con voltaje de umbral mayores.

# 4.1. Módulos de la Arquitectura

En esta sección se explicarán cada uno de los módulos que componen la arquitectura del ADC, tanto a nivel de esquemático como implementación física. Además, las simulaciones que se presentan en esta sección, son simulaciones postlayout pues presentan una idea más real sobre el comportamiento de cada uno de los circuitos. Además, cada uno de los bloques de layout que se presentan, han pasado el DRC y LVS. Posterior a esto se ofrecerá la arquitectura completa y una explicación a nivel de funcionamiento de la arquitectura.

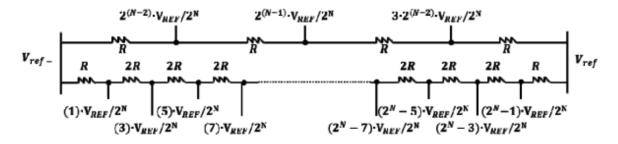

# 4.1.1. Escalera Resistiva (Resistive Ladder)

En la mayoría de implementaciones de arquitecturas Flash, el voltaje de referencia para los comparadores es generado por divisores resistivos que en su mayoría consisten de una fila de N+1 resistencias. Implementar el divisor resistivo de esta forma puede causar discrepancias muy grandes en el valor de las resistencias pues en circuitos integrados la creación de resistencias puede ser un problema, esto porque los valores que se pueden llegar a tener son limitados junto con las variaciones en el proceso de fabricación.

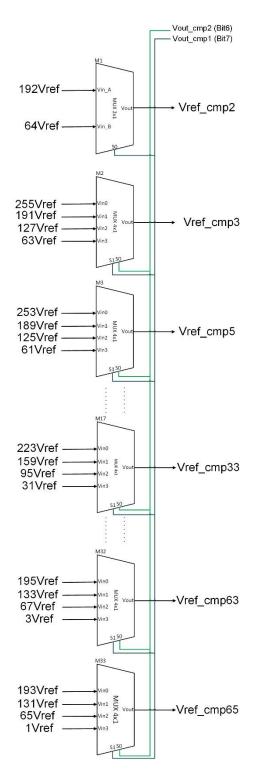

Bajo esta perspectiva es que se decide hacer un cambio en la arquitectura ADC que se está presentando, pues se están diseñando dos escaleras de división resistiva, donde en una de ellas se generan los voltajes más críticos, es decir, 64Vref y 192Vref; mientras que en la otra rama se estarán generando los demás voltajes de referencia para los comparadores.

La escalera resistiva tiene dos voltajes de referencia Vref+ es el voltaje de referencia mayor, mientras que Vref- el voltaje de alimentación más bajo. Esto permite que el ADC pueda cambiar de niveles de voltaje para adecuarse a señales con rangos de voltaje que no están en el rango de 0 a 1.2V y así aprovechar de mejor manera los 8 bits de la resolución de este ADC.

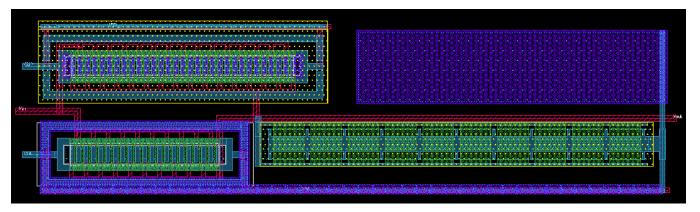

La figura 4.2 muestra la implementación de esta escalera resistiva en la que se reduce la cantidad de resistencias en comparación a una arquitectura Flash convencional a un poco más de la mitad ya que en la arquitectura que diseñada se están utilizando 133 resistencias mientras que en una arquitectura Flash tradicional se estarían utilizando 257 resistencias. Esta reducción se logra creando pasos dobles en lugar de pasos simples entre los voltajes de referencia que combinado a las técnicas de interpolación y plegado se refleja en una optimización del hardware

utilizado. Las resistencias que se utilizaron son las OPRRPRES que dan un rango acertado ya que son capaces de dar valores de 1.0733 k $\Omega$  (L=1.06 µm y W=0.74 µm) y 2.144 k $\Omega$  (L=1.48 µm y W=0.74 µm), que resultan en valores ideales para esta arquitectura pues son valores relativamente altos y limitaran la corriente consumida a un máximo de 4.373 µA cuando Vref+ es 1.2V y Vref- es 0V. Cabe mencionar que en la figura 4.1, R se refiere a la resistencia OPRRPRES de valor 1.0733 k $\Omega$ , 2R a la resistencia OPRRPRES de valor 2.144 k $\Omega$  y N a la resolución del ADC.

**Figura 4.2**. Diagrama esquemático de la escalera resistiva. Adaptada de [5].

En el Anexo 1 se puede observar una tabla con cada uno de los valores de referencia que esta escalera resistiva está generando para un voltaje de referencia Vref de 1.2V y un voltaje Vref- de 0V. La forma en cómo se calcula el voltaje de referencia esta enunciado en la ecuación 4.1-1, donde #Salida se refiere a la salida de la escalera resistiva, Vref al voltaje positivo de referencia, Vref- al voltaje negativo de referencia de la escalera resistiva y N a la cantidad de bits de resolución del ADC

$$Vref = \#Salida * \frac{(V_{ref} - V_{ref})}{2^{N} - 1}$$

(4.1-1)

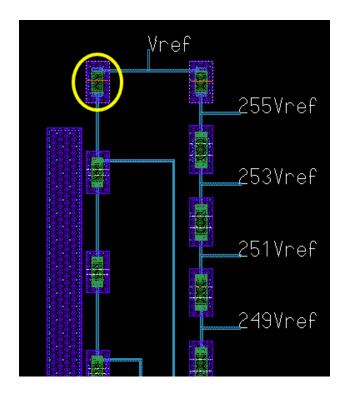

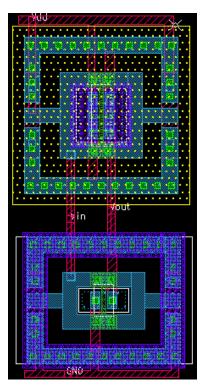

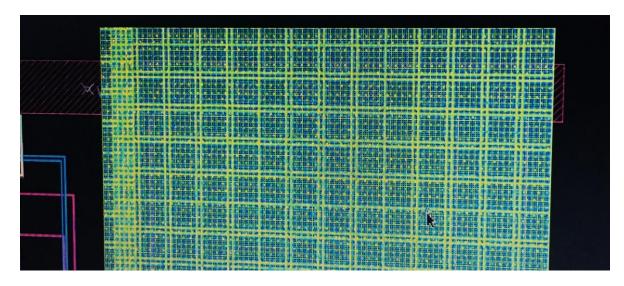

Ahora bien, en cuanto a la implementación del layout de la escalera de divisores resistivos se tiene una vista del mismo en la figura 4.3. Cabe mencionar que el layout del divisor resistivo no aparece en su totalidad ya que la altura es muy grande (676.20 µm), sin embargo, se ofrece una vista en la que se muestran las dos ramas de resistencias y algunas de las salidas del mismo. En la figura 4.3, la zona destacada con un circulo amarillo, corresponde a una de las resistencias en su implementación física.

Figura 4.3. Muestra una parte del layout de la escalera resistiva.

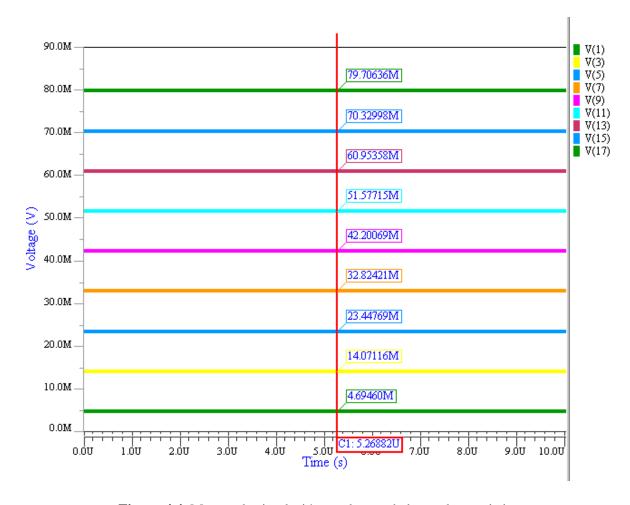

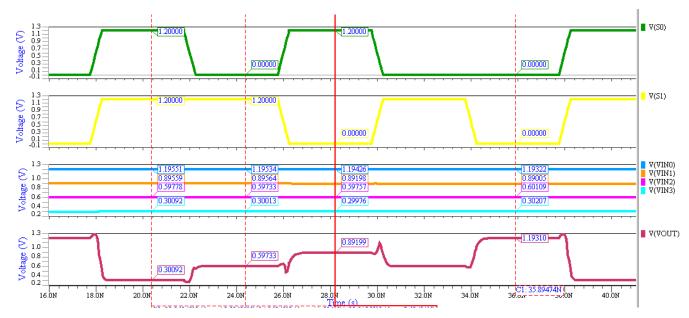

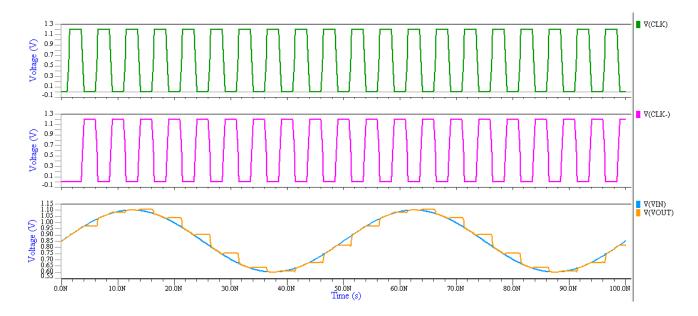

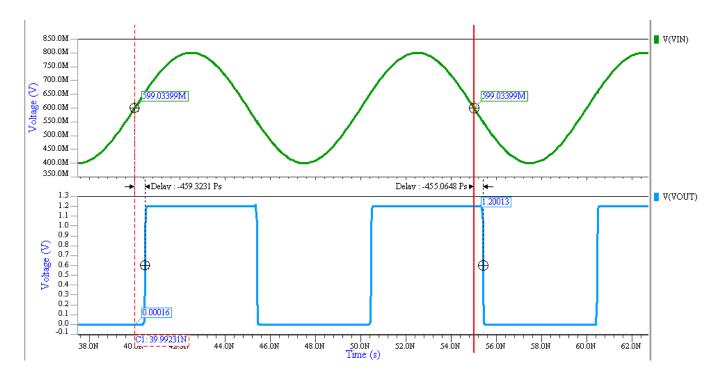

La simulación de este subcircuito se puede observar en la figura 4.4, en ella se muestran algunos voltajes de referencia pues poner los voltajes haría prácticamente imposible de observar los voltajes. En dicha simulación en comparación con la tabla del Anexo 1, se puede ver como las variaciones en el voltaje de referencia teórico y postlayout son mínimas, las discrepancias se ven reflejadas en el orden de las decenas de  $\mu V$ .

Figura 4.4. Muestra la simulación postlayout de la escalera resistiva.

### 4.1.2. Selección de los voltajes de referencia para los comparadores

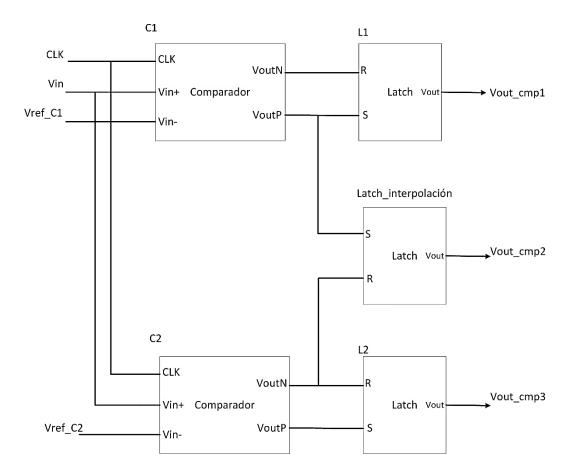

Esta macro celda de la arquitectura del ADC, es la encargada de escoger los voltajes de referencia para los comparadores de una de las etapas que se explicaran más adelante. Además, en esta sección del circuito se implementa la técnica de plegado, que, junto con la interpolación, ayuda a reducir la cantidad de comparadores que se deban utilizar.

Esta celda se basa en la multiplexión para poder escoger cada uno de los voltajes de referencia. Es por esto que a continuación se realiza un análisis de las arquitecturas escogidas para la implementación de esta sección.

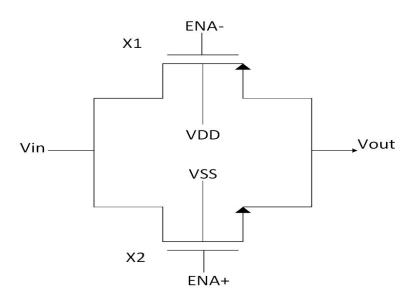

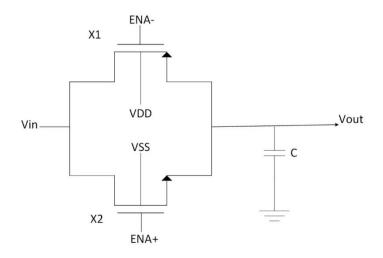

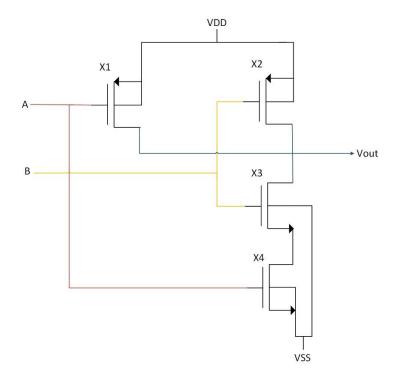

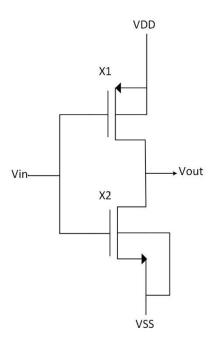

## 4.1.2.1. Compuertas de paso

Una de las formas más sencillas de implementar multiplexores es haciendo uso de compuertas de paso que se basan en la interconexión del drenador de un transistor PMOS con el drenador de un NMOS e igualmente se interconectan las fuentes de cada uno de los transistores. Además, se cuenta con una única señal habilitadora de polaridad invertida para cada transistor; la señal habilitadora se conecta a la compuerta de cada uno de los transistores.

La compuerta de paso es básicamente un interruptor que bloquea el paso de la señal que tiene como entrada si se encuentra deshabilitado. Se utiliza un transistor de cada tipo (NMOS y PMOS), pues cada uno de ellos logra una mejor conducción para diferentes valores de voltaje, entiéndase con esto que el transistor PMOS es más eficiente conduciendo valores de voltaje altos sin degradar la señal y el NMOS es más eficiente conduciendo valores bajos de tensión sin degradar la señal que tendrá como salida. Por lo que, poner un transistor de cada tipo provocaría que no importe la amplitud de la señal, a la salida no se producirá una degradación de la señal significativa.

La figura 4.5 muestra la compuerta de paso implementada, donde además se debe hacer notar que el transistor NMOS\_RF (X1) tiene como dimensiones L=0.15  $\mu$ m y W=0.5  $\mu$ m, mientras que el PMOS\_RF (X2) tiene como dimensiones L=0.15  $\mu$ m y W=0.5  $\mu$ m.

Figura 4.5. Esquemático de la compuerta de paso.

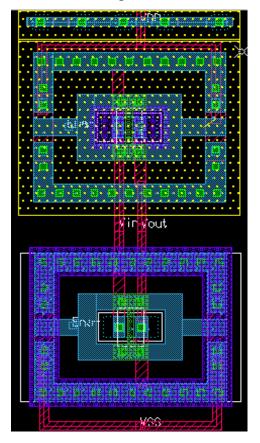

Además, en la figura 4.6 se muestra la implementación física de dicha compuerta de paso.

Figura 4.6. Layout de la compuerta de paso.

## 4.1.2.2. Multiplexor de 2 entradas 1 salida