#### Instituto Tecnológico de Costa Rica

Escuela de Ingeniería Electrónica

Integración de un microprocesador de aplicación específica en un flujo de diseño de circuitos integrados digitales.

Informe de Proyecto de Graduación para optar por el título de Ingeniero en Electrónica con el grado académico de Licenciatura

Reinaldo Castro González

# INSTITUTO TECNOLÓGICO DE COSTA RICA ESCUELA DE INGENIERÍA ELECTRÓNICA PROYECTO DE GRADUACIÓN

#### ACTA DE APROBACIÓN

Defensa de Proyecto de Graduación Requisito para optar por el título de Ingeniero en Electrónica Grado Académico de Licenciatura Instituto Tecnológico de Costa Rica

El Tribunal Evaluador aprueba la defensa del proyecto de graduación denominado: Integración de un microprocesador de aplicación específica en un flujo de diseño de circuitos integrados digitales, realizado por el señor Reinaldo Castro González y, hace constar que cumple con las normas establecidas por la Escuela de Ingeniería Electrónica del Instituto Tecnológico de Costa Rica.

Miembros del Tribunal Evaluador

Ing Roberto Molina Robles

Ing. Ronny García Ramírez

Profesor lector

Profesor lector

Ing. Alfonso Chacón Rodríguez

Profesor asesor

Cartago, 2 de Mayo de 2017

Declaro que el presente Proyecto de Graduación ha sido realizado enteramente por mi persona, utilizando y aplicando literatura referente al tema e introduciendo conocimientos propios.

En los casos en que he utilizado bibliografía he procedido a indicar las fuentes mediante las respectivas citas bibliográficas. En consecuencia, asumo la responsabilidad total por el trabajo de graduación realizado y por el contenido del correspondiente informe final.

Reinaldo Castro González

Cartago, 2 de mayo de 2017

Céd: 3 0454 0969

### Resumen

En este documento se expone una metodología de diseño semipersonalizado de circuitos integrados digitales, mediante el uso de las herramientas Synopsys empleando una tecnología CMOS de 0,13 micrómetros. El flujo de diseño se efectúa mediante una estructura de scripting, principalmente en lenguajes TCL, Bash, y PERL, congruentes con la semántica de las herramientas de Synopsys. Se expone como se desarrolla la jerarquía de archivos y directorios para ubicar los archivos fuente y los productos de la ejecución del flujo.

Se analiza la efectividad del flujo, sometiendo el RTL de un microprocesador de aplicación específica (ASP) en arquitectura RISC-V. Se expone la integración de una celda física para la unidad de punto flotante del ASP y las celdas físicas de las memorias para datos y programa del ASP. El análisis se realiza sobre los reportes generados por la herramienta, y sobre una verificación determinística sobre el RTL y los GLN, mediante simulaciones generadas a partir de bancos de prueba (testbench) derivados de un modelo dorado de alto nivel.

Palabras clave: Back End, Front End, GLN, Integración, RTL, Script, Síntesis, STA, Synopsys

### Abstract

This document presents a semipersonalized design methodology of digital integrated circuits, by using of Synopsys tools and a 0,13  $\mu m$  CMOS technology. The design flow is made through a scripting structure, mainly in languages like TCL, Bash, and PERL, wich are consistent with the semantics of Synopsys tools. This work discusses how the file and directory hierarchy is developed to locate source files and output products.

The effectiveness of the flow is analyzed by subjecting the RTL of a RISC-V arquitectured Specific Application Microprocessor (ASP). It discusses the integration of a physical cell for the ASP floating-point unit and the physical cells of the ASP data and program memories. The analysis is performed on the reports generated by the tool, and deterministic verification on the RTL and GLN, through simulations generated from test benches, that derives from a golden reference model implementet in a high level programming language.

Keywords: Back End, Front End, GLN, Integración, RTL, Script, Síntesis, STA, Synopsys

# Agradecimientos

A mis padres que han sido el pilar fundamental en mi vida, ustedes son los responsables de que sea la persona que soy. Gracias por sus sabios consejos y apoyo incondicional.

A mi hermano Rolando, quien ha sido un gran apoyo en todos mis proyectos, siempre un ejemplo para mí, y mi modelo a seguir mientras crecía.

A mi primo Miguel por ser siempre un amparo para continuar con mis proyectos, gracias por ser otro hermano mayor para mí y brindarme tu apoyo en todas mis metas.

Al Ing. Dr. Alfonso Chacón Rodríguez por toda la colaboración que me brindó, no sólo para que este proyecto se consolidase, sino por toda su ayuda para que pudiese continuar estudiando en esta institución. Gracias por sus consejos, sus duras lecciones y amistad.

Finalmente a los Ingenieros: Dr. Juan Agustín Rodríguez, quien sentó las bases para poder llevar a cabo este proyecto, al M.Sc. Carlos Salazar y M.Sc. Ronny Gracía, quienes colaboraron en la supervisión para que este proyecto fuese exitoso.

Reinaldo Castro González

Cartago, 2 de mayo de 2017

# Índice general

| Ín | $\operatorname{dice}$ | de figuras                                                               | iii |

|----|-----------------------|--------------------------------------------------------------------------|-----|

| Ín | $\mathbf{dice}$       | de tablas                                                                | vii |

| 1  | Intr                  | roducción                                                                | 1   |

|    | 1.1                   | Entorno de la tesis                                                      | 1   |

|    | 1.2                   | Descripción del problema y justificación                                 | 4   |

|    | 1.3                   | Síntesis del problema                                                    | 4   |

|    | 1.4                   | Enfoque de la solución                                                   | 4   |

|    |                       | 1.4.1 Generalidades de la solución                                       | 4   |

|    |                       | 1.4.2 Síntesis de la solución                                            | 5   |

|    | 1.5                   | Trabajos anteriores                                                      | 5   |

|    | 1.6                   | Objetivos                                                                | 7   |

|    |                       | 1.6.1 Meta                                                               | 7   |

|    |                       | 1.6.2 Objetivo general                                                   | 7   |

|    |                       | 1.6.3 Objetivos específicos                                              | 7   |

| 2  | Ma                    | rco teórico                                                              | 9   |

|    | 2.1                   | Tipos de diseño circuitos integrados digitales                           | 9   |

|    |                       | 2.1.1 ICs totalmente personalizados                                      | 9   |

|    |                       | 2.1.2 <b>ICs programables</b>                                            | 10  |

|    |                       | 2.1.3 ICs semipersonalizados                                             | 11  |

|    | 2.2                   | Flujo de diseño digital para el diseño de circuitos integrados digitales | 12  |

|    |                       | 2.2.1 Generalidades del flujo de diseño digital                          | 13  |

|    |                       | 2.2.2 Flujo de diseño digital en las herramientas de Synopsys            | 16  |

|    |                       | 2.2.3 Front End                                                          | 16  |

|    |                       | 2.2.4 Back End                                                           | 18  |

| 3  | Flu                   | jo de Diseño Digital                                                     | 21  |

|    | 3.1                   | Estructura de directorios y archivos                                     | 22  |

|    | 3.2                   | Scripts para diseño de front end                                         | 27  |

|    |                       | 3.2.1 Script de síntesis lógica                                          | 27  |

|    |                       | 3.2.2 Simulación Lógica: evaluación pre y post síntesis lógica           | 37  |

|    | 3.3                   | Scripts de diseño back end                                               | 39  |

|    |                       | 3.3.1 Script de implementación o síntesis física                         | 39  |

ii Índice general

|              |       | 3.3.2 Script de simulación física: evaluación post implementación           | 48        |

|--------------|-------|-----------------------------------------------------------------------------|-----------|

|              |       | 3.3.3 Script de análisis de temporizado estático STA                        | 48        |

|              | 3.4   | Script de síntesis de IP Cores y bibliotecas autónomas                      | 52        |

|              | 3.5   | Análisis de resultados: Scripting                                           | 54        |

| 4            | Sínt  | esis lógica de un microprocesador RISC-V                                    | <b>57</b> |

|              | 4.1   | Estrategia de síntesis y validación                                         | 59        |

|              |       | 4.1.1 Restricciones del diseño                                              | 59        |

|              |       | 4.1.2 Comprobación de la síntesis                                           | 60        |

|              | 4.2   | Análisis de resultado: síntesis lógica del ASP                              | 61        |

|              |       | 4.2.1 Evaluación pre síntesis                                               | 61        |

|              |       | 4.2.2 Evaluación post síntesis                                              | 63        |

| 5            | Imp   | lementación física de la FPU del ASP y bloques de memoria                   | 69        |

|              |       | 5.0.1 Análisis de los resultados obtenidos en la implementación de la FPU . | 70        |

|              |       | 5.0.2 Reportes del análisis de temporización estática (STA)                 | 84        |

|              | 5.1   | Integración de los <i>IP Cores</i> de memorias SRAM                         | 88        |

| 6            | Con   | clusiones y Recomendaciones                                                 | 91        |

|              | 6.1   | Conclusiones                                                                | 91        |

|              | 6.2   | Recomendaciones                                                             | 91        |

| Bi           | bliog | rafía                                                                       | 93        |

| $\mathbf{A}$ | Hoj   | a de Información del Proyecto                                               | 97        |

# Índice de figuras

| 1.1 | propia, basada en la expuesta en [8]                                                                                                                                                                                                                                                                                                                                                            | 2    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.2 | Diagrama de bloques del Sistema de Reconocimiento de Patrones Acústicos.<br>Figura de autoría propia, basada en la expuesta en [8]                                                                                                                                                                                                                                                              | 3    |

| 2.1 | Tipos de Diseño de Circuitos Integrados. Figura de autoría propia                                                                                                                                                                                                                                                                                                                               | 10   |

| 2.2 | Diagrama de Gajski. Espiral que ilustra el flujo digital de diseño de circuitos integrados y cuyas arístas establecen los ámbitos por los que debe atravesar el diseño. Figura de autoría propia basada en lo expuesto en la sección 1.6 de                                                                                                                                                     |      |

|     | [29]                                                                                                                                                                                                                                                                                                                                                                                            | 13   |

| 2.3 | Esquema representativo e ilustrativo del flujo de diseño de circuitos integrados digitales. Figura de autoría propia.                                                                                                                                                                                                                                                                           | 14   |

| 2.4 | Esquema ilustrativo del flujo de diseño de circuitos integrados digitales, en la etapa inicial de síntesis lógica (conocida como etapa de front end). Imagen de autoría propia                                                                                                                                                                                                                  | 16   |

| 2.5 | Esquema ilustrativo del flujo de diseño de circuitos integrados digitales, enfo-<br>cado a las herramientas de síntesis física, en esencia las herramientas de <i>Back</i>                                                                                                                                                                                                                      | 10   |

|     | End. Figura de autoría propia                                                                                                                                                                                                                                                                                                                                                                   | 18   |

| 3.1 | Esquema de la jerarquía de directorios y archivos para implementar el flujo de diseño digital. El archivo .gitignore es un archivo oculto, que contiene información para que la herramienta de control de versiones usada en el DCILab opere de forma personalizada. Este archivo carece de relevancia para la estructura del flujo; sin embargo, permite mantener un repositorio más ordenado. | O.F. |

| 3.2 | Figura de autoría propia                                                                                                                                                                                                                                                                                                                                                                        | 23   |

|     | autoría propia.                                                                                                                                                                                                                                                                                                                                                                                 | 24   |

| 3.3 | Esquema ilustrativo de la relación entre los scripts de bash que inicializan las herramientas EDA y crean las varibles que contienen los punteros a los                                                                                                                                                                                                                                         |      |

|     | archivos y la biblioteca de la tecnología de integración. Figura de autoría propia.                                                                                                                                                                                                                                                                                                             | 25   |

**iv** Índice de figuras

| 3.4  | propia                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

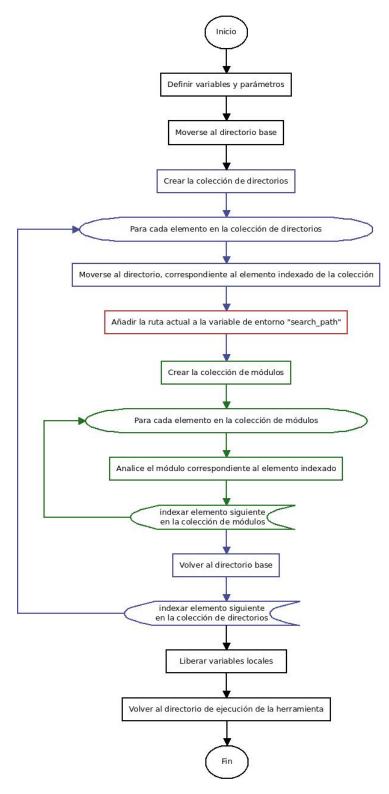

| 3.5  | Algoritmo recursivo de lectura y análisis de los módulos <i>HDL</i> del diseño. Figura de autoría propia                                                                                                                                                                                                                                                                                                                  |

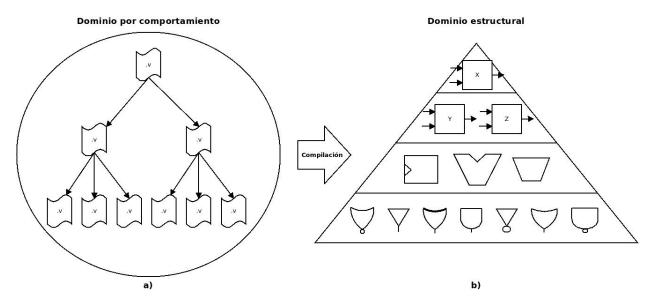

| 3.6  | Ilustración del proceso de compilación de front end. En figura $a$ ) se aprecia la estructura jerárquica de códigos en HDL, y en la figura $b$ ) la jerarquía abstraída, implementada mediante distintos niveles de elementos digitales, pasando desde funciones complejas, módulos digitales avanzados, hasta compuertas lógicas fundamentales. Aunque no siempre se llega hasta estas últimas. Figura de autoría propia |

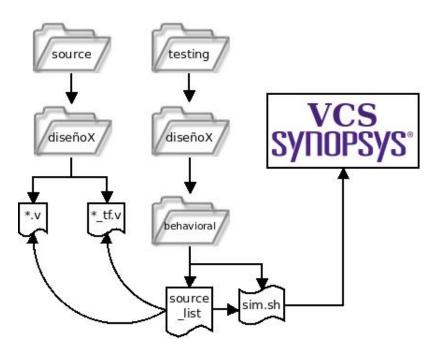

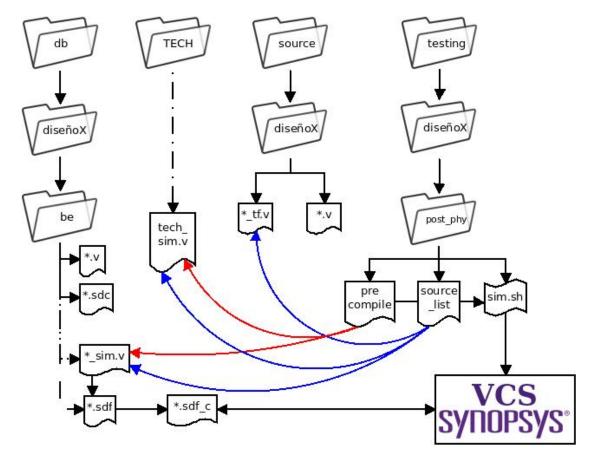

| 3.7  | Estructura del script de simulación por comportamiento. El archivo source_list apunta hacia el RTL, que se ubica en algún subdirectorio de source. El script de simulación llama al archivo source_list al invocar al simulador VCS.                                                                                                                                                                                      |

| 3.8  | Figura de autoría propia                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.9  | Primer propuesta de distribución de potencia para el trazado de la unidad aritmética de punto flotante discutida en el capítulo 4                                                                                                                                                                                                                                                                                         |

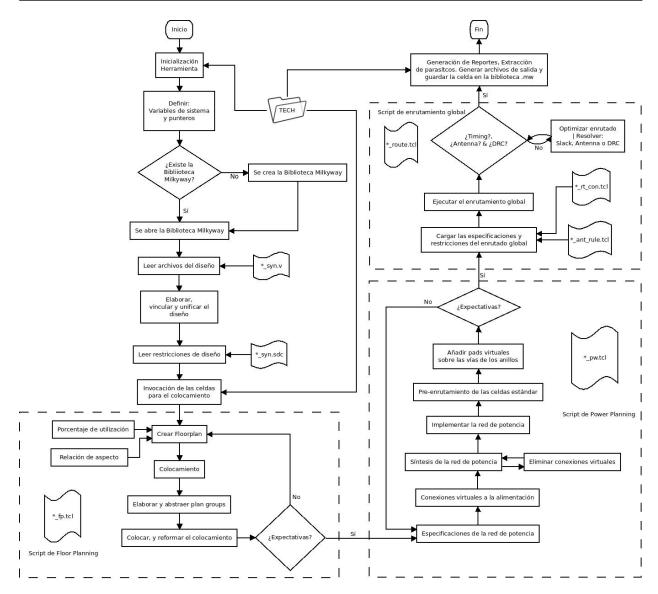

| 3.10 | Diagrama de flujo que expone el proceso genérico de la implementación física en la herramienta IC Compiler. Figura de autoría propia                                                                                                                                                                                                                                                                                      |

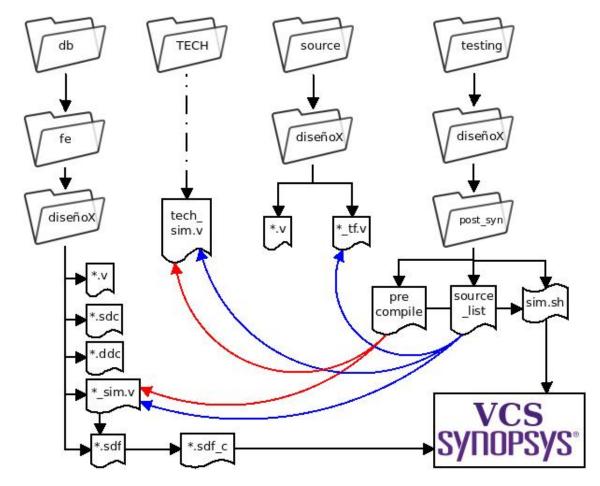

| 3.11 | Estructura del script de bash para la simulación post implementación. Figura de autoría propia                                                                                                                                                                                                                                                                                                                            |

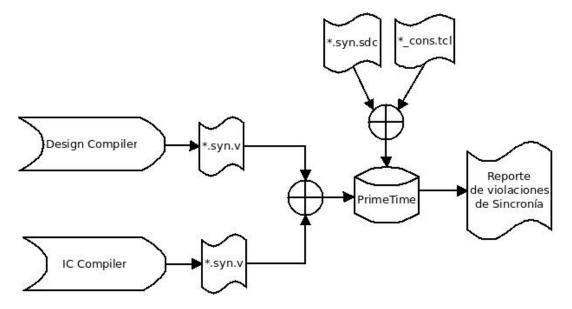

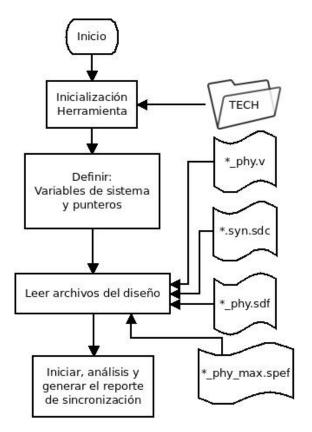

| 3.12 | Diagrama de flujo del análsis de temporizado estático (STA). Figura de autoría propia                                                                                                                                                                                                                                                                                                                                     |

| 3.13 | Diagrama de flujo del script para un análisis básico de STA en la herramienta PrimeTime de Synopsys. Figura de autoría propia                                                                                                                                                                                                                                                                                             |

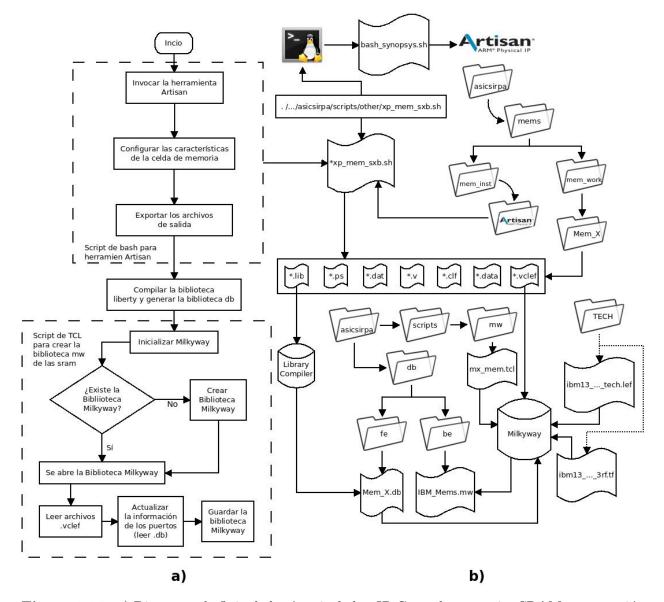

| 3.14 | <ul> <li>a) Diagrama de flujo de la síntesis de los IP Cores de memorias SRAM y generación de las bibliotecas autónomas.</li> <li>b) Estructura de directorios y archivos que intervienen en la síntesis de los IPcores de las memorias, herramientas involucradas y los archivos generados.</li> <li>Figuras de autoría propia</li></ul>                                                                                 |

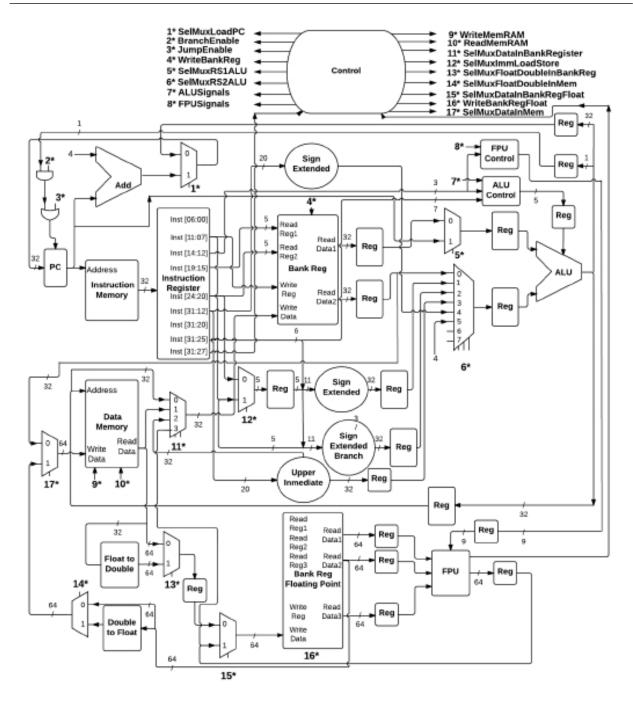

| 4.1  | Diagrama funcional del microprocesador ASP. RISC-V. Imágen tomada del trabajo [8], con la autorización del M.Sc Salazar                                                                                                                                                                                                                                                                                                   |

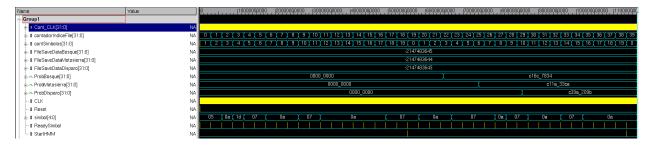

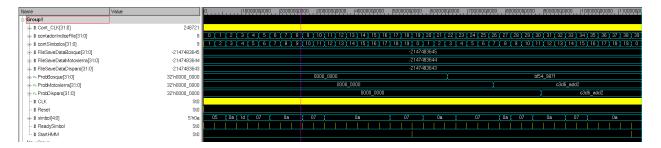

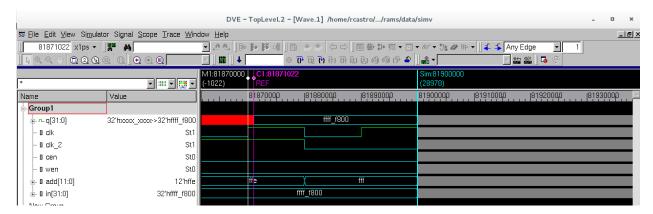

| 4.2  | Resultado de la simulación por comportamiento del ASP con la FPU diseñada en [24]. Según lo estipulado por el M.Sc Salazar en [8]. Esta es la referencia derada para esta trabajo.                                                                                                                                                                                                                                        |

| 4.3  | dorada para este trabajo                                                                                                                                                                                                                                                                                                                                                                                                  |

Índice de figuras

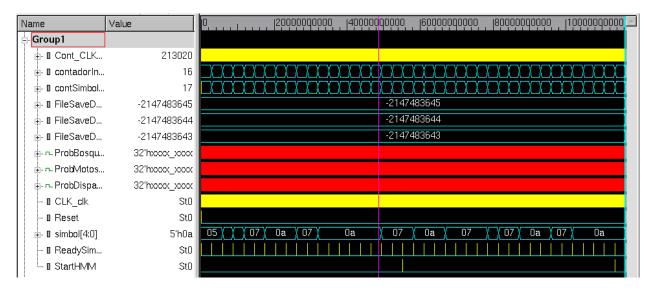

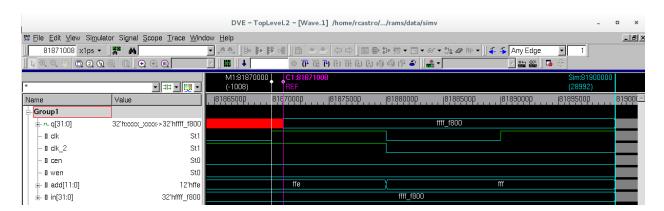

| 4.4 | Resultado de simulación post síntesis lógica del ASP, con la FPU de [25, 35]. Nótese la existencia de señales indefinidas. Un análisis más detallado mostrará violaciones en la restricción de tiempo de mantenimiento en el resultado de la                                                                              |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | síntesis lógica                                                                                                                                                                                                                                                                                                           | 62  |

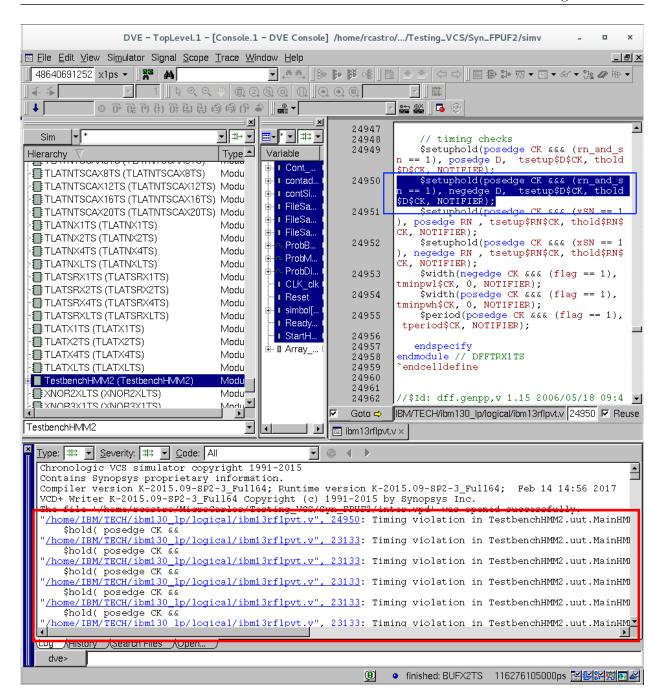

| 4.5 | Detalle de los resultados de la verificación post-síntesis, proporcionados por VCS. Nóstese la violación de hold. Esto implica que hay que corregir el problema, ya sea desde DesignCompiler, o modificando el RTL si el DC no logra su cometido                                                                          | 66  |

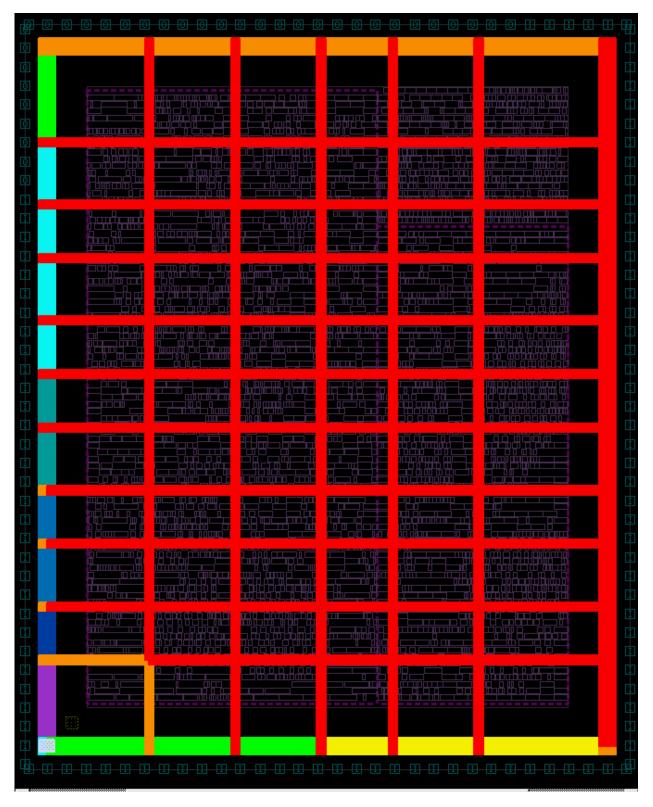

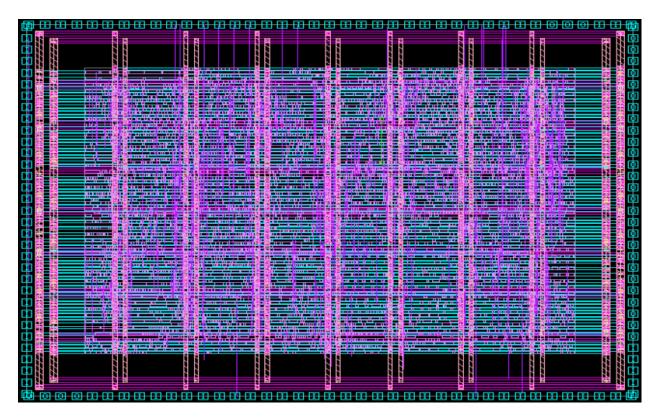

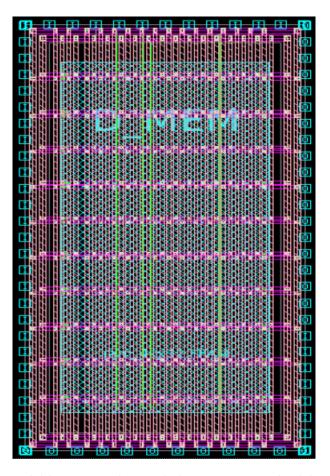

| 5.1 | Foto captura del layout de la celda física generada para la unidad de punto flotante del ASP                                                                                                                                                                                                                              | 71  |

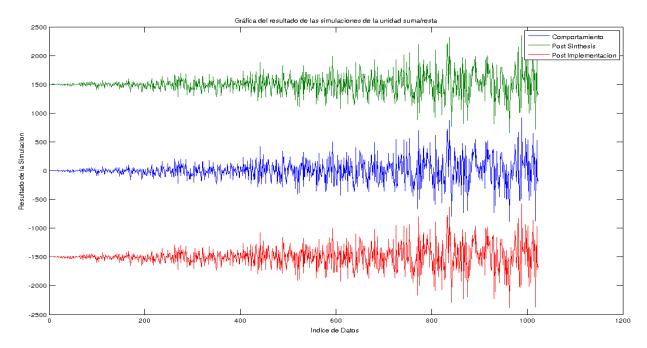

| 5.2 | Gráfico de los resultados de las distintas simulaciones asociadas con el módulo de suma y resta de la FPU. Observar que hay un desface entre los datos, hecho                                                                                                                                                             |     |

| - 0 | a drede para apreciar mejor la dinámica de las distintas gráficas                                                                                                                                                                                                                                                         | 86  |

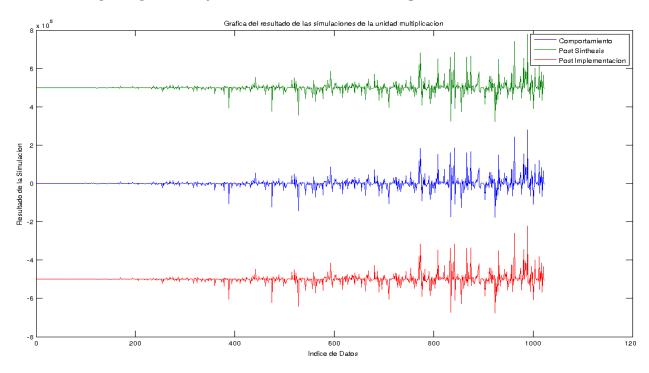

| 5.3 | Gráfico de los resultados de las distintos simulaciones asociadas con el módulo de multiplicación con signo de la FPU Observar que hay un desface entre los                                                                                                                                                               | 0.0 |

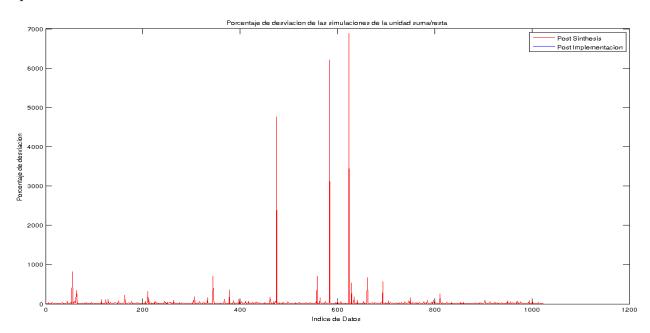

| 5.4 | datos, hecho a drede para apreciar mejor la dinámica de las distintas gráficas. Gráfica del porcentaje de desviación, de las simulaciones post síntesis de la unidad de suma y resta de la FPU, respecto a simulación por comportamiento. Se que la simulación post síntesis lógica, presenta algunas incongruencias para | 86  |

|     | ciertos datos, mientras la síntesis física es congruente                                                                                                                                                                                                                                                                  | 87  |

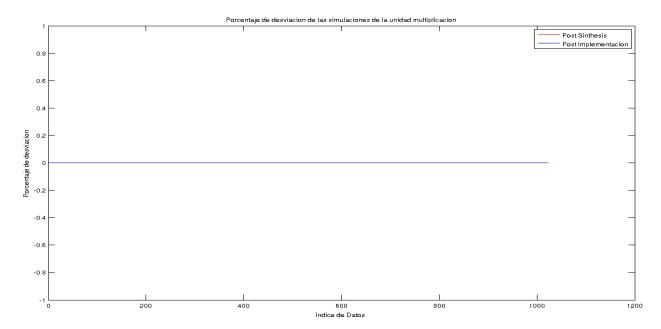

| 5.5 | Grafica que muestra el porcentaje de desviación, de las simulaciones post síntesis de la unidad de multiplicación de la FPU. Observe que ambas líneas son perfectamente horizontales, lo que indica que la simulaciones post síntesis son consistentes con la de comportamiento                                           | 88  |

| 5.6 | Foto captura del layout resultante de la impementación del <i>IP Core</i> de una                                                                                                                                                                                                                                          |     |

|     | memoria SRAM de 4kx32                                                                                                                                                                                                                                                                                                     | 89  |

| 5.7 | Simulación post implementación física del <i>IP Core</i> para la memoria de datos                                                                                                                                                                                                                                         |     |

|     | (4kx32) con el modelo de retardos mínimos                                                                                                                                                                                                                                                                                 | 90  |

| 5.8 | Simulación post implementación física del IP Core para la memoria de datos                                                                                                                                                                                                                                                |     |

|     | (4kx32) con el modelo de retardos típicos                                                                                                                                                                                                                                                                                 | 90  |

vi Índice de figuras

# Índice de tablas

| 5.1 | Resumen del reporte de potencia de la FPU post síntesis lógica | 71 |

|-----|----------------------------------------------------------------|----|

| 5.2 | Resumen del reporte de potencia de la FPU post síntesis física | 72 |

viii Índice de tablas

# Índice de listados

| 3.1 | Directivas para crear las variables de entorno utilizadas por los scripts de las |    |

|-----|----------------------------------------------------------------------------------|----|

|     | herramientas e invocar el scritp de las herramientas de Synopsys                 | 24 |

| 4.1 | Reporte de temporizado del microprocesador ASP post síntesis lógica              | 63 |

| 4.2 | Reporte de área del microprocesador ASP post síntesis lógica                     | 67 |

| 5.1 | Reporte de área de la unidad de punto flotante de ASP post síntesis lógica.      | 72 |

| 5.2 | Reporte de área de la unidad de punto flotante de ASP post síntesis lógica.      | 73 |

| 5.3 | Reporte de temporizado del microprocesador ASP post síntesis lógica              | 73 |

| 5.4 | Reporte de temporizado de la FPU post síntesis lógica.                           | 76 |

| 5.5 | Reporte de temporizado del microprocesador ASP post síntesis lógica              | 79 |

| 5.6 | Reporte STA de la FPU. Anotaciones sobre el análisis entre registros y puer-     |    |

|     | tos                                                                              | 82 |

| 5.7 | Reporte STA de la FPU. Anotaciones sobre el análisis entre registros y puer-     |    |

|     | tos                                                                              | 84 |

Índice de listados

# Capítulo 1

### Introducción

#### 1.1 Entorno de la tesis

Costa Rica es uno de los países que se encuentran a la vanguardia en materia de conservación ambiental, esto debido al sistema de áreas protegidas, que cubre cerca del 25% del territorio nacional cuenta con alguna categoría de protección. Las políticas nacionales de protección no sólo abogan por preservar la flora y fauna local sino también por mantener un desarrollo sostenible garantizando la perpetuidad de los recursos naturales. [1]

Los recursos naturales son, innegablemente, el medio fundamental para el crecimiento integral de las sociedades modernas. Estos se encuentran implícitos en todas las actividades humanas y son indispensables para sostener el estilo de vida del ciudadano moderno, desde su nutrición, materia prima para la manufactura de la tecnología que emplea, los servicios que recibe, entre otros. [2]

Por otra parte la riqueza natural representa una gran fuente de ingresos económicos para el país, debido al turismo. Según el informe del ICT, durante el primer trimestre del 2015 al país arribaron por todas las vías de ingreso un total de 811,379 personas, mientras que para el primer trimestre del 2016 arribaron un total de 919,624 lo que representa un incremento del 13.3%. [3]

No obstante al marco jurídico en materia ambiental y los programas de protección ambiental hacia la flora y fauna, Costa Rica tiene serios problemas de caza furtiva y tala indiscriminada, pues los programas de conservación y la legislación actual son insuficientes para velar por la correcta protección de los recursos naturales (i.e. flora, fauna, minerales, etc), en mayor medida debido a la carencia de los fondos y personal necesarios para ejercer con más rigurosidad las políticas de conservación y penalización. De forma ilustrativa según el Sistema Nacional de Áreas de Conservación, en el 2014 eran necesarios, aproximadamente, 300 funcionarios dedicados al control y protección de las áreas protegidas (i.e. guardabosques) y el Estado era incapaz de hacer las contrataciones por falta de presupuesto. [1]

2 1.1 Entorno de la tesis

Dado el dilema expuesto, estatalmente, se han puesto en marcha diversas estrategias para enfrentar la problemática; sin embargo, aumentar el recurso humano no es la opción más rentable para el Estado, siendo probable que una densidad mayor de guardabosques tampoco sea la solución. Partiendo de estas premisas se ha optado por un cambio de visión en camino a resolver el problema. Se considera que la posible solución resida en el uso de tecnología para facilitar la labor de los guardabosques.

Esta propuesta de solución tecnológica consiste en la implementación de una Red Inalámbrica de Sensores (RIS) para vigilar de forma remota las zonas protegidas. Una RIS no es otra cosa que una serie de dispositivos autónomos distribuidos en un área de interés, utilizando elementos de instrumentación (i.e. sensores) para monitorear condiciones físicas o ambientales. Cada miembro de la red corresponde a un nodo [4]. Se considera que si la RIS no es la solución óptima, sí es una alternativa muy eficiente pues una RIS es capaz de medir parámetros, almacenarlos, procesarlos y enviarlos entre sí, lo cual permite ejecutar muchas de las labores realizables por un guardabosques. Como consideración especial, debe tenerse en cuenta que en un bosque no hay un acceso fácil a fuentes de alimentación eléctrica, por lo que es imperativo que la RIS tenga un bajo consumo energético.

En respuesta a esta restricción, se realizó el proyecto: "Sonidos Ilegales" [5] de la Escuela de Ingeniería Electrónica del Tecnológico de Costa Rica (TEC), el cual refiere a la implementación de un sistema de reconocimiento de sonidos de motosierras, disparos de armas de fuego, como indicadores indirectos de actividades de tala y caza ilegales en zonas protegidas. Este proyecto consistió en el diseño de un sistema de hardware SoC <sup>1</sup> de bajo consumo energético el cual llevaría a cabo las operaciones de procesamientos mencionas de la RIS. [6, 7]

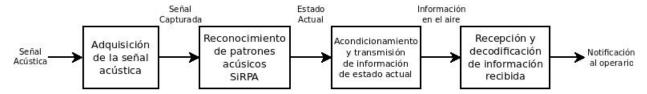

El funcionamiento de la *RIS* propuesta consistió en la obtención de muestras de señales acústicas del medio, que en este caso se trata de un bosque. Seguidamente, los datos eran procesados aplicando reconocimiento de patrones. En caso de encontrar un estado de alarma: disparo o motosierra, se activaría el bloque de transmisión de información donde posteriormente la persona a cargo de la protección de la zona (el guardabosques), debía recibir una notificación donde se le indicará el tipo de suceso y en cual nodo de la red se hizo de detección. En la figura 1.1 se muestra un diagrama de bloques de un nodo de la RIS que se propuso, la cual permite, a groso modo, entender el funcionamiento de la misma.

**Figura 1.1:** Procesamiento realizado por cada nodo miembro de la RIS. Figura de autoría propia, basada en la expuesta en [8].

<sup>&</sup>lt;sup>1</sup>SoC: Single on Chip. Sistema integrado en un chip

1 Introducción 3

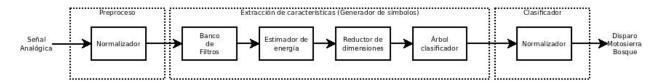

En cuanto al procesamiento, el bloque llamado  $SiRPA^2$ , sigue una estructura estándar de un sistema de reconocimiento de patrones, compuesto de un bloque de preprocesado, una etapa de identificación/extracción de características fundamentales y un bloque de clasificación.

El preproceso consiste en acondicionar la señal analógica, que significa normalizar y digitalizar la señal acústica. El bloque de identificación está compuesto por una batería de filtros, un estimador de energía, un reductor de dimensiones y un árbol clasificador. En el banco de filtros el espectro de la señal acústica se separa en 8 bandas distintas y luego se estima la energía a cada banda.

Mediante una transformación lineal, el reductor de dimensiones proyecta la salida del estimador de energía, que se encuentra en un espacio de ocho dimensiones, a un espacio de tres dimensiones. Según lo predice la maldición de dimensionalidad, el conjunto de símbolos necesarios para describir de manera adecuada las observaciones realizadas es tres órdenes de magnitud superior si se emplea un espacio de ocho dimensiones en comparación a uno de tres. [10, 9]

El árbol binario o generador de símbolos, permite ubicar el centroide mas cercano a un patrón de entrada de tres dimensiones, según la distancia L1 o Manhattan. Consecuentemente, los símbolos discretos se generan asociándolos, a las trayectorias continuas en el espacio del vector tridimensional de entrada, que describe la señal acústica en un determinado instante. El árbol binario genera un alfabeto de 32 símbolos discretos. [11, 12, 13, 14]

La etapa de clasificación es la encargada de calcular la probabilidad de que un conjunto de símbolos de entrada, formen parte de una señal acústica, de acuerdo con las categorías: bosque, motosierra o disparo. En este bloque, se utiliza un clasificador basado en la técnica de modelos ocultos de Markov (HMM). En la figura 1.2 se muestra un diagrama de bloques ilustrando como funciona internamente el SiRPA.

**Figura 1.2:** Diagrama de bloques del Sistema de Reconocimiento de Patrones Acústicos. Figura de autoría propia, basada en la expuesta en [8].

<sup>&</sup>lt;sup>2</sup>SiRPA, es el acrónimo en español para Sistema de Reconocimiento de Patrones Acústicos

#### 1.2 Descripción del problema y justificación

Luego de muchas etapas iterativas en el diseño del SiRPA, el proyecto se encuentra codificado en un lenguaje de descripción de hardware (HDL). Se han efectuado pruebas usando plataformas de sistemas embebidos como Beagle Boards y textitFPGAs para la validación del diseño, se han publicado algunos papers al respecto, y se ha demostrado la viabilidad del proyecto, por lo que compete continuar la labor de implementar la codificación HDL a su etapa final, la cual consiste en la síntesis de los módulos descritos en HDL sobre un chip de silicio.

Durante el 2014 el *DCILab* contó con el apoyo del ingeniero argentino Dr. Juan Agustín Rodríguez, quien desarrolló un flujo de diseño digital sobre las herramientas de software Synopsys que implementan los módulos en HDL del *SiRPA* al silicio para el circuito integrado. El trabajo del Dr.Rodríguez quedó incompleto y el *SiRPA* no ha podido ser fabricado. Es por ello que el *DCILab* requiere terminar el trabajo empezado por el Dr. Rodríguez e integrar la parte final del *SiRPA*, que consiste en un microprocesador desarrollado por el Ing. M.Sc. Carlos Salazar García, para así dejar todo el proyecto *SiRPA* depurado y listo para su fabricación. Además el *DCILab* está interesado en que dicho proceso de síntesis quede documentado y se establezca una estructura de diseño digital genérica, capaz de ser adaptada para futuros proyectos.

Es posible fabricar estos prototipos vía MOSIS <sup>3</sup>, un consorcio que permite a universidades y pequeños farbicantes acceder a fábricas con costos manejables. [15]

#### 1.3 Síntesis del problema

El proyecto SiRPA se encuentra inconcluso y el DCILab requiere de una persona con conocimientos en microelectrónica capaz de someter los componentes del SiRPA a un flujo de diseño ASIC, y fabricar un prototipo SoC.

#### 1.4 Enfoque de la solución

#### 1.4.1 Generalidades de la solución

Dado que se requiere diseñar un circuito integrado digital que parte de una codificación HDL, es necesario desarrollar una jerarquía de diseño digital que permita realizar el layout de los módulos descritos en HDL, por lo que se necesita de una herramienta de software especializada para tal fin. Design-Compiler e IC-Compiler son herramientas interactivas de

<sup>&</sup>lt;sup>2</sup>Una FPGA (del inglés Field Programmable Gate Array) es un dispositivo electrónico que contiene bloques de lógica y electrónica digital que puede ser reconfigurada "in situ" mediante un lenguaje de descripción de hardware.

<sup>&</sup>lt;sup>3</sup>MOSIS (Metal Oxide Semiconductor Implementation Service)

1 Introducción 5

Synopsys que le permiten al usuario controlar el desarrollo del circuito integrado sobre el silicio, definiendo las características físicas como: conexión eléctrica, distribución espacial y física, limitaciones espaciales y sus implicaciones electromagnéticas para que su posterior fabricación e implementación física sean exitosas.

El proceso de diseño de un circuito integrado es lento, tedioso, y tiene un componente iterativo, lo que implica tiempo para que un ingeniero se familiarice con el flujo de diseño. Es por ello que aparte de crear el flujo de diseño de un chip sobre la herramientas, es conveniente establecer para futuros proyectos, una estructura de archivos y scripts, propios de las herramientas de Synopsys, para así facilitar el diseño y rediseño de proyectos futuros del DCILab. Como comprobación de la efectividad del flujo de diseño digital anteriormente mencionado, deberán someterse los componentes del ASP mediante las herramientas de Synopsys, para su posible fabricación a futuro, y establecer una documentación oportuna para agilizar el trabajo, de los colabores del DCILab en cuanto a síntesis sobre silicio respecta.

#### 1.4.2 Síntesis de la solución

Establecido el panorama anterior, la solución consiste en desarrollar una jerarquía de flujo de diseño digital en las herramientas de Synopsys, que permita someter los componentes del SiRPA (específicamente el microprocesador ASP) al proceso de síntesis al silicio, según las reglas de diseño del proceso de fabricación de IBM: 8RF de 0,13 micrómentros (IBM013), que es la tecnología a la cual tiene acceso el DCILab, y así contar con el proyecto SiRPA completo hasta la última etapa previa a su fabricación que podría hacerse vía MOSIS en un futuro. Cabe destacar que la índole del proyecto y las restricciones del laboratorio en términos de licencias de software solamente permiten una opción de EDA <sup>4</sup>, la cual es Synopsys.

### 1.5 Trabajos anteriores

SiRPA es un proyecto de investigación que ha sido explorado y analizado desde diversas perspectivas de solución cada investigador ha dado forma a cada etapa que componen el sistema. Tanto a nivel de software como a nivel de hardware, los aportes incluyen desde propuestas de diseño, implementación, mejoras o rediseño de etapas que han presentado problemas. Entre estos trabajos se encuentran los siguientes:

• En [16], se efectuó la primera prueba de concepto para evaluar la viabilidad de implementar el SiRPA. Se empleó el software MATLAB, para generar un modelo de alto nivel cuyo objetivo fue el análisis de las señales acústicas y se desarrolló una etapa de identificación de características utilizando la teoría de onditas (wavelets en ingles). Este trabajo constituye la primer referencia del sistema. La estrategia de extracción de características mediante onditas fue descartada posteriormente

<sup>&</sup>lt;sup>4</sup>EDA: Electronic Design Automation. Software usado en la síntesis de circuitos integrados

- En [17], se implementó el SiRPA en una FPGAutilizando el lenguaje de descripción de hardware VHDL. Aquí se estableció que el uso de un banco de filtros utilizando una misma unidad de filtro para cada una de las ocho bandas, como una metodología de clasificación idónea para los requerimientos de hardware del SiRPA. Es en este trabajo donde se intenta implementar por primera vez el algoritmo de HMM en hardware mediante un MAP (del ingles Matrix and Arrays Processor), el cual consiste una estructura digital cuya arquitectura se optimiza de acuerdo con la ejecución de operaciones en punto flotante en 32 bits de forma combinacional.

- En [18], se desarrolló un módulo reductor de dimensiones mediante la estrategia de transformación lineal, fundamentada en el algoritmo de discriminantes de Fisher. Este módulo permitió transformar un espacio de 8 dimensiones en un espacio de 3 dimensiones, que implica mayor facilidad en la clasificación de señales acústicas y ahorro energético, al disminuir la densidad de hardware.

- En [13], se desarrolló la herramienta HMMSoft que consiste en un software de alto nivel (lenguaje C/C++) con interfaz gráfica, capaz de realizar el entrenamiento del algoritmo de HMM utilizado por el clasificador. Esta aplicación permite identificar características de patrones acústicos lo cual contribuye a validar el reconocimiento de un audio en particular. Esta herramienta representa un hito considerable ya que mediante ella, es posible establecer un marco de referencia para la verificación funcional del sistema.

- En el trabajo de [9], se realizó la síntesis de la sección de extracción de los patrones acústicos y entrenamiento a partir de conjuntos de datos de audio similares a los que se esperara detectar. El proceso de extracción mencionado fue integrado a la aplicación HMMSoft [13]. Consecuentemente el proyecto SiRPA fue modelado en el lenguaje C, e implementado en un sistema embebido (BeagleBoard xM) [19] y usando la herramienta HMMSoft además del modelo en C del SiRPAse desarrolló el primer modelo de verficación para SiRPA

- En [20], se implementaron los módulos de hardware del reductor de dimensiones, generador de símbolos y una unidad de HMM en Verilog. Partiendo de la estructura de la unidad HMM desarrollada por [9] para el sistema embebido, en [20] se propone implemetar la unidad mediante una máquina microprogramada. Posteriormente al realizar pruebas sobre una FPGA, se observó que los resultados divergían de lo esperado según el modelo de [9] y por tanto clasificar los patrones acústicos correctamente es imposible. Según expone [8] el hardware presentó problemas de cálculo ya que los resultados tiendía a cero rápidamente debido a que en [20], no se consideraron los problemas de escalamiento que se describen ampliamente en [21].

- En [22], se expusp la verificación funcional de los módulos descritos en hardware que conforman el SiRPA.

1 Introducción 7

• En [23], se tomó como punto de partida el trabajo de [17] y se rediseñó la unidad contemplando efectos de submuestreo. De acuerdo con un análisis del bloque de reducción de dimensiones elaborado en [20] se estableció la necesidad de aumentar el formato de palabra de 16 a 24 bits. Por lo tanto se integraron además todos los bloques para formar la etapa de identificación o extracción de características. Finalmente, se evaluó la funcionalidad de esta etapa, tomando como referencia dorada el trabajo realizado en [9].

- En [8] se expone la necesidad de implementar la unidad de clasificación *HMM* mediante un microprocesador de aplicación específica ya que durante la experimentación en [23] se determinó que la unidad *HMM* implementada en [20] no era correcta.

- En cooperación con el trabajo de [8], se encuentra ella trabajo [24] donde se expone el proceso de diseño e implementación en un FPGA de la unidad de punto flotante (FPU) que usará el microprocesador de [8]. Posteriormente [25] expone la implementación de algunas mejoras para la FPU de [24].

#### 1.6 Objetivos

#### 1.6.1 Meta

Desarrollar un sistema de detección de disparos de armas de fuego, motosierras y otras actividades ilegales en un bosque, que esté implementado en un circuito integrado de bajo consumo energético.

#### 1.6.2 Objetivo general

Implementar un microprocesador de aplicación específica en una tecnología CMOS de 0,13 micrómetros para posteriormente ser integrado al proyecto SiRPA.

#### 1.6.3 Objetivos específicos

- Diseñar una jerarquía de scripting <sup>5</sup> que implemente el flujo de síntesis y simulaciones "Post Colocado y Enrutamiento" (*Place&Route*), para optimizar el tiempo del proceso de diseño para futuros proyectos.

- Sintetizar lógicamente de manera correcta los módulos RTL del Microprocesador de Aplicación Específica (ASP) sobre celdas estándar de una tecnología CMOS 0,13.

<sup>&</sup>lt;sup>5</sup>En informática un script es un archivo que contiene un conjunto de órdenes e instrucciones, las cuales ejecutan una función, ya sea en un lenguaje de programación o una herramienta de software. Se invita al lector a consultar un diccionario de términos de computación

8 1.6 Objetivos

• Sintetizar físicamente de manera correcta la unidad aritmética de punto flotante del microprocesador y las memorias de datos y programa del microprocesador ASP sobre la tecnología CMOS 0,13

# Capítulo 2

## Marco teórico

#### Diseño de ASICs

Este trabajo no pretende exponer el proceso de fabricación de un circuito integrado. En las secciones siguientes se expondrá brevemente, la metodología usanda para que a futuro se pueda llevar a cabo la implementación de un sistema sobre un dado de silicio <sup>1</sup> (silicon dice), usando las herramientas de Synopsys.

En primera instancia producir un sistema en un circuito integrado representa una mejor protección para los derechos intelectuales, pues su contenido difícilmente es reproducible. Un circuito integrado presenta enormes facilidades de portabilidad debido a su tamaño y su consumo energético. Lo cual es el principal objetivo del proyecto: "Sonidos Ilegales".

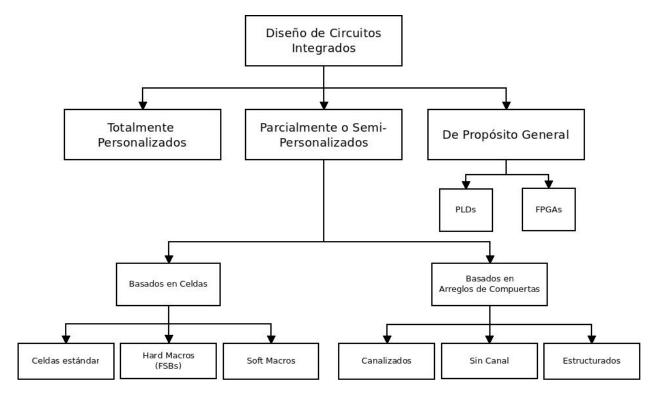

### 2.1 Tipos de diseño circuitos integrados digitales

La clasificación del diseño de circuitos integrados se puede apreciar en el esquema de la figura 2.1.

Como puede observarse el diseño de circuitos integrados (de aquí en adelante ICs<sup>2</sup>) se puede clasificar a grosso modo en tres tipos principales:

#### 2.1.1 ICs totalmente personalizados

En esta metodología de trabajo los diseñadores generan todas las celdas lógicas de acuerdo con las necesidades tiene el diseño que se pretende realizar, lo que contempla la concepción funcional, lógica y física de cada celda. También se desarrollan las máscaras necesarias para la fabricación del chip sobre la oblea de silicio.

<sup>&</sup>lt;sup>1</sup>Entendiendo por dado el espacio que el sistema propuesto ocupará sobre la oblea de silicio, al final del proceso de fabricación

<sup>&</sup>lt;sup>2</sup>ICs: acrónimo en inglés para circuitos integrados

Figura 2.1: Tipos de Diseño de Circuitos Integrados. Figura de autoría propia.

Empresas como Intel son un buen ejemplo de industrias dedicadas al desarrollo de circuitos integrados totalmente personalizados. Aquí los ingenieros invierten enormes cantidades de tiempo maximizando el aprovechamiento de cada micrómetro cuadrado disponible en el dado, lo que les permite incluir circuitos analógicos, optimizar celdas de memoria e incluso contemplar y mejorar la eficiencia mecánica de las estructuras de conexión y ubicación de los componentes del chip.

Esta es la metodología más costosa de todas, no obstante, es la respuesta adecuada si el diseñador necesita de unidades (celdas) más eficientes en términos energéticos y velocidad, de las que es capaz de encontrar en una biblioteca de celdas existentes. Es comúnmente utilizada por empresas dedicadas a la innovación y el desarrollo tecnológico.

#### 2.1.2 ICs programables

Estos consisten en dispositivos lógicos programables (PLDs), que son circuitos integrados con configuraciones estándar predeterminadas. Algunos ASICs para permiten la personalización de algunas funciones puntuales, por lo que aunque sean estructuras prediseñadas y flexibles, son consideradas como una rama del diseño de ICs.

2 Marco teórico

#### 2.1.3 ICs semipersonalizados

Son aquellos ICs para los cuales existe una biblioteca de celdas estándar y posiblemente todas las mascaras de diseño están disponibles. El uso de bibliotecas de celdas prediseñadas hace el diseño más fácil. Está metodología de diseño se subdivide en dos partes:

#### Basado en arreglos de compuertas

En este tipo de diseño los transistores se encuentran predefinidos en un patrón dado sobre en la oblea de silicio. Este patrón se conoce como arreglo base y a los elementos más pequeños se los conoce como celdas base o celdas primitivas.

En esta técnica el diseñador únicamente define la interconexión de las celdas usando para ello máscaras personalizadas. Así el diseñador escoge de entre una basta biblioteca de celdas prediseñadas y precaracterizadas. Las celdas lógicas suelen ser denominadas como macros. La razón de esto se debe a que el trazado de la celda base es el mismo para cada celda lógica y únicamente se personaliza la interconexión y el enrutado dentro de las celdas y con las celdas advacentes, de manera similar a un macro de software.

Existen subcategorías del uso de esta técnica, pero esa información excede el alcance de esta tesis, por lo que no serán expuestas. Se invita al lector a considerar una bibliografía pertinente [26, 27]

#### Basado en celdas estándar

Un circuito integrado basado en celdas estándar usa celdas lógicas prediseñadas como compuertas "Y", "O", "Flip Flops", "Multiplexores", etc.. Estas celdas se conocen como celdas estándar.

Suele usarse el término *CBIC* para esta categoría. El área de ubicación de las celdas estándar en un *CBIC* se construye en hileras, de manera similar a una pared de ladrillos. Las celdas estándar pueden y suelen ser utilizadas en conjunto a microcontroladores, o microprocesadores, conocidos como "Mega celdas". Este término también se emplea para bloques totalmente personalizados, y suelen ser denominados como: "Macros a Nivel de Sistema (SLMs)", "Mega Funciones", "Bloques Fijos", o "Bloques Funcionales Estándar (FSBs)".

En esta metodología es diseñador define únicamente la colocación y el enrutado (interconexión entre celdas estándar) de las celdas estándar; sin embargo, estás pueden ser colocadas libremente en el área disponible del dado. Esto implica que las máscaras de fabricación en un *CBIC* son únicas para cada cliente.

Usar *CBICs* tiene enormes ventajas ya que permite hacer diseños más flexibles y optimizarlos en términos de aprovechamiento de área, velocidad o consumo energético. Adicionalmente las bibliotecas de celdas estándar suelen ofrecer las mismas celdas estándar prediseñadas para cumplir distintas las expectativas de desempeño, enfocadas a tamaño, velocidad o energía.

Las principales desventajas consisten en que el tiempo necesario para el diseño suele ser elevado, debe comprarse una biblioteca de celdas estándar, y se está sujeto a las restricciones de ésta, y finalmente las máscaras de fabricación serán nuevas con cada nuevo diseño o versión de diseño, lo cual implica tiempo adicional, además de costos adicionales por parte del fabricante.

La información de esta sección se tomó a partir de las fuentes [28, 26, 28]

# 2.2 Flujo de diseño digital para el diseño de circuitos integrados digitales

Dada la complejidad en el proceso de diseño de circuitos integrados, es imperativo llevar a cabo un diseño estructurado, que use los principios de jerarquización, modularidad, regularidad y localidad para manejar la complejidad del diseño.

El diseño digital VLSI suele ser particionado en cinco niveles de abstracción: diseño de arquitecturas, diseño de microarquitecturas, diseño lógico, diseño de circuitos y diseño físico. Estas etapas son ejecutadas en paralelo, y en muchas ocasiones son depedientes entre si.

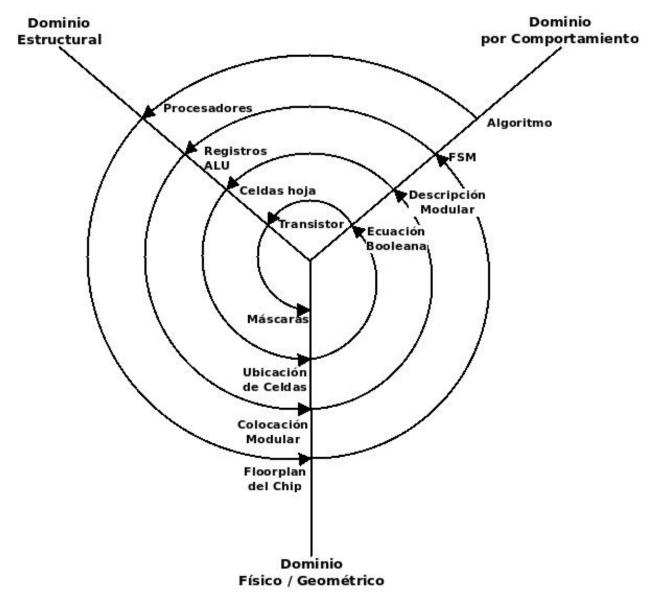

Una manera alternativa de analizar el diseño estructurado es mediante el "diagrama Y" mostrado en la figura 2.2.

El diagrama de Gajski o diagrama Y, permite entender el concepto de abstracción en el diseño digital, pues se parte desde un concepto general de diseño y al interiorizar en el diagrama se desvelan las etapas que llevan hasta la fabricación correcta del circuito integrado.

El proceso de diseño puede verse como la transformación desde un dominio hacia otro manteniendo la equivalencia de los dominios. Las descripciones por comportamiento se transforman en descripciones estructurales y estas a su vez son transformadas en descripciones físicas. Cada transformación es validada, ya sea manualmente o mediante herramientas automatizadas. La especificación jerárquica de cada dominio y sucesivamente detallando sus niveles de abstracción es lo que permite diseñar grandes sistemas.

La razón para describir en detalle los niveles de abstracción y los respectivos dominios es para definir un proceso de diseño en el cual la función final del sistema es capaz de rastrearse hasta la descripción por comportamiento inicial.

El diagrama Y muestra las transformaciones entre cada dominio y las variaciones entre los niveles de abstracción. El flujo de diseño procede desde los anillos exteriores hacia los interiores, profundizando en niveles de abstracción cada vez más complejos, de acuerdo a una jerarquía establecida.

Para más detalles ir a la sección 1.6 de [29].

2 Marco teórico

Figura 2.2: Diagrama de Gajski. Espiral que ilustra el flujo digital de diseño de circuitos integrados y cuyas arístas establecen los ámbitos por los que debe atravesar el diseño. Figura de autoría propia basada en lo expuesto en la sección 1.6 de [29].

#### 2.2.1 Generalidades del flujo de diseño digital

Como se mencionó en el apartado anterior, el diseño comienza a dar sus pasos en cuanto es concebida una función o proceso y su comportamiento ha sido modelada en un algoritmo, ya sea secuencial, concurrente o una mezcla de ambos. Este algoritmo se traduce a un lenguaje estandarizado, el cual en el caso de los circuitos integrados digitales corresponde a un HDL, que en términos concretos es la descripción digital del circuito integrado o el modelo digital.

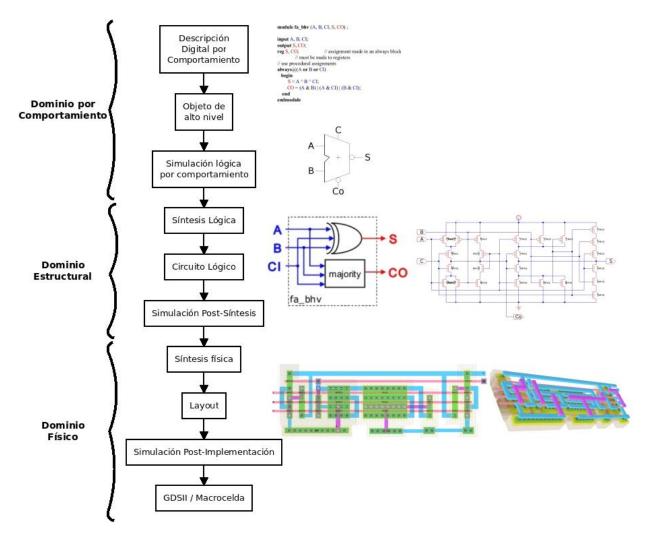

**Figura 2.3:** Esquema representativo e ilustrativo del flujo de diseño de circuitos integrados digitales. Figura de autoría propia.

Partiendo del modelo digital se puede hacer una verificación de comportamiento, que en términos técnicos se denomina simulación lógica. El modelo digital no es más que un objeto de alto nivel capaz de emular el comportamiento deseado. Su utilidad es poca para el diseñador, ya que no provee datos sobre el desempeño del diseño, únicamente provee información a nivel de comportamiento; sin embargo, es el punto de partida en el flujo de diseño.

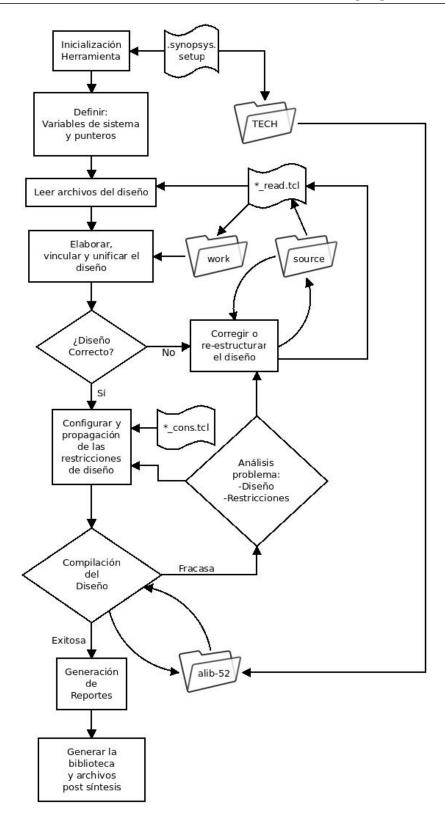

Una vez que la simulación lógica es satisfactoria, se procede a usar el modelo por comportamiento y asociar los módulos descritos en él, con unidades lógicas provistas de características de retardos (sincronización de señales), consumo energético, y área, las cuales se encuentran en la biblioteca de la tecnología que se usará en la fabricación. A este proceso se le conoce como síntesis lógica, y genera una base de datos que contiene datos de las celdas estándar y las conexiones entre ellas para ejecutar las funciones abstraídas del modelo de comportamiento.

2 Marco teórico 15

La base de datos creada en el proceso de síntesis permite generar un nuevo modelo codificado en HDL y una primera aproximación del desempeño de los módulos diseñados, i.e. un modelo con la información sobre los retardos de propagación de las señales en las celdas y entre las mismas, un presupuesto de la energía disipada y el área necesaria para ubicar las celdas usadas. Este nuevo modelo, denominado como modelo post-síntesis nuevamente se simula con el mismo arreglo o banco de pruebas usado en la simulación por comportamiento.

La simulación post-síntesis permite observar el retardo de propagación de las señales, y confirmar si las expectativas de sincronización son alcanzadas. También permite verificar si los datos son generados en los plazos necesarios, y poder garantizar una funcionalidad correcta de los módulos y el diseño en lo concerniente al desempeño de las celdas estándar.

Cuando los resultados obtenidos en la síntesis lógica y la simulación respectiva sean satisfactorios, se toma el modelo post-síntesis y se usa esta información para empezar con el plano de piso (floorplan) del chip. Las celdas estándar son invocadas a un área determinada, y posteriormente se establecen las conexiones que permiten implementar los módulos abstraídos en la primera etapa del diseño (el modelo de comportamiento). Este proceso recibe el nombre de síntesis física o implementación física, en esta tésis se usará la palabra síntesis para referirse a la síntesis lógica, y la palabra implementación será usada para referirse a la síntesis física).

Posteriormente, se genera una nueva base de datos con información más precisa sobre el diseño. Retardos debido a efectos parasíticos, distancia del recorrido de las señales, perdidas resistivas del alambrado, y otros efectos que serán expuestos más adelante.

Nuevamente se genera una base de datos con la información del colocamiento y el enrutado, que incluye modelos de sincronía y potencia más completos, y otra representación HDL del diseño post implementación. Esta etapa permite obtener una respuesta más precisa de diseño. Al igual que en la etapa anterior, se crean reportes de consumo energético, aprovechamiento de área, calidad de resultados (QOR, que es un compendio de la información más relevante de todos los reportes generados), etc.

Cuando una simulación post-implementación es satisfactoria se procede a dar por concluido el flujo, y a continuación se establecen dos panoramas:

En el primer caso nuestro diseño está completo por lo que se procede a compilar la base de datos en un archivo estándar para condensar la información necesaria para el fabricante. Aquí se valora si el diseño tiene probabilidad alta de ser fabricado con éxito, siendo así la información suministrada será usada para desarrollar las máscaras necesarias para la construcción del chip.

El segundo escenario consiste en que el diseño en el que se ha estado trabajando no es el producto final, sino que forma parte de otro diseño más complejo y grande, el cual aún no haya sigo terminado. En ese caso la base de datos servirá para generar una macro celda que será utilizada en diseños posteriores.

En la figura 2.3 se aprecia un resumen gráfico de la explicación anterior.

### 2.2.2 Flujo de diseño digital en las herramientas de Synopsys

Synopsys es una empresa que brinda herramientas de diseño asistido por computadora (CAD), para la automatización de procesos en el diseño de circuitos integrados. El flujo de diseño digital suele ser similar independientemente del proveedor de las herramientas; sin embargo, esta tesis gira entorno a los softwares de Synopsys, por lo que se expondrá la metodología de diseño usando este proveedor.

### 2.2.3 Front End

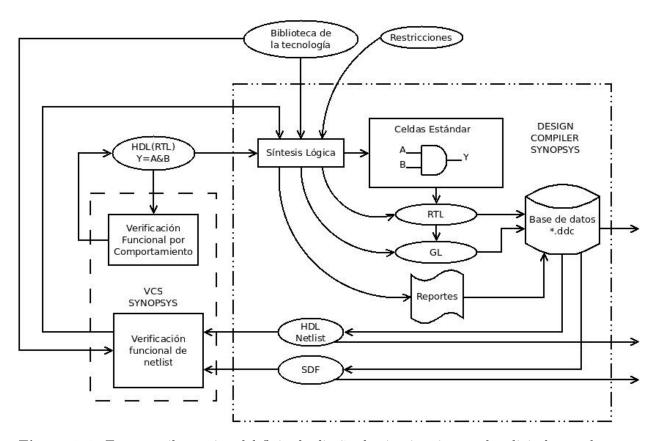

**Figura 2.4:** Esquema ilustrativo del flujo de diseño de circuitos integrados digitales, en la etapa inicial de síntesis lógica (conocida como etapa de front end). Imagen de autoría propia.

El término Front End, está asociado a la jerga del desarrollo de software, y significa interfaz, que no tiene mucho que ver con el diseño de circuitos integrados. Una traducción más literal, y por lo tanto, menos elegante del concepto sería "fachada", y es en esencia con lo que el diseñador interactúa en la primer etapa del diseño.

2 Marco teórico

Al decir que el diseñador interactúa con una fachada, se debe entender que el diseñador trabaja con el cascarón de un elemento que intrínsecamente no es circuito electrónico como tal, si no un modelo abstracto que presenta un comportamiento de causa efecto, el cual, naturalmente, es acorde a la semántica de la lógica digital, o lógica binaria. Recurriendo nuevamente a la jerga del software, podemos entender el front end o fachada como aquello relacionado con un objeto de alto nivel, que ofrece un vector de respuestas de acuerdo con la dinámica de un vector de estímulos.

El diseñador comienza a acercarse al diseño del circuito integrado, considerando y definiendo los aspectos principales de la fachada. Retomando el diagrama de Gajski (figura 2.2), el proceso de "Front-End" consiste en la transición del modelo de comportamiento a un modelo estructurado, que se asocia con las funciones de las celdas estándar ofrecidas por la tecnología y el fabricante.

Condensando lo anterior, las herramientas de *front end* de un proveedor, son aquellas que ejecutan o facilitan el proceso de síntesis lógica en el flujo digital del diseño de circuitos integrados. En el caso de Synopsys, estas herramientas son principalmente Design Compiler y VCS, existen otras herramientas adicionales asociadas a la familia de Design Compiler, VCS y el Shell de Design Compiler son las principales y suelen ser suficientes.

En la figura 2.4 se aprecia un diagrama que ilustra como el proceso expuesto en la sección 2.2.1, se implementa mediante las herramientas de Synopsys todos los procesos en el diseño de circuitos integrados tienen un componente iterativo, y en este diagrama se aprecia como antes de avanzar en el flujo, se atraviesa por etapas a las que se recurre con frecuencia (etapas de simulación de comportamiento y de post síntesis). La depuración de la etapa de síntesis es esencial para garantizar el éxito final del proyecto, por lo que las simulaciones tienen una gran importancia.

Cómo se observa desde el diagrama de Gajski (figura 2.2), las herramientas de front end traducen el diseño por comportamiento en modelos de altos nivel de circuitos digitales, aunque como tal no se trabajan con circuitos lógicos reales. Para efectos prácticos el diseñador nunca trabaja realmente con elementos lógicos y digitales: las herramientas proveen la virtualización del comportamiento diseñado, mediante una biblioteca de simulación. Las celdas estándar abstraídas en el proceso de síntesis se comportarán como un elemento de circuito digital real. De ahí que se pueda validar si la etapa de síntesis cumple las expectativas del diseñador.

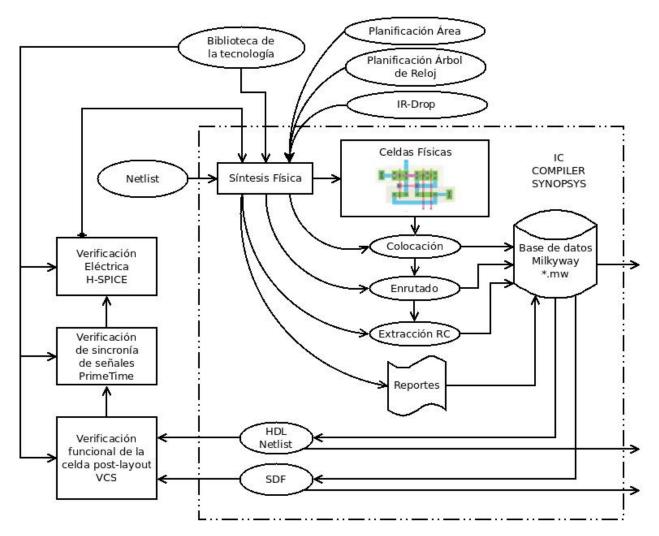

#### 2.2.4 Back End

**Figura 2.5:** Esquema ilustrativo del flujo de diseño de circuitos integrados digitales, enfocado a las herramientas de síntesis física, en esencia las herramientas de *Back End.* Figura de autoría propia.

El back end refiere a aquellos procedimientos relacionados con la constitución interna de un proyecto, nuevamente se emplea el anglicismo "Back End" para referirse a dichos procesos. No existe un concepto en español capaz de traducir el significado de esta palabra, pero se podría entender como todos aquellos aspectos ocultos al macro diseñador, entendiendo por oculto, una serie de elementos compuestos por elementos más simples hasta llegar a las unidades fundamentales de la electrónica moderna, i.e. transistores. Una analogía curiosa, y que ilustra bien esta situación es la de la muñeca matryoshka [30]: cada muñeca contiene a otra muñeca más pequeña, y se interioriza así hasta alcanzar una pequeña muñeca que no contiene a ninguna otra.

2 Marco teórico 19

En el proceso de diseño de circuitos integrados semipersonalizados, y basados en celdas estándar, el diseñador no alcanza a trabajar directamente con transistores, o con los elementos que componen las celdas, sino que da por hecho que las celdas estándar son funcionales y a partir de ellas (las celdas estándat) se generan nuevas macroceldas, las cuales ejecutarán las funciones macromodeladas con el RTL del diseño.

En síntesis de lo anterior, el diseñador de "back end" trabaja con las etapas ocultas para los diseñadores de comportamiento, y síntesis del diseño, dónde los primeros establecen la semántica del diseño, y los segundos generan cajas negras que realizan las funciones descritas por sus antecesores. Estas cajas negras manifiestan el comportamiento de una unidad electrónica real, en términos de consumo energético, área, y tiempos de propagación de señales, pero no dejan de ser modelos de alto nivel que no son circuitos electrónicos como tales, y es por ello que ha esta etapa se le denomina fachada.

En el proceso de back end las cajas negras abstraídas del proceso de síntesis, adquieren información más realista y equivalente a la de una celda física real. Esto se aprecia en la figura 2.3, donde en el extremo derecho de la figura se observan los productos de las distintas etapas del flujo:

En el dominio estructural (donde operan las herramientas de síntesis lógica) se muestran los bloques funcionales a nivel lógico.

Al descender en el flujo, se aprecia que la celda estándar es abstraída del diseño estructural, i.e. se asocia con una celda trazada (layout), donde pueden observarse: los metales que interconectan las celdas y los transistores que componen las celdas.

Las herramientas de back end se encargan de facilitar el colocado y enrutado de las celdas estándar que se abstrajeron de la síntesis lógica. En el back end se asocia la base de datos post síntesis con la base de datos de la tecnología, invocando celdas físicas para generar un nuevo layout que implemente el diseño sintetizado. Para esta sección del diseño, se utiliza la herramienta IC Compiler, que permite al diseñador establecer los criterios de optimización del trazado en términos de aprovechamiento de área, colocación selectiva para mejorar la eficiencia del consumo energético, sincronización de señales críticas (tal como la señal de reloj), definir criterios de alambrado (enrutado) para sopesar las pérdidas resistivas, y controlar fenómenos de electromigración y radiación o antena.

# Capítulo 3

# Flujo de Diseño Digital de Circuitos Integrados con las herramientas de Synopsys. Estructura de scripting

A continuación se detalla la estructura propuesta para implementar un flujo de diseño de circuitos integrados, y se expone como fueron sometidos los módulos de un microprocesador de aplicación específica basado en la plataforma abierta RISC-V. Con el fin de demostrar la efectividad del flujo de diseño digital propuesto. Esta estructura está basada en el manual sobre el uso de las herramientas de Synopsys en el flujo de diseño de ASICs, que ya ha sido desarrollado en el DCILab [31].

La estructura objetivo para el presente proyecto de graduación dista considerablemente de la propuesta en [31] y que a su vez está basada en el manual [32]. En estos trabajos las estructuras se basan en ejemplos simples con diseños *HDL* relativamente pequeños. Para este trabajo se toma como premisa que se trabaja con diseños muy grandes por lo que se requiere de mayor eficiencia en la generación de las bases de datos y archivos necesarios para el diseño.

Dado que las herramientas EDA que se utilizan corren sobre un sistema operativo Linux, muchos de los scripts que se encuentran en esta estructura hacen referencia a particularidades de este sistema operativo, que no se aclaran pues se consideran deberían ser conocimiento básico de los destinatarios de este documento.

La primera propuesta de esta estructura fue desarrollada por el Dr. Juan Agustín Rodríguez y se tomó como referencia para desarrollar la que a continuación será expuesta. La estructura que se propone se basa en tres principios muy relacionados con el mundo de desarrollo de software; sin embargo, apelan más a la experiencia práctica del Dr. Rodríguez y del aspirante que escribió este informe.

• Regularidad: este concepto se refiere a la uniformidad con la que los elementos desarrollados se ubican, dentro de la estructura de archivos y directorios, los cuales están basados en un principio o plan.

Esta estructura es "regular" en tanto presenta la misma morfología para los distintos directorios, esto quiere decir que aunque los directorios contienen archivos de distinta naturaleza, la mayoría presentan una jerarquía constante entre sí.

• Localidad: se refiere a usar archivos y directorios únicos, para evitar el manejo de múltiples versiones y múltiples rutas de acceso a archivos que en esencia son iguales, lo cual suele ser un problema cuando se debe involucrar a más personas en un proyecto.

La estructura presenta localidad en tanto los archivos fuente y las bases de datos generadas por los procesos de síntesis, únicamente residen en un único directorio y presentan sólo una ruta de acceso, no se generan copias de estos archivos en otros directorios, y la forma en que se accede a ellos es mediante punteros. Existen algunas excepciones a este principio; sin embargo, serán expuestas más adelante y se justificará el porqué de estos archivos.

• Continuidad: la continuidad hace referencia a dos conceptos; el primero es sobre la capacidad de poder usar elementos en la estructura del flujo para rastrear el diseño en una etapa dada hasta la etapa de origen que en este caso corresponde al modelo de comportamiento del diseño. El segundo se relaciona con la capacidad de ser permanente, o en otras palabras tener la capacidad de degradarse con lentitud. Es frecuente encontrar que entre diseñadores existan desacuerdos sobre la mejor forma de nombrar los archivos o la mejor manera de ubicarlos y realmente no es posible definir una estructura como la más eficiente o la estructura suprema, pues apela a muchos criterios subjetivos y relativos, tanto por parte de los diseñadores como por la naturaleza de los proyectos.

Finalmente se afirma que la estructura es continua, ya que la navegación dentro de los directorios permite identificar de forma fácil e intuitiva, cada etapa del flujo. Mediante los scripts, y un conocimiento general del flujo descrito en 2.2.1, puede ubicarse cualquier resultado, y rastrear los archivos fuente que los generaron (los resultados). Respecto a la parte de continuidad en el tiempo, se espera ofrecer una estructura lo suficientemente elegante y práctica para que pueda seguir siendo utilizada en futuros proyectos y que los diseñadores que los enfrenten puedan sentirse cómodos con ella.

# 3.1 Estructura de directorios y archivos

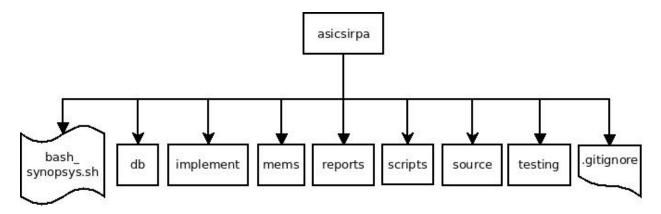

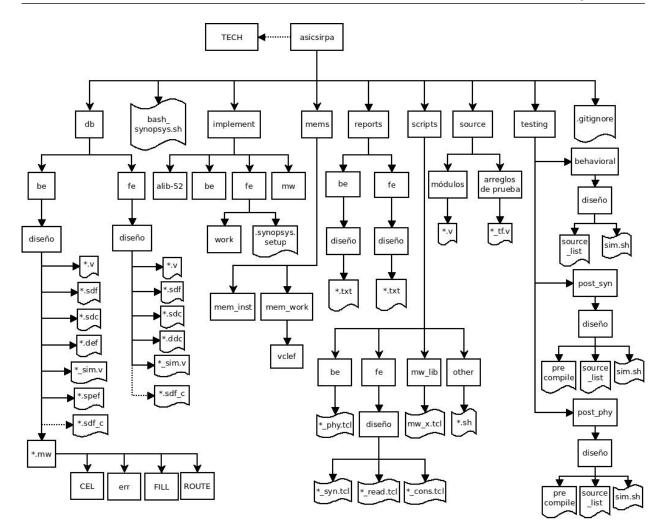

Como puede apreciarse en la figura 3.2, el directorio base del proyecto contiene hasta el momento siete directorios y dos archivos, uno de los cuales es oculto y carece de relevancia para el proyecto. Comenzando por el archivo **bash\_synopsys.sh**, tenemos un script del intérprete de comandos **bash**, que es una de las tantas consolas que ofrecen los ambientes Linux. Este script contiene punteros hacia los archivos ejecutables del juego de herramientas de Synopsys, la licencia para que puedan correr, y finalmente cualquier otro software afín al proyecto pueda usarse.

Figura 3.1: Esquema de la jerarquía de directorios y archivos para implementar el flujo de diseño digital. El archivo .gitignore es un archivo oculto, que contiene información para que la herramienta de control de versiones usada en el DCILab opere de forma personalizada. Este archivo carece de relevancia para la estructura del flujo; sin embargo, permite mantener un repositorio más ordenado. Figura de autoría propia.

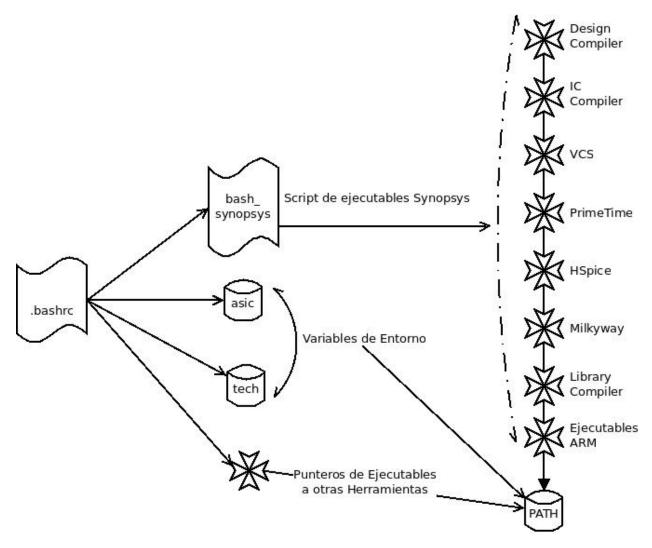

Dentro de la estructura propuesta existe un archivo importante para que los scripts y las herramientas trabajen de forma más eficiente. El archivo en cuestión es el .bashrc, que se ubica en el directorio HOME del usuario (universal en cualquier sistema linux moderno). Este archivo es ejecutado cada vez que se abre una terminal o consola de tipo bash. Le permite al usuario personalizar distintos aspectos de la consola, como:

Contar con la posibilidad de disponer de las herramientas sin tener que ejecutar el script de inicialización (bash\_synopsys.sh) cada vez que se abre una nueva terminal, invocando por defecto al script de inicialización.

Si existen copias del proyecto en más de un computador, se tendrá una ruta absoluta diferente hacia el directorio del proyecto para cada máquina. Sin embargo, una vez dentro del directorio del proyecto, las rutas hacia directorios y archivos se vuelven universales. Usar variables de entorno permite que en los scripts hayan punteros hacia el directorio principal del proyecto, esto evita la necesidad de editar los scripts, en caso de querer ejecutarlos en computadores diferentes.

En el bloque de código 3.1 podemos observar un ejemplo que ilustra la ejecución del script de bash para incluir en la variable de ambiente PATH, las rutas a los ejecutables de las herramientas EDA (línea 8), y la creación de 2 variables con la ruta relativa al directorio base del proyecto (variable "asic", línea 3) y al directorio de la biblioteca de la tecnología (variable "TECH", línea 5).

Figura 3.2: Esquema completo de la jerarquía de directorios y archivos que implementan el flujo de diseño digital. El bloque TECH hace referencia a la biblioteca de la tecnología. No es una buena idea agregar este directorio en la misma ubicación que el proyecto ya que es un directorio de tamaño considerable y copiarlo en cada proyecto representa un mal uso de los recursos. Figura de autoría propia.

**Listado 3.1:** Directivas para crear las variables de entorno utilizadas por los scripts de las herramientas e invocar el scritp de las herramientas de Synopsys.

```

# Home for working on the SiRPA ASIC Integration Project

1

2

asic=/home/rcastro/asicsirpa

export asic

3

# IBM technology files for the Integration Project (Library)

4

tech=/home/IBM/TECH

5

6

export tech

7

# Load the EDA Synopsys executables

. $asic/bash_synopsys.sh

8

# Load a text processor application

9

PATH=$PATH:/home/tools/sublime_text_3

10

export PATH

11

```

**Figura 3.3:** Esquema ilustrativo de la relación entre los scripts de bash que inicializan las herramientas EDA y crean las varibles que contienen los punteros a los archivos y la biblioteca de la tecnología de integración. Figura de autoría propia.

Retomando el diagrama de la figura 3.2, dentro del directorio del proyecto de integración encontramos siete directorios, de los cuales db, implement, reports y scripts presentan la misma estructura regular, pues en cada uno de estos directorios encontramos otros 2 directorios llamados be y fe (que como podrá intuirse hacen referencia a back end y front end respectivamente). Se decidió usar estas abreviaciones por su simplicidad, pues resumen muy concretamente a qué hacen referencia y son muy intuitivas.