Instituto Tecnológico de Costa Rica Escuela de Ingeniería Electrónica

### Development of a multi-core and multi-accelerator platform for approximate computing

para optar por el título de Ingenierio en Electrónica

con el grado académico de Licenciatura

Pablo Felipe Osorio Marín

30 de noviembre de 2017

Instituto Tecnológico de Costa Rica Escuela de Ingeniería Electrónica Proyecto de Graduación Tribunal Evaluador

Proyecto de Graduación defendido ante el presente Tribunal Evaluador como requisito para optar por el título de Ingeniero en Electrónica con el grado académico de Licenciatura, del Instituto Tecnológico de Costa Rica.

Miembros del Tribunal

M.Sc. Luis Paulino Méndez Badilla Profesor Lector

M.Sc. Miguel Ángel Hernández Rivera Profesor Lector

M.Sc. Jorge Castro-Godínez Profesor Asesor

Los miembros de este Tribunal dan fe de que el presente trabajo de graduación ha sido aprobado y cumple con las normas establecidas por la Escuela de Ingeniería Electrónica.

Declaro que el presente documento de tesis ha sido realizado enteramente por mi persona, utilizando y aplicando literatura referente al tema e introduciendo conocimientos y resultados experimentales propios.

En los casos en que he utilizado bibliografía he procedido a indicar las fuentes mediante las respectivas citas bibliográficas. En consecuencia, asumo la responsabilidad total por el trabajo de tesis realizado y por el contenido del presente documento.

Pablo Felipe Osorio Marín Cartago, 30 de noviembre de 2017 Céd.: 8 0111 0971

This work is licensed under a Creative Commons "Attribution-NonCommercial-ShareAlike 4.0 International" license.

to my dear family and friends

# Acknowledgments

The result of this work and all the tough days of work, could not be possible without the constant support of many people. Many thanks to my adviser, Jorge Castro Godínez, through all the confusion and speculations every time I found guidance, advice and work to keep on going. Without him this opportunity could not have materialized for which am forever grateful. To my parents, Luis and Gloria, my sister and friends to whom I find myself deeply grateful for everything they have done to help me achieve this goal. Who have endured all this process with me and even when it seems impossible help me be above it. I will always be growing thanks to your support.

Imagination is more important than knowledge -Albert Einstein

Pablo Felipe Osorio Marín Cartago. November 30th, 2017.

## Abstract

Changing environment in the current technologies have introduce a gap between the ever growing needs of users and the state of present designs. As high data and hard computation applications moved forward in the near future, the current trend reaches for a greater performance. Approximate computing enters this scheme to boost a system overall attributes, while working with intrinsic and error tolerable characteristics both in software and hardware. This work proposes a multicore and multi-accelerator platform design that uses both exact and approximate versions, also providing interaction with a software counterpart to ensure usage of both layouts. A set of five different approximate accelerator versions and one exact, are present for three different image processing filters, Laplace, Sobel and Gauss, along with their respective characterization in terms of Power, Area and Delay time. This will show better results for design versions 2 and 3. Later it will be seen three different interfaces designs for accelerators along with a softcore processor, Altera's NIOS II. Results gathered demonstrate a definitively improvement while using approximate accelerators in comparison with software and exact accelerator implementations. Memory accessing and filter operations times, for two different matrices sizes, present a gain of 500, 2000 and 1500 cycles measure for Laplace, Gauss and Sobel filters respectively, while contrasting software times, and a range of 28-84, 20-40 and 68-100 ticks decrease against the use of an exact accelerator.

**Keywords:** Multicore, Accelerator, Memory mapped, Interfaces, Approximate, platform, Sobel, Laplace, Gauss, Parallelism, DMA, Processor, Power, Area, Delay, Time, Performance.

## Resumen

El constante cambio en el ámbito de las nuevas tecnolog ha traído consigo una brecha entre las necesidades de los usuarios y el estado actual de los diseños. Computación aproximada entra en este esquema para mejorar las caracterísiticas de los dise tanto en software como en hardware, al utilizar las propiedades intrínsicas y tolerables a errores de cada componente. Este trabajo propone el dise una plataforma multi-núcleo y multi-acelerador que usa versiones tanto exactas como aproximadas, además de recursos por software para asegurar ambas estructuras. Se muestra un grupo de cinco versiones diferentes de aceleradores aproximados, así como una versión exacta para los filtros de procesamiento de imágenes, Laplace, Sobel y Gauss, cada uno junto con su respectiva caracterización en términos de Potencia, Área y Tiempo de retraso. En estas se observarán mejores resultados para las versiones 2 y 3. Continuamente se muestran tres diseiferentes de interfaces para la incorporaci aceleradores en conjunto con un procesador softcore, Altera NIOS II. Los resultados recopilados demuestran una mejora considerable al utilizar las versiones aproximadas en comparación con las versiones de software y acelerador exacto. Los tiempos de operación de filtrado y accesos a memoria, para dos tamae matrices diferentes, presentan una ganancia de 500, 2000 y 1500 ciclos en mediciones para los filtros Laplace, Gauss y Sobel respectivamente contrastando contra los tiempos por software, y un decremento en el rango de 28-84, 20-40 y 68-100 ciclos contra el uso de acelerador exacto.

Palabras clave: Multi-núcleo, Acelerador, Interfaces, Aproximado, Plataforma, Sobel, Laplace, Gauss, Paralelismo, DMA, Procesador, Potencia, rea, Retraso, Tiempo, Rendimiento.

# Contents

| List of Figures iii |                                                                                                         |    |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

| Li                  | List of Tables v                                                                                        |    |  |  |  |  |  |

| Al                  | Abbreviations                                                                                           |    |  |  |  |  |  |

| 1                   | Introduction                                                                                            | 1  |  |  |  |  |  |

|                     | 1.1 Approximate Computing                                                                               | 4  |  |  |  |  |  |

|                     | 1.2 Contribution                                                                                        | 6  |  |  |  |  |  |

| <b>2</b>            | Background and Related Work                                                                             | 9  |  |  |  |  |  |

|                     | 2.1 Background                                                                                          | 9  |  |  |  |  |  |

|                     | 2.2 Related Work                                                                                        | 12 |  |  |  |  |  |

| 3                   | Characterization of approximate accelerators                                                            | 17 |  |  |  |  |  |

|                     | 3.1 Image processing filters                                                                            | 18 |  |  |  |  |  |

|                     | 3.1.1 Laplace $\ldots$ | 18 |  |  |  |  |  |

|                     | 3.1.2 Gauss $\ldots$   | 19 |  |  |  |  |  |

|                     | 3.1.3 Sobel $\ldots$                                                                                    | 20 |  |  |  |  |  |

|                     | 3.2 Experimental Setup                                                                                  | 22 |  |  |  |  |  |

|                     | 3.3 Characterization Results                                                                            | 24 |  |  |  |  |  |

| <b>4</b>            | Interfacing accelerators and a softcore processors                                                      | 29 |  |  |  |  |  |

|                     | 4.1 Proposed Designs                                                                                    | 31 |  |  |  |  |  |

|                     | 4.1.1 Avalon Slave Interface                                                                            | 32 |  |  |  |  |  |

|                     | 4.1.2 Custom Avalon Master-Slave interface                                                              | 35 |  |  |  |  |  |

|                     | 4.1.3 DMA Interface                                                                                     | 38 |  |  |  |  |  |

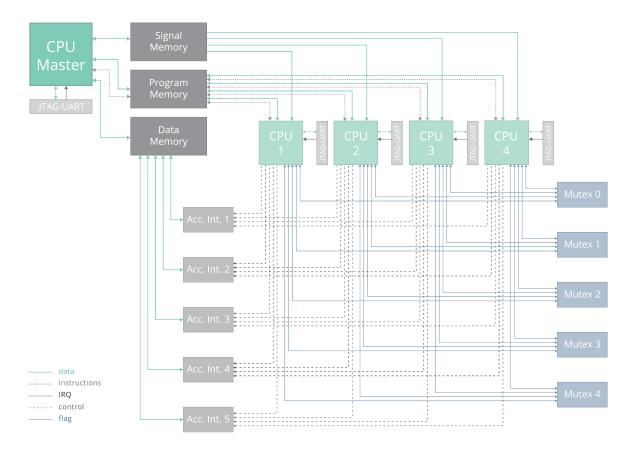

| <b>5</b>            | A Multicore and Multi-Accelerator Platform                                                              | 45 |  |  |  |  |  |

|                     | 5.1 Multi-Core Design                                                                                   | 45 |  |  |  |  |  |

|                     | 5.2 Proposed Design                                                                                     | 47 |  |  |  |  |  |

| 6                   | Conclusions                                                                                             | 53 |  |  |  |  |  |

|                     | 6.1 Future work                                                                                         | 54 |  |  |  |  |  |

| Bibliography        |                                                                                                         |    |  |  |  |  |  |

# **List of Figures**

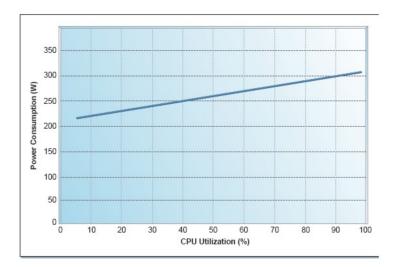

| 1.1  | Power Consumption vs CPU Utilization (taken from [17])         | 2  |

|------|----------------------------------------------------------------|----|

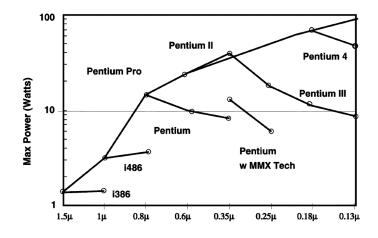

| 1.2  | Power Dissipation for several microprocessors (taken from [7]) | 3  |

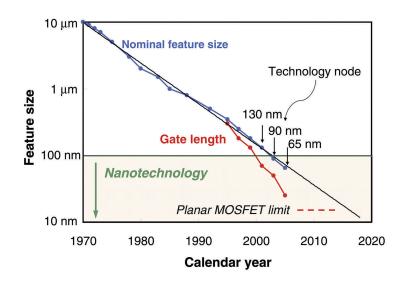

| 1.3  | Moore's Law (taken from $[35]$ )                               | 3  |

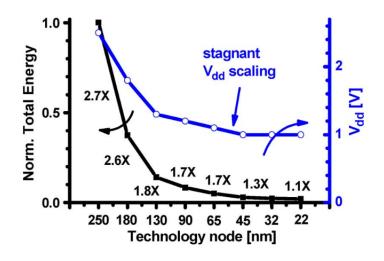

| 1.4  | Utilization wall (taken from [27]).                            | 4  |

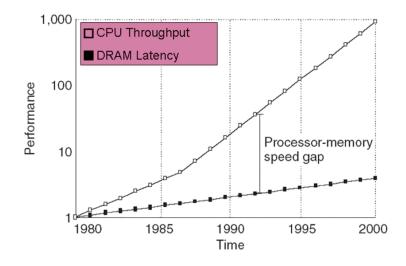

| 1.5  | Memory Wall (taken from [24])                                  | 5  |

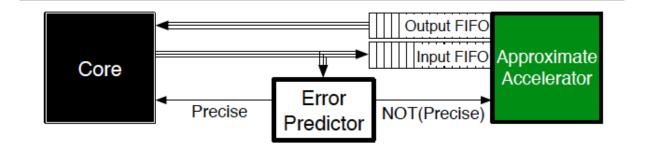

| 1.6  | Approximate Architecture with Quality Control (taken from [8]) | 6  |

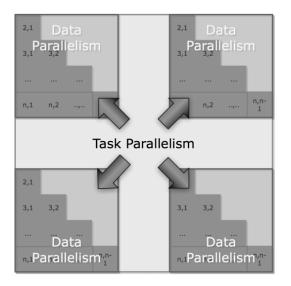

| 2.1  | Task parallelism (taken from [26]).                            | 10 |

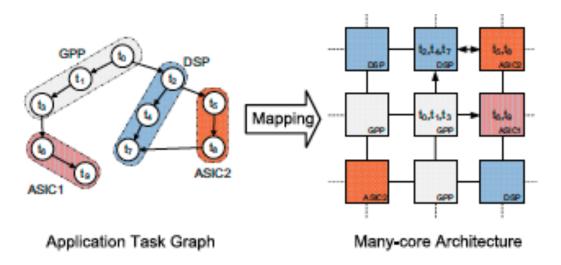

| 2.2  | Application Mapping (taken from [4]).                          | 12 |

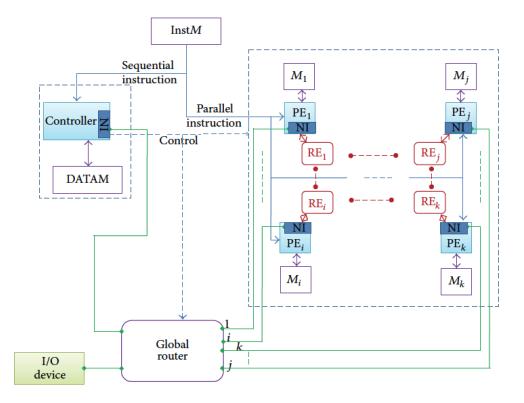

| 2.3  | Multicore design (taken from [21]).                            | 13 |

| 2.4  | SNNAP System Diagram (taken from [33])                         | 15 |

| 2.5  | Methodology Flow (taken from [22])                             | 16 |

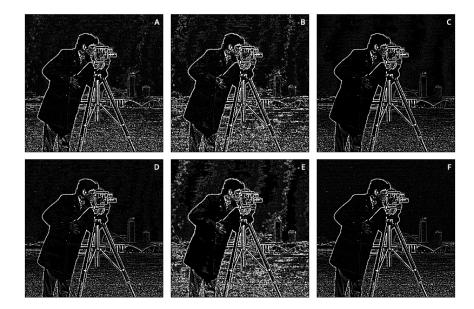

| 3.1  | Cameraman test image                                           | 17 |

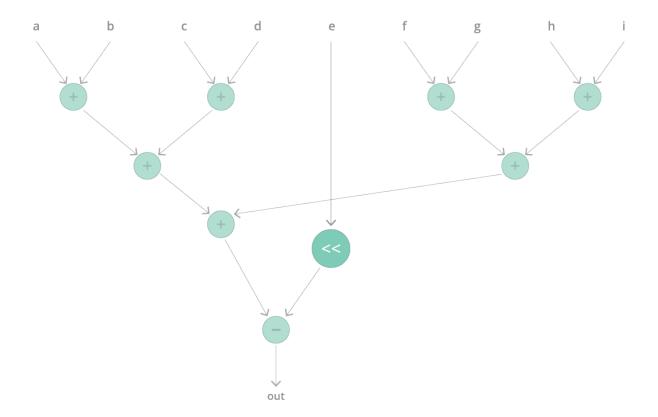

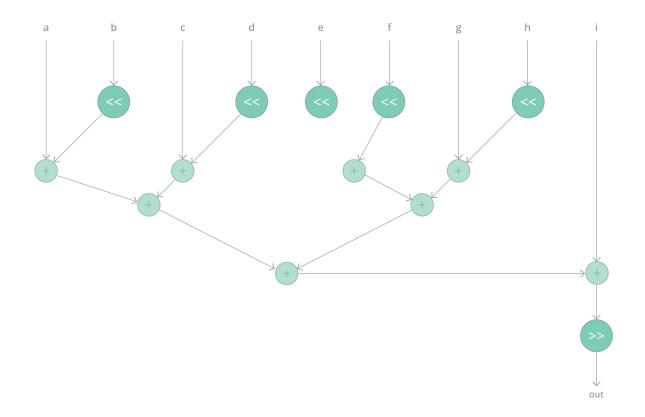

| 3.2  | Laplace filter data flow graph                                 | 18 |

| 3.3  | Gauss 3x3 filter data flow graph.                              | 20 |

| 3.4  | Sobel filter data flow graph                                   | 21 |

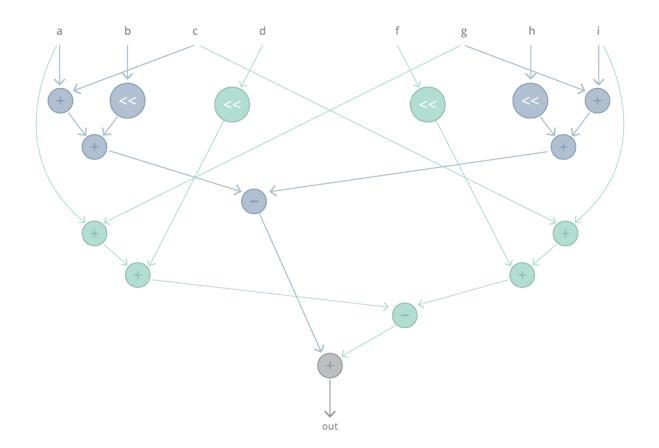

| 3.5  | Methodology diagram for accelerators characterization          | 22 |

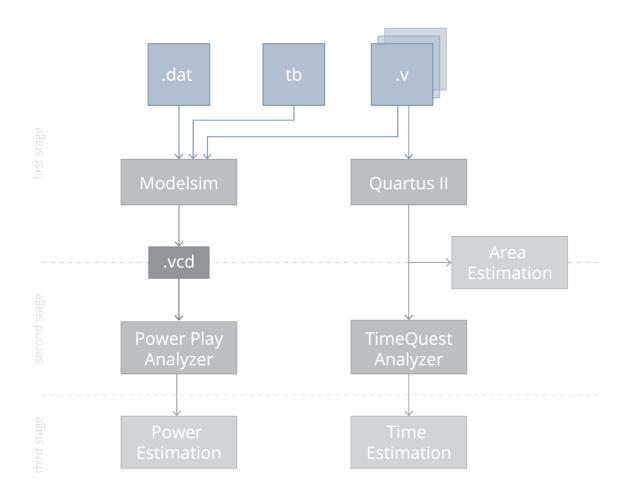

| 3.6  | Laplace 8 Filter Versions Outputs                              | 25 |

| 3.7  | Gauss Filter Versions Outputs                                  | 26 |

| 3.8  | Sobel Filter Versions Outputs                                  | 28 |

| 4.1  | Avalon Memory Mapped Interface Transfers (taken from [1])      | 30 |

| 4.2  | NIOS Program Code Memory Map. Retrieved from [2]               | 32 |

| 4.3  | Avalon Slave Interface for Accelerators                        | 33 |

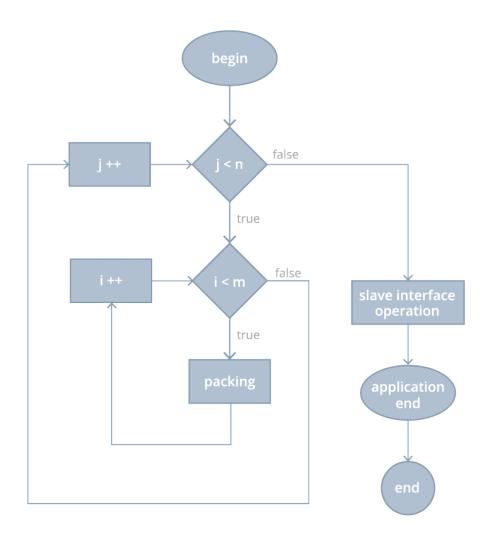

| 4.4  | Flow Diagram Avalon Slave Interface                            | 34 |

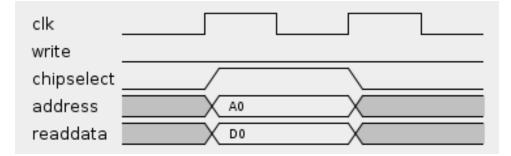

| 4.5  | Read Timing Diagram for the Slave Interface                    | 35 |

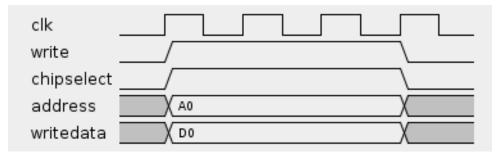

| 4.6  | Write Timing Diagram for the Slave Interface                   | 35 |

| 4.7  | Avalon Master-Slave Interface for Accelerators                 | 36 |

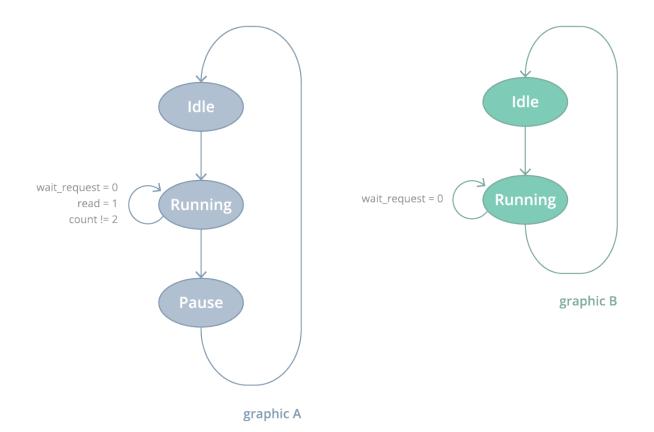

| 4.8  | Finite State Diagrams                                          | 37 |

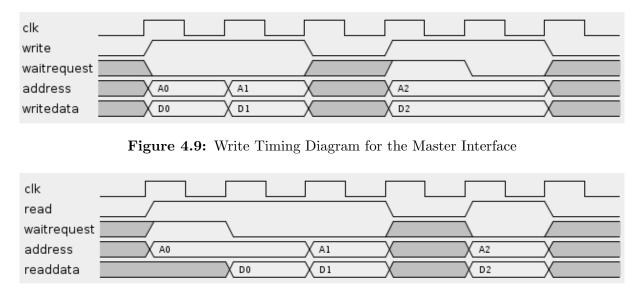

| 4.9  | Write Timing Diagram for the Master Interface                  | 38 |

| 4.10 | Read Timing Diagram for the Master Interface                   | 38 |

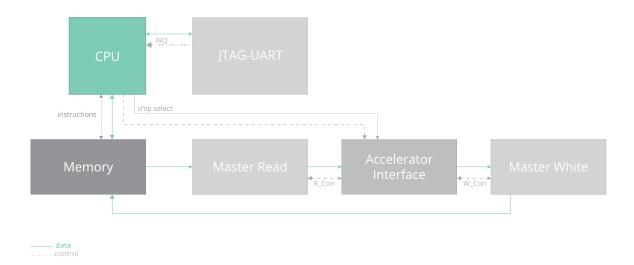

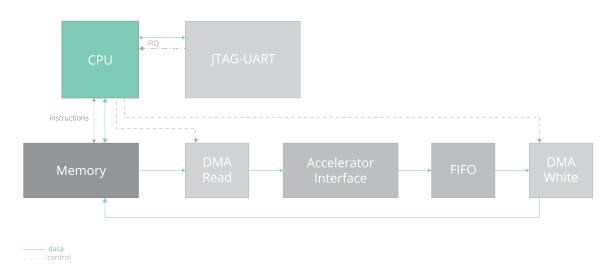

| 4.11 | DMA Interface for Accelerators                                 | 39 |

| 4.12 | Flow Diagram DMA Inerface                                      | 40 |

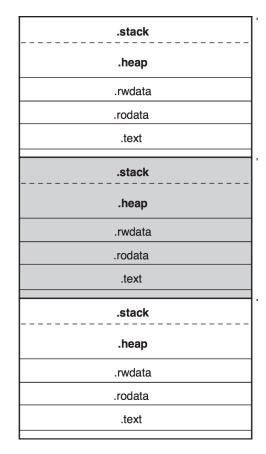

| 5.1 | Multicore Memory Partition. (taken from [2]) | 46 |

|-----|----------------------------------------------|----|

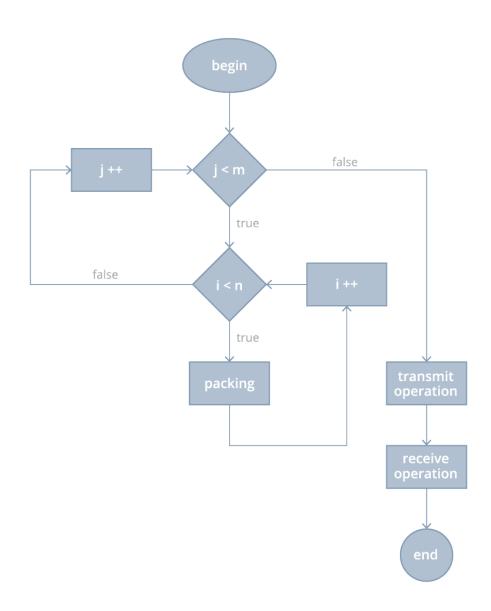

| 5.2 | Proposed Multicore Design                    | 48 |

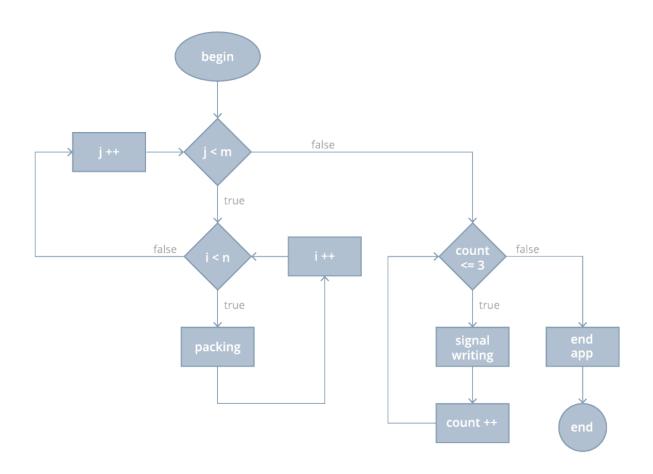

| 5.3 | Flow Diagrama Master Application             | 49 |

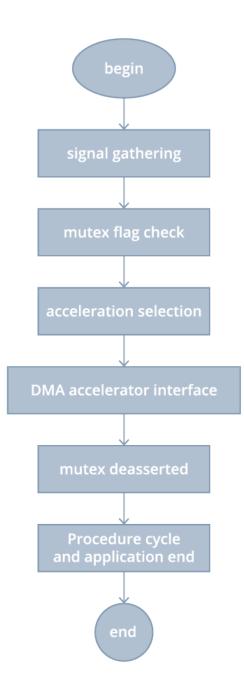

| 5.4 | Flow Diagrama Slave Application              | 51 |

# **List of Tables**

| 3.1 | Quality characteristics of Laplace approximate accelerators  | 24 |

|-----|--------------------------------------------------------------|----|

| 3.2 | Laplace Accelerators Characterization                        | 25 |

| 3.3 | Quality characteristics of Gaussian approximate accelerators | 26 |

| 3.4 | Gaussian Accelerators Characterization                       | 27 |

| 3.5 | Quality characteristics of Sobel approximate accelerators    | 27 |

| 3.6 | Sobel Accelerators Characterization                          | 28 |

| 4.1 | Performance Time Filters Software Versions                   | 42 |

| 4.2 | Performance Time Laplace 8 Accelerators                      | 42 |

| 4.3 | Performance Time Gauss 3x3 Accelerators                      | 43 |

| 4.4 | Performance Time Sobel Accelerators                          | 43 |

# **Abbreviations**

| BSP  | Binary Space Partitioning          |

|------|------------------------------------|

| CPU  | Central Processing Unit            |

| DMA  | Direct Memory Access               |

| DRAM | Dynamic Random Access Memory       |

| DSP  | Digital Signal Processing          |

| EBL  | Embedded Logic Blocks              |

| ER   | Error Rate                         |

| FIFO | First In First Out                 |

| FPGA | Field Programmable Gate Array      |

| FSM  | Finite State Machine               |

| GPP  | General Purpose Processor          |

| GPU  | Graphical Processing Unit          |

| HAL  | Hardware Abstraction Layer         |

| HDL  | Hardware Description Language      |

| IDE  | Mean Error Distance                |

| IP   | Intellectual Property              |

| MED  | Integrated Development Environment |

| PSNR | Peak Signal to Noise Ratio         |

| SD   | Secure Digital                     |

| SoC  | System on Chip                     |

| SRAM | Static Random Access Memory        |

| SSIM | Structural Similarity Method       |

# Chapter 1

### Introduction

With the coming forth of newer applications, such as neural network, computer vision, machine learning, and data mining, it has become clear that characteristics of current technology no longer meet the performance requirements. There is an increasing demand of resources and efficiency for more complex applications and designs. It has been estimated that, on average, 4000 GB of data per day would be necessary for autonomous driving vehicles [23]. With the ongoing integration of Artificial Intelligence (AI) to end-user devices, and the continuous research on deep and machine learning, the need for better, faster, and efficient computing systems is on the rise.

Most of the problems with actual resources are not recent nor specific to a single cause. But even so, there are several factors that had cause this gap and will potentially generate a bigger treat. One of the problems resides in how to manage such complicated computations without disregarding execution time, power, or energy. For instance, by 2008 a single server based on Intel x86 processor, and used for data center operation, was estimated to consume 250 W on average, which turned to 23 billion W in a year for a single server farm operation [17]. In terms of the power bill, costs to maintain these facilities, and the fact that for the years to come *data is the new oil* [9], the growth is expected to be exponentially bigger with each year. As depicted in Figure 1.1, the power consumption of any server depends on its maximum utilization. The question now resides in how can it be possible to reduce the power consumption without reducing the processed data or incrementing the number of computing nodes.

Even as the power consumption problem arises, it is not the only characteristic to take in account when looking into current computing systems. Just as this is part of one of many constrains, other factors can come in the way for a complete integration or a desired development. As central processing units (CPUs) are the center component of every computation, the depth now resides in its optimization and structure.

Moore's Law has rules the design of CPUs for more than 50 years. This empirical law states that every two years the numbers of transistors in an integrated circuit will double. Many complex algorithms, dense data applications, and graphics processing, begun to

rely deeply in the advancement of new and more powerful generation of processors. As presented in 1.3, the feature size has decreased over the years, reaching the sub-micron era (less than 100nm) around 2005. Recently, Intel has achieved 10nm technology [19], which has pointed out that Moore's law might not continue to fulfill the expectations for further application. As Intel continues to be one of the biggest chip manufacturer around the world, it only creates a bigger gap between what it is expected from manufacturers and the actual needs of the present applications. The International Technology Roadmap for Semiconductors (ITRS) expectations report that it will only be viable to keep shrinking transistors until 2021-2025 [5], which also leads to the need of rethinking the present solutions to compensate future lacks and flaws that could be met. As the number of transistors per area for a specific processor grows, it allows to develop faster and more complex system, it represents a cost in terms of power and energy consumption, as it can be seen in Figure 1.2. So, newer design trends are needed to overcome these design challenges.

But the problem with Moore's law doesn't end there as the need for a continuous integration of transistors persists. According to Dennard classic scaling theory, each transistor count scales by a factor of  $S^2$ , where S is the scaling factor between two technology processes, while the switching frequency is scaled by a factor of S. The capacitance and the threshold voltage are scaled by a factor of 1/S and  $1/S^2$ , respectively. As feature size has decreased, this conception does not hold accordingly anymore. Reaching the barrier of 90nm, the characteristics foreseen by the Post-Dennard regime, or leakage-limited, changed drastically, as depicted in Figure 1.4. Under this scheme, the threshold voltage can not be further reduced without expecting an increase in leakage, rising the power density per chip, and thus limiting the utilization of the available silicon. This problem is now referred as the *utilization wall*. Due to this, portions of chip's silicon stay under-clocked at operation for full frequency or just are not used full time, making that sections of the chip remain *dark* (this concept is referred as *dark silicon* in the literature). This leads to an underutilization of resources, but it also opens the possibility to utilize portions of

Figure 1.1: Power Consumption vs CPU Utilization (taken from [17]).

the chip to enhance energy efficiency that could then free up power budget, establishing a cycle that would allow more computations but with a small power cost.

There is still another more concerning challenge that single- and multi-core processors had not been able to counter, which is the difference of speed between microprocessors and memory. This problem is the so called *memory wall*. As the improvement rate in a single processor grow exponentially with each new design, the memory technology also experiences an exponential grow but at a much slower pace. As stated [37], on average, each 5th instruction on a program requires a memory access, which then leads to be almost 40% of the whole operation. This problem it is not an easy one since, on theory, DRAM (Dynamic Random Access Memory) speeds increases 7% per year, while processor trend is to augment by 80%. The growing gap between CPU and DRAM over the time is presented in Figure 1.5. Due to the cache characteristics, the associated cache misses cause that an overall continuous increase would end up degrading the general performance over time. Even for newer and more complex systems this challenge still remains as one

Figure 1.2: Power Dissipation for several microprocessors (taken from [7]).

Figure 1.3: Moore's Law (taken from [35]).

of the most concerning factor when looking for different design opportunities to overcome this gap, and then reduce the averages cost of cycles in full functional operation [37].

As these problems seem to envelop the computational world, there have been several answers to each of them from different perspectives and studies. The firsts grasps at fighting these, came from the exploration of multi-core processors. This technology allows the users to still rely on the capabilities of a given chip or system by doing more task in parallel and thus enhancing the overall performance. Multicore has presented more energy efficiency in comparison to older single-core technologies allowing its integration in a diverse set of applications. As this technology is now in servers, laptops, mobile devices, and so on, it was thought to be the solution to the problems regarding Moore's law. But it also presents a worst problem for dark silicon, since the multi-core processing does not break the utilization wall, as the area is not scaled, the amount of chips that can be filled with more cores running at full frequency tends to decrease. The reality is that these cores still remain dark in most of their use [32], and in a multi-core architecture there's none real complete use of their whole resources. Even as these platforms are not the perfect solution, they present themselves as the most viable option for the near future [12] [11].

#### 1.1 Approximate Computing

The diverse layout of problems surrounding the processors industry today has begun a quest for other design paradigms in order to tackled every part of this spectrum. Newer research trends help, but not overcome, every aspect of it. Current technologies are making efforts to instead of disregarding misses or bad logic as useless, to look them as a potential solution for generating a far better performance in total. In words of Tom

Figure 1.4: Utilization wall (taken from [27]).

Simonite, *a bad chip at math* can help develop the technology for the future to come [30]. All of these because of **Approximate Computing**.

Approximate Computing is a design paradigm that aims to exploit the error-tolerance in a wide set of applications by performing inexact computations that allow reductions in the required computing resources, and it can be noticeable in lower power, area, and execution time [36]. As several applications turns to the realm of estimation and probability, such as speech recognition, neural networks, mining, image processing, data analytics, and so on, approximate computing has a wide range of opportunities for its use and implementations taking a leverage in the intrinsic characteristics of these processes [20]. There had been several proposals to apply this concept to software, circuits and architectures.

The abilities in software to explore productive algorithms, while using the probabilistic opportunities has brought a clearer way to synthesize whole systems and elaborate new models on the run that facilitates their approximation. But this is not only one tool, a far better one resides in the coming of approximated compilers that enables to transform complete programs in order to enhance its performance and energy consumption, while allowing tolerable errors. The software techniques vary from a range of possibilities, beginning with error injection to specific parts in code moving forward to annotating approximable programs portions. Approximation has several usages and usable techniques in this area, such as loop perforation, where skipping several iterations can reduce overhead. This area has vast applications as signal and image processing, machine learning, data research, scientific computing and much more, all of this represent the future frontiers to be break by approximate computing, where not only the main possibilities reside but the applications characteristics tend to prefer an approximate usage [20].

The advancements made by approximate computing do not end with software. Considering hardware, this design paradigm has proven to be reliable for recent architectures

Figure 1.5: Memory Wall (taken from [24]).

covering two main areas regarding tolerable parts of software running on the processor and the translation from code to accelerators. This recent development also favors the incorporation of simpler units or processes, such as arithmetic circuits and synthesis techniques during hardware design, exploiting as well the intrinsic features of already codes that works with estimates and probabilities, as is the case of neural accelerators. These adders, multipliers, and automated approximate implementations, tend to present upgrades in power-efficiency characteristics by exploiting the control accuracy integrated in them [25]. Also in presence of intrinsic errors several hardware units can be useful for exploiting its approximate capabilities, such is the case with memory access skipping, voltage scaling, and refresh rate reduction, just to mention a few. In Figure 1.6 can be observed the conception of an approximate accelerator altogether with an error predictor unit and a host processor; this architecture presents the basis for an approximate approach capable of replacing regions of code for a hardware implementation, speeding up an application and predicting the errors that need to be corrected, when outside the tolerable range. This is just an example of the work done in this area and how can be integrated to real life end user process. By doing these the search for a far better and more effective technology, could have met its most palpable solution.

#### 1.2 Contribution

This work aims to propose a multi-core and multi-accelerator platform for approximate computing. First, the design of approximate accelerators for 3 image processing kernels (Laplace, Gaussian, and Sobel), altogether with their characteristics in terms of error, delay, power, and area, are presented. For each kernel, five different designs are proposed using low-power and high-performance approximate adders, producing different accelerator versions for the same application. Centering around the characterization idea, on how this components will reflect on each accelerator, tests will focus on estimation tools from Altera to ease and enhance the results. Ranging from the synthesis tool, to Power-Play analysis estimator and TimeQuest Analyzer. All of this combined give an accurate behavior and initial performance estimation.

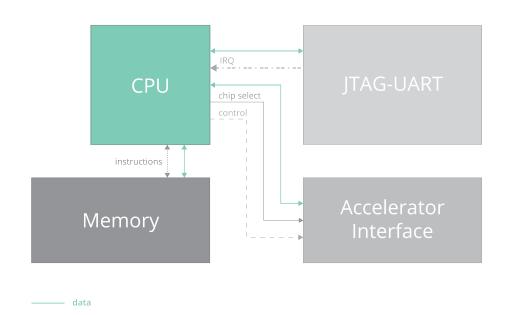

Figure 1.6: Approximate Architecture with Quality Control (taken from [8]).

Three different ways to integrate the accelerators with the softcore NIOS processor and different hardware components, from custom develop to Altera intellectual property, is presented. Each one is implemented following the bus and memory mapped protocols for slave/master interactions. The proposed designs differentiate in the protocols they need to sustain with the full system. The first shows the incorporation of a custom logic memory mapped slave who responds directly to the processor. The second has both memory mapped master and slave, to respond any read/write operations in memory sent from the processor and maintain the processing logic needed for validation. The last one has two direct memory access units (DMA) and a first in first out memory (FIFO), one for writing and the other reading, who also communicate with the processor to control the data flow.

Finally this work details a proposed multi-core platform that integrates approximate accelerators. Showing a structure capable of interact both with hardware and software, manipulating shared resources such as the accelerators, both exact and approximate, and perform adequately to the needs of master/slave interactions.

## Chapter 2

### **Background and Related Work**

### 2.1 Background

This section presents a compilation of basic notions related to image filtering, the uses of accelerators, and processor-accelerators relationship for building systems on Field Programmable Gate Array (FPGA). This reflects and establishes a practical basis in order to show a clearer picture on how these can be applied and used with the approximate computing design paradigm.

The hardware acceleration techniques are present in a diverse set of implementations, for instance, custom design circuits through hardware description language (HDL), and a variety of Graphical Processing Units (GPU) from vendors like Nvidia or ATI. The elaboration of such components have set a paradigm basis for parallelism exploitation, allowing to free resources from other parts of computing systems or relieving the amount of functions set for the main processor to do. In Figure 2.1 is possible to observe the task distribution for a single group of accelerators; this represents the basis for any design in the subject of parallelism. The integrations into commercial systems has shown to reach peak performance far better, allowing for faster development and managing a continuous research around this technology [26]. It is worth to mention that C code has maintain well establish patterns for progress around processors, but the integration of parallelism and the requirement of fine data in large amounts, tend to failed when setting an effective application. That is why, with the understanding of the desired architecture and with the flow chart around the C code software, is possible to develop Verilog- or VHDL-based accelerators capable of doing the same computations faster and with far more data.

Image processing has been a viable and reliable choice to develop hardware acceleration in recent years and it has been at the forefront of current studies in different areas in order to achieve real time performance. One example is presented in [38], where an image detection application to detect cells in a micro-well is moved to a FPGA-based accelerator implementation. By doing this, it is possible to implement faster growing systems in different researches. The current systems incorporating accelerators facilitate a way for faster tracking, less resources and detailed output, especially when dealing with large amounts of input data.

As real time applications continue to develop faster than ever, the processing envelop within the diverse group of sensors and data acquiring systems grow even larger. Problems now reside in the level of autonomy that newer designs require, in order to sustain a confident task building and routines management. The mixture of general purpose processors and hardware accelerators integrated in a FPGA, become a resilient option for embedded systems focusing in the organizations of resources and functions. In order to achieve a greater speedup for the case of image processing, due to the larger amounts of data needed, a hardware implementation should be used [31]. Since software can not sustain the intensive parallelism and information required for fulfilling this larger modes of acquisition. By doing this kind of implementation more sensitive and high resolution data can be obtained, facilitating far better solutions and improve the end user necessities.

Works regarding parallelization and customization has been presented several times. Most recent ones face challenges in the area of optimization while incorporating techniques such as scheduling, synthesis and virtualization. The structures presenting multicore solutions by itself does not solve the area and power problems common to the technical world in the past years. Networks of systems utilizing direct memory access (DMA) and series of scratchpad memory (SPM) with engines of accelerator has come to show improvement in comparison to commercial available processors. One of these designs, with a group of 24 accelerators, shows seven times more speed up and 20 percent increase in energy savings

Figure 2.1: Task parallelism (taken from [26]).

in comparison to the 12 core 1.9GHz Intel Xeon processor [15]. These results present the effective performance of a group of monolithic accelerators, which tend to offer greater advantages in performance, programming and computational costs; improving lastly the different workloads whole systems can achieve in different platforms.

Not only recent systems should involve multi-accelerators techniques and scheduling, but also look at the need for incorporating these with multi-core and efficient mapping methodologies. Optimizing power consumption and resource usage and power has reached levels for which a single core at higher frequencies can not meet the specific requirements. The exploiting of parallelism and efficient low frequency multi-processor have shown a well distribution increasing performance and advancements. In order to achieve an adequate multi-core performance, first any given application needs to be separated into tasks to be executed in conjunction for each different core. This way it assures that the necessary memory hierarchy, synchronization and communication within the system are given to all assignments. Enhancement in mapping and management distribution, has presented the advantages of designing larger scale architectures with any number of cores needed. If the mapping requirements aren't met, the fully capabilities of any multi core design wouldn't be achieved [4]. In Figure 2.2 it is shown the mapping of a whole program using a graph to form tasks in different cores. By managing these processes one can incorporate any given set of instructions into an embedded platform with far greater overall characteristics, fulfilling this way the aim for user optimizations in the current system demands.

The specifics for an adaptive hardware acceleration algorithms resides in the characteristics of each algorithm in study. A propose methodology involve de PARO design flow [14], in which the compiler receives programs descriptions such as mapping, partitioning and localization. In this way it is possible to get the representation of the parallel architecture associated to it, which ensures the maximum data reuse for each combination of accelerator and processor array, while maintaining the resource constrains and optimizing the placement of logic components and the sequentially scheduling iterations. After this results are given, the PARO flow continues with the translation into hardware description language, enabling a road to the most efficient possible architecture and participating in hand tune if necessary. Such appliances are present and constantly selective in digital filtering, image analysis and neural network. For such designs it been proved, that incorporating this designs in a FPGA presents a more reliable way to use the available resources and present the optimal design.

As more architecture incorporate the potential of machines composing multi-core and multi-accelerator platforms, the risk reside in maintaining an appropriate communication system between the application running on the core and specific region of offload on accelerators [6]. In order to overcome this, its necessary to rely on the ability to dynamically schedule task over a full set of processing units. Several proposes overcome this barriers by introducing virtual shared memory, high level distribution or register mapping communication. StarPu, the first type of these, demonstrates a high-level programming that with help from automate prediction data transfers in the prefetching state, is able to minimize the cost of each communication in the multi accelerator configuration and influence the decisions in the scheduler. By using this one is able to increase the speed and performance in multi-core and multi-accelerator machines.

#### 2.2 Related Work

The increasing amount of computations needed for a full program running on a specific SoC, has brought different new types of available tools for increasing performance. There has been work done in this area, for instance, regarding an implementation of Wiener filter [10]. In this work the characteristic of a full integration with hardware acceleration or custom instructions is presented. For both cases the main focus is the capabilities of converting a C code from a image filter into hardware, following the corresponding data path. The proposed architecture considers that a receiver/sender structure for the image pixels to treat, a DMA controller and the image filter. The results gathered from it show that the design with the hardware accelerators is two orders of magnitude faster and required the least amount of logical gates. So, any design that requires a high level of processing data should consider as a first choice the development around accelerators. Taking in account that customs instructions gives more control around the circuit generated and variability, but at a much higher operational cost in terms of area and execution time.

With the large quantity of resources available, the use of softcores and FPGA presents great opportunity to develop and test different systems. By using processors such as the NIOS core, from Altera, it provides a base of studies to construct a multi-core platform and its viability for implementations it full embedded systems. A desired platform containing an adjustable size of cores is able to demonstrate that implementing image processing applications, the performance and speed tend to overcome the capabilities of a GPU. For the cases of FIR filter and matrix multiplication by 29.5% and 23.6%, respectively

Figure 2.2: Application Mapping (taken from [4]).

[21]. In Figure 2.3 is presented the design of the multicore platform. As it can bee seen, the reception from a software stage and the instruction router, first the desired application is receive and decomposed to a set of instructions to be executed. Then they will be distributed in each core so the output would then be saved in common memory. This interaction between software/hardware, as well with the incorporation of a NIOS processor, present a viable solution for programmable architectures that depend on big quantity of data. This work set a base for the optimizations needed in order for custom accelerators be implemented, and how by integrating these technologies such as approximate computing can continue increase the efficiency of such designs even more.

Research on approximate computing goes from simple blocks such as adders, multipliers and so on, in order to extend to accelerators and more complex systems, such as neural networks. These adders tend to integrate an Error Detection and Correction (EDC) unit, that enables flexibility due to requirement of the different applications. As this components becomes a decisive part in full systems for their adaptive capabilities, it is also clear the cost in area and energy. Considering this is also possible to incorporate a Consolidated Error Correction (CEC), which at a low cost enables to correct the accumulated error for any accelerator output by treating it with a specific model for approximation error, facilitating in this way a far better response in terms of area, speed and accuracy in results in comparison to modern accelerators [29]. To incorporate these type of error detection is necessary to take in account the unique requirements of each desired benchmark, so any architecture could apply it to improve its characteristics.

Figure 2.3: Multicore design (taken from [21]).

Also, exploring the possibility to declared programs, functions, and even hardware that can tolerate certain errors without compromising the overall results, while improving lastly the performance of each design, have been researched. More complex architectures are rising, involving dual voltage static random access memory (SRAM), interleave high and low voltage operations and approximate caches with registers. With the incorporation of approximate operations, the hardware achieves freedom to use less resources, sacrificing the accuracy but gaining the advantage of less energy used. In this aspect, the utilization of microarchitectures, with the capacity of managing its resources from a high voltage in exact mode to low voltage in approximate, become a big tool representing even a reduction , for several benchmarks, of at least 43% in energy saves up [13]. The data in this structure would first undergo a mapping into approximate programming for then be applied into hardware, and the different possibilities it can sustain, from operation, to registers and loads, stores and caching in memory. This newer technology presents the usage of DMA to communicate with the SRAM, with reduced refresh rate and the implementations of registers that does not guaranteed and exact value, each of this features in approximate mode. Facilitating a whole assemble that would become reliable for data processing and acquisition in both modes.

The works in hardware acceleration approximation have come to two main threads, one where it is possible to exploit traditional architectures and another one with discrete accelerators [28]. In both it is possible to achieve more current research and future works. The traditional aspects limits the efficiency gains, such example its presented above. The newer approach seeks a co-design between accelerator, software interface and compiler in order to maintain quality and reach meet the performance necessities. If the old architectures are combined with new accelerators its possible to achieve better levels of behavior.

Not all the performance for a given application resides in its structure in hardware and traditional operation. There have been several solutions in high level synthesis where its possible to use a compiler framework in order to compose approximate programs from exact ones in order to use these in neural networks, such as systolic neural network accelerator in programmable logic (SNNAP). While offloading regions in the program its possible to identify the best parts and strategies in order to incorporate sections of code with approximation for a better performance. Using an specific set of accuracy requirements its possible to observe an increment in the operation characteristics of SNAAP, while running different set of programs [33]. With the increasing support of imprecision in modern systems, its possible to use such compilers for already set program domains and show approximation in both hardware and software. Including programs in embedded sensing and machine learning can drastically impact performance without impacting the final output, facilitating a whole new form of programming and integration in complete systems.

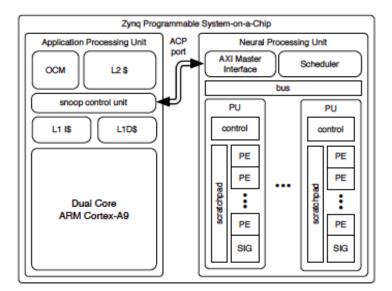

Due to its intrinsic characteristics for error tolerability, and probability background, neural networks are case of implementation subject for tests in this area. The most versatile and complete research up to now, resides in SNNAP. This type of neural acceleration was designed to be implemented on SoC's and based on a FPGA for approximate programs. The mixture between its workflow and the neural network topology and weights maintains an effective senses that enables its use in commercial devices without the need of hard reconfigurations. The approach of understanding and passing C code to gate level enables a wide range of benchmarks. Utilizing this scheme in a Zynq board, it was possible to demonstrate up to 3.8 times the speed up and 2.8 times the energy savings [34]. In Figure 2.4 the configuration of this accelerator it is shown, the dual core enables a reception an storage of the program to be accelerated, the neural processing unit its the accelerator part from which sections of the approximated code are run and the result its then send to the ARM on chip memory via the accelerator coherency port. The design incorporating such technologies demonstrates how FPGA present an advantage tool for accelerating code regions on fixed hardware and it is able to exploit neural network for hardware approximation.

As more approximate accelerators are develop, the classical way of invocation is linked to specific code sections. But by working this way, there has been an associated error to any results given. The introduction of a predictor would help to prevent large quantity of data degradation by evaluating the different cases, in these manner is possible to run both modes as needed just by taking in account the signal from the predictor. Such systems are also presented in neural network to ensure realistic reference points. If the predictor is present, such systems could achieve 2.6 times more speedup and 2.8 times energy reduction by the specification of a 5% error [8]. In neural predictors would gain at least 17% in energy. For optimizing approximate systems the requirements of architectural mechanism that assist in output control are a necessity in order to achieve a viable design.

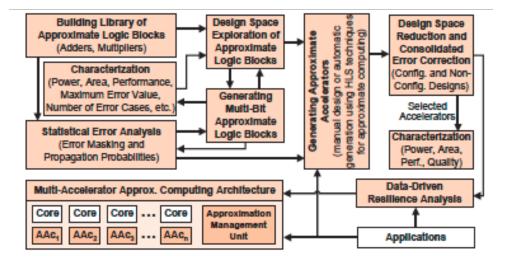

In more adaptive systems the incorporation of approximate blocks require to adaptively change in order to reduce the area and power overhead and maintain the error analysis of each design. The needs for logic that enables the change between modes of accurate

Figure 2.4: SNNAP System Diagram (taken from [33]).

and approximation, becomes clearer as the diverse use of multi accelerators in a single architecture begins to fail in flexibility and adaptivity [22]. In Figure 2.5, it is presented the custom logic for a full flow between high level synthesis generating accelerators from logic blocks, and its implementation in multi-accelerator architectures. For such, it is needed a way to analyze the continuing masking of error propagation and the change between modes, so that the result from the approximate computing are efficient and are able to propose viable solutions. The data flow that this methodology follows, is first the generation of the approximate accelerator, for this to be a viable option it is required a library of approximate logic blocks who by a given set of error analysis, in previous work, and a overall characterization, can construct the component that adapts to this criteria. After the generation, an analysis of the characterization and resilience is done, previous to the incorporation to the final computing architecture. This final architecture presents a *n* number of accelerators and its given core, both undergoing a serious of features that would finally enable the given application to run separately in each, by doing these a more efficient and efficient unit is present. The last block is the Approximation Management Unit, which its in charged of selecting the appropriate mode for each accelerator. By controlling this signals it is possible to keep the performance and quality necessary, but with the advantage of reducing the overall energy consumption. Such a tool for control needs to keep track for resilience in the data path and properties of different applications at run times in this type of architectures.

Figure 2.5: Methodology Flow (taken from [22]).

# Chapter 3

# Characterization of approximate accelerators

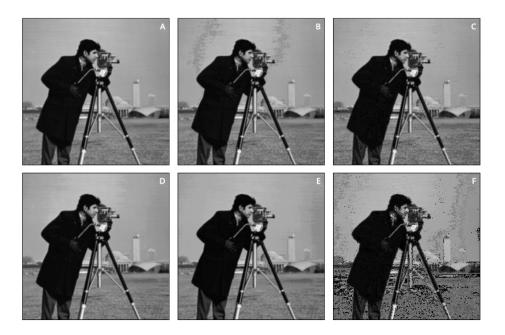

In this chapter, approximate accelerators for three image processing filters: Laplace, Sobel and Gaussian, are described. For each filter, five approximate versions are presented, varying their error metrics due to the approximate arithmetic components used. This chapter is divided in three main sections: the accelerators designs, experimental setup, and the results of the characterization in each case. In the first section a depiction of each filter is provided ranging from the operations needed, circuitry implementation an kernel specification. Later, the experimental setup is described, which contains all the information regarding the tools used for the characterization as well as the procedure followed. A flow diagram is presented, so the experimental structure is easily delineated and follow all along the text. Finally, the results from the experimentation and implementation of each filter, using test image Figure 3.1, are shown in the last section.

Figure 3.1: Cameraman test image

## 3.1 Image processing filters

This section presents three different filters used along this work. A full depiction of the operations can be seen in the following diagrams and explanations. For each filter, there is a brief kernel description, in order to understand the mathematical process behind it, and also a group of pictures are place to demonstrate the different effects of filtering on a specific image.

#### 3.1.1 Laplace

The Laplace filters are derivative filters used to find edges in images. They are represented by equation (3.1).

$$L(x,y) = \frac{\partial^2 f(x,y)}{\partial x^2} + \frac{\partial^2 f(x,y)}{\partial y^2}$$

(3.1)

There are several ways to get the discrete representation on the effect of a Laplacian model, the most common being the convolution around a central negative peak. For the scenarios studied in this work, the kernel of the Laplace filter is described as:

Figure 3.2: Laplace filter data flow graph.

$$\Delta_{xy}^2 = \begin{bmatrix} -1 & -1 & -1 \\ -1 & 8 & -1 \\ -1 & -1 & -1 \end{bmatrix}$$

As can be seen in Figure 3.2, a data flow graph representing this filter is composed of combinational logic, taking in account 7 adding operations, 1 subtraction and 1 shift left operation. In the first part of the operation, nine inputs of eight bits are taken, the e entry is associated specifically with the pixel in study and the other inputs are the surrounding matrix in order to execute the convolution. The diagram proposed is the outcome after the convolution is execute between the kernel, presented above, and the matrix associated with the desired pixel. Just as the e input undergoes a left shift of two, in order to get a multiplication by four, the other eight inputs (a, b, c, d, f, f)q, h, and i, are added between each other. Then, the result of the multiplication is subtracted from the result of all additions, to get the final output of the laplacian filter. Finally the output is constrained, so that the obtained value stays positive and does not surpass an integer value of 255. The operations described are the basics, both exact and approximate accelerators would have to complete. For each of the approximate cases, the proposed variations would concern the adders in every component, varying these with it approximate counterparts in order to understand how they would reflect in the behavior and results provided by each accelerator.

#### 3.1.2 Gauss

For the Gauss smoothing filter, or Gaussian filter, the two dimension convolution are used to blur images and remove details and noise. This filter provides a method for reducing intensity, but it diverges from other types since the kernel used for it is bell shaped. The equation (3.2) presents the form a Gaussian distribution has.

$$G(x,y) = \frac{1}{2\pi\sigma^2} \cdot e^{-\frac{x^2 + y^2}{2\sigma^2}}$$

(3.2)

It is worth mentioning that the implantation of this operator type is necessary to obtain a kernel that allows to perform convolution operations, just as for Laplace filter. The kernel in study is for Gauss filtering, usign a 3x3 dimension filter, is giving by:

$$G = \frac{1}{16} \cdot \begin{bmatrix} 1 & 2 & 1 \\ 2 & 4 & 2 \\ 1 & 2 & 1 \end{bmatrix}$$

In Figure 3.3, the data flow graph for the 3x3 Gaussian filter is depicted. In this design, the component is constructed with combinational logic, receiving at the start nine inputs, representing the matrix in study. The logic describes the result after performing the convolution, beginning by a one bit left shift, in order to apply a multiplication by 2, on

the inputs b, d, f, and h; for the e input is perform a two bit left shift, so its performed a multiplication by four. After this is complete, the logic proceeds to add the entree a with the result of the shift in input b, the same with c and the shift in d, g and the shift in h, and finally the adding of both shifts in e and f. The results are then added between each other, and with the input i. This final operation undergoes a right shift of four, so that the division by 16 is completed, obtaining the output of the accelerator. This output will then be constrained in order to maintain the values in a range between 0 and 255, by doing this is possible to limit the result and check its reliability. The same logic presented in 3.3 would be used for the different Gauss filter approximate models done, since the main change is the replacement of its adders by an inexact counterparts.

#### 3.1.3 Sobel

The Sobel filter of two dimensions performs a spatial gradient measurement on images, and is able to remark areas of high spatial repetition. The kernel is able to respond directly to vertical and horizontal operation respectively to the pixel under verification. The way it works is by taken two different kernels for each dimension, so it give different computations in every orientation. After the result is obtained, both magnitude and direction can be calculated. The procedure is basically a first order derivate and calculates the difference of pixel magnitude in a edge region. The kernels that describe the operations are as follows:

Figure 3.3: Gauss 3x3 filter data flow graph.

$$G_x = \begin{bmatrix} 1 & 0 & -1 \\ 2 & 0 & -2 \\ 1 & 0 & -1 \end{bmatrix} \quad G_y = \begin{bmatrix} 1 & 2 & 1 \\ 0 & 0 & 0 \\ -1 & -2 & -1 \end{bmatrix}$$

Taking in account the above 3x3 kernels is possible to realize the convolution between these and matrices in study, with this kernel the appropriate characterization is realized. Looking at Figure 3.4, it can noticed the operations all data undergoes for both the vertical and horizontal position. This diagram describes as well the circuitry involving the Sobel accelerator, which is composed of eight inputs (a, b, c, d, f, g, h, and i). In this case the center pixel is not taken in account, as one can extrapolate from the kernels described. The first step in the accelerator, as mark out by the road in green, is the process of the horizontal kernel. The inputs d and f are multiplied by two, while the *a-g* and *c-i* pixels are added respectively. The results from the *a-g* operation is added with the *d* multiplication, and then it is subtracted with the result of the *g-i* and *f* multiplication addition. The following step, marked by road blue, is the vertical kernel. The inputs b and h are multiplied by two, while *a-c* and *g-i* are added. The result of *a-c* operation will be added with the output of the b multiplication, and then subtracted with the *g-i* operation and *h* multiplication adding. The output of both subtractions will then be added giving the final output of the filter. This is denoted as *out* in Figure 3.4. Same as

Figure 3.4: Sobel filter data flow graph.

the other cases, the output value will then be constrained between 0 and 255.

## 3.2 Experimental Setup

Once every filter is implemented using HDL, for both exact and approximate cases, the characterization is performed. Intel FPGA (Altera) provides a programmable logic device design software called Quartus II. This suite enables analysis and synthesis of HDL designs, perform timing analysis, and power consumption estimation. The tools necessary are Power Play, TimQuest and the synthesis report. For the results section, a DE2-115 Altera board is considered as target platform. Inside the board, a Cyclone IV EP4CE115 chip is available, containing 114480 logic elements (LEs), 3 888 Embedded memory (Kbits) and three 50 MHz oscillator clock inputs.

The characterization procedure utilizing these tools is depicted in Figure 3.5. The first instances needed are the design files of each accelerator. The HDL file, describing the flow and interactions between the inputs and outputs, is the main part of this procedure.

Figure 3.5: Methodology diagram for accelerators characterization.

The design files comprise a three set basis, between the VHDL (.v) file, the test bench (.tb) and the image data (.dat). Each one of these would compromise the dynamic and structural basis for the accelerators. The hardware description file describes the logic correspondent between its inputs an outputs, making it the main component of the study flow. Next is the test bench file, which it assures the behavioral model while performing a simulation study in Modelsim or any other verification tool. Finally the last component, of the design files, would be the image data file (.dat). A matrix that composes the entirety of the image in study can be seen in Figure 3.1. Since each value in the matrix accounts for a different input value for the accelerator, it would be read continuously in the test bench while performing the verification.

In order to rely on the design files, it is first needed to set the schematic file (.bdf). Fixing a main block of study for continuous test, also facilitating the exchange of top files for different study cases in the project. Since the work envelops close to 20 different versions of accelerators, such tool favors every repetition without increasing the amount of work. Likewise allows to maintain every design under study, in a single main file and save the reports without exception.

After the necessary aspects are met, the next step begins by compiling each top module. The main reasons to undergo this stage are verification, Fit and Place route for the DE2-115 board, and evaluation of Timing Analysis. So far in the second stage, as shown in Figure 3.5, the main use of the compiler is verification and fitting. Using the specified board, one can study the area report by analyzing the consumed percentage of logical elements and embedded memory. This record would help summarize the average size each accelerator could take and the required resources (associated with the area used), and enable comparison between approximate versions. Also sharing second stage, as seen in Figure 3.5, is the Modelsim simulation. Each accelerator has to undergo a stimulus study and functional verification, to guarantee correct behavior, taking the test bench and data files as inputs. The stimulus study output, value change dump file (.vcd), is required for Power Play analysis. In it is contained all the functional data from the accelerator simulation, inputs/outputs from the accelerator and clock cycles taken.

For stage three, there are two main operations. The first one is the Power Play analysis, which receive the .vcd file in order to accurately estimate the power consumption the design would have. By doing this, it is possible to have an evaluation of what is to be expected in full operation for a specific accelerator, understanding the optimal performance requirements for a complete system. The second analysis is the timing estimation, using the TimeQuest Analyzer. This tool is capable of perform timing analysis by validating the design logic, using industry standard constraints (sdc) and report methodology. Now, for a full characterization it presents a data-sheet report, where is possible to observe all the possible delay paths and determine the critical circuit path. Through this data is possible to set the implications and quality metrics needed to implement such circuitry in a complete system.

After the above analysis is done, the metrics for both exact and approximate design are

determined. For each version of accelerator it will be presented a two low, two highs and a mixture of both, as can be seen in Table 3.1. In every version the error estimate predictor is varied. Such information would be vital in order to grasp performance metrics needed to influence development on any design. Also in Tables 3.1, 3.3 and 3.5, are presented the characteristics of a quality study done by the execution of each accelerator

### 3.3 Characterization Results

#### Laplace

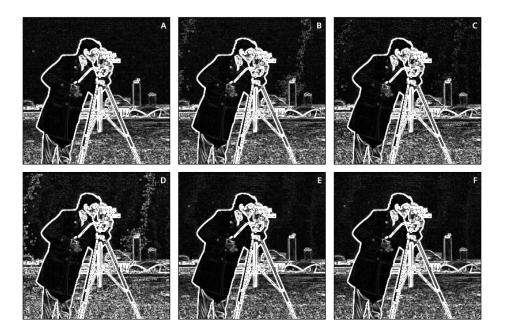

In the table 3.1, it can be seen the five different versions and there given quality output. This metrics can be observe by the parameters mean error distance (MED), error rate (ER), peak signal to noise ratio (PSNR) and the structural similarity index method (SSIM). The first two metrics are commonly used in the context of approximate computing [18] [16], while the remaining in image processing to compare quality among images. In Figure 3.6 can be seen the software outputs of each accelerator version for Laplace, listed from A to F one can appreciate the differences between each other. The effect of this filter can be seen, noting a darker image with edges accented, in both background and foreground. Image F is the exact version, while the other are approximate, comparing these with the data in Table 3.3 one can see the effect the quality characteristics has on an output image.

|           | MED   | $\mathbf{ER}$ | PSNR (dB) | SSIM |

|-----------|-------|---------------|-----------|------|

| Laplace 1 | 32.47 | 0.237         | 21.41     | 0.79 |

| Laplace 2 | 64.90 | 0.231         | 15.38     | 0.61 |

| Laplace 3 | 6.84  | 0.472         | 32.89     | 0.84 |

| Laplace 4 | 6.05  | 0.521         | 33.52     | 0.89 |

| Laplace 5 | 39.18 | 0.584         | 14.18     | 0.48 |

Table 3.1: Quality characteristics of Laplace approximate accelerators

The results obtained from the characterization of all Laplace accelerators is present in table 3.2. In this table, the three main characteristics are shown: area, delay (between inputs and outputs), and power consumption estimation. From this data one can see in terms of area measurement the exact version, noted as Laplace, have a similar area in comparison to version 1 and 5. The accelerator with less consumed blocks is version 4, while version 2 is the one taking more. In terms of time delay there are three aspects varying from minimum, average and maximum time. Each of these represent the full functioning of the accelerator. In the minimum case four of the approximate ones have higher times in comparison with the exact version. The highest and smallest versions been 5 and 4, with 10.47 and 7.88 nanoseconds (ns) respectively. The average presents more variability between each version, laying version 3 with 17.73 ns as the fastest. For

Figure 3.6: Laplace 8 Filter Versions Outputs

the maximum cases version 1, 2 and 5 are similar between one another, but faster than the exact. The least and highest times are 24.5385 and 31.331 ns, for versions 3 and 4 respectively. Finally for the power estimation only version 2 decrease, while version 1 sustains. For the other approximate versions the Power increase by a factor of ten in version 5, being the highest, and a factor of five in version 4. Both of these representing the cases with the most variability. This can lead to the expectation that version 2 can be better replacement both for power, but considering delay version 3 its an optimal option. Considering area is more difficult to choose a better option, since one must consider every characteristic and the final gain in a full system to opt for one choice.

| Accelerator | Area(ELB) | Delay (ns) |         | Power Estimation (mW) |        |

|-------------|-----------|------------|---------|-----------------------|--------|

|             |           | Minimum    | Average | Maximum               |        |

| Laplace     | 136       | 7.99       | 21.94   | 29.36                 | 156.74 |

| Laplace 1   | 136       | 8.37       | 20.41   | 28.06                 | 156.78 |

| Laplace 2   | 151       | 9.49       | 21.51   | 28.07                 | 154.37 |

| Laplace 3   | 122       | 8.37       | 17.72   | 24.54                 | 162.38 |

| Laplace 4   | 121       | 7.88       | 19.75   | 31.33                 | 161.02 |

| Laplace 5   | 136       | 10.47      | 20.59   | 28.99                 | 165.23 |

Table 3.2:

Laplace Accelerators Characterization

#### Gauss

In the Table 3.3, it is shown the quality metrics study for the Gauss filter, as is the case with the Laplace filter the MED, ER, PSNR and SSIM set the base for this study.

Figure 3.7: Gauss Filter Versions Outputs

In the table can be appreciated the five different version for the inexact accelerators. Along with this data, in Figure 3.7 can be seen the software outputs of each accelerator version for Gauss filtering, listed from A to F one can appreciate the differences between each other. The effect of this filter are seen, noting the removal noises and small quality stains around the main image parts. Image A is the exact version, while the other are approximate, comparing these with the data in Table 3.3 one can see the effect the quality characteristics has on an output image.

|            | MED  | ER    | PSNR (dB) | SSIM |

|------------|------|-------|-----------|------|

| Gaussian 1 | 8.53 | 0.210 | 33.92     | 0.93 |

| Gaussian 2 | 7.82 | 0.272 | 32.15     | 0.89 |

| Gaussian 3 | 2.31 | 0.799 | 40.49     | 0.97 |

| Gaussian 4 | 3.26 | 0.934 | 37.18     | 0.96 |

| Gaussian 5 | 5.79 | 0.725 | 28.54     | 0.83 |

Table 3.3: Quality characteristics of Gaussian approximate accelerators

The characterization for this accelerator can be seen in Table 3.4. From which Gauss represents the exact version, all the observations from this data would be done in comparison regarding it. In terms of area, only versions 1, 2, and 6 increase, while versions 3 and 4 decrease between 30-40 units. For the delay in the minimum case the most notable variant is given by version 3 with a change of almost 1 ns. In the average subject are present more changes between the obtained data, almost all tend to increase with the exception of version 4 which decrease. The most notable case been version 5 with an increment near to 5 ns. The last column present the data gathered from the Power Estimations Analysis,

in which can notably see increment in versions 1 and 2, however in comparison among one another the difference is almost ineffective. One can extract also a decrement for versions 3 and 5. Taking in account power results version 5 give the higher benefits. But in terms of delay, version 4 surpass all other characteristics, same as with the consumed logic blocks.

| Accelerator | Area(ELB) | Delay (ns) |         | Power Estimation (mW) |        |

|-------------|-----------|------------|---------|-----------------------|--------|

|             |           | Minimum    | Average | Maximum               |        |

| Gaussian    | 120       | 7.92       | 16.42   | 32.08                 | 157.06 |

| Gaussian 1  | 127       | 7.71       | 17.29   | 23.87                 | 161.11 |

| Gaussian 2  | 134       | 7.91       | 16.27   | 22.15                 | 161.15 |

| Gaussian 3  | 98        | 8.59       | 19.71   | 25.99                 | 153.62 |

| Gaussian 4  | 82        | 7.89       | 15.07   | 21.42                 | 158.15 |

| Gaussian 5  | 126       | 7.49       | 21.61   | 31.62                 | 153.03 |

Table 3.4: Gaussian Accelerators Characterization

#### Sobel

Table 3.5, shows the quality metrics study for the Sobel filter, as is the case with the Gauss and Laplace filters the MED, ER, PSNR and SSIM are used. Along with this data, in Figure 3.8 can be seen the software outputs of each accelerator version, listed from A to F one can appreciate the differences between each other. Noticing the effect of Sobel filter where image boundaries are highlighted. Image A is the exact version, while the other are approximate, comparing these with the data in Table 3.3 one can see the effect the quality characteristics has on an output image.

Table 3.5: Quality characteristics of Sobel approximate accelerators

|         | MED   | ER    | PSNR (dB) | SSIM |

|---------|-------|-------|-----------|------|

| Sobel 1 | 61.86 | 0.052 | 24.36     | 0.90 |

| Sobel 2 | 11.77 | 0.737 | 21.59     | 0.77 |

| Sobel 3 | 41.13 | 0.336 | 17.42     | 0.68 |

| Sobel 4 | 6.00  | 0.718 | 31.80     | 0.91 |

| Sobel 5 | 6.44  | 0.811 | 30.88     | 0.88 |

Further more during the study of Sobel filter accelerator and each of the different versions, is possible to procure several characteristics from them, each of these are show in Table 3.6. From this table, one can see that in terms of area versions 1 and 3 present an increment, while the others decrease, versions 5 been the lowest. For minimum delay about every versions maintains the same time, with the exception of version 1 which shows a small decrease. In average delay versions 1 and 4 stays near to the exact one, while version 5 increases and version 2 gives a slight trim. Maximum delay gives the more variability,

Figure 3.8: Sobel Filter Versions Outputs

showing higher and smaller times for version 1 and 5 respectively. Version 2 and 3 offer a narrow change between one another. Slight difference is demonstrated in versions 2, 3 and 4, in comparison with the exact one. From the power estimation, version 5 indicates the least consume. Versions 1 and 3 stays near the same value as the exact version. As for version 2 and 4 show a slim variant. Overall version 2 of the proposed accelerator return the highest benefits in terms of power and time, also is the case with version 5. The difference been in the average delay time, since in the last version a considerable increment can be seen and since it is a prevail occurrence affecting most of the process, the highest benefits comes from the second version.

| Accelerator | Area(ELB) |         | Delay $(ns)$ | 1       | Power Estimation (mW) |

|-------------|-----------|---------|--------------|---------|-----------------------|

|             |           | Minimum | Average      | Maximum |                       |

| Sobel       | 197       | 10.30   | 22.54        | 26.12   | 162.62                |

| Sobel 1     | 207       | 9.97    | 22.80        | 29.25   | 161.60                |

| Sobel 2     | 192       | 10.78   | 20.41        | 25.90   | 158.18                |

| Sobel 3     | 219       | 10.12   | 21.86        | 25.64   | 161.27                |

| Sobel 4     | 191       | 10.52   | 22.59        | 26.04   | 159.72                |

| Sobel 5     | 183       | 10.0295 | 24.19        | 20.49   | 154.74                |

Table 3.6: Sobel Accelerators Characterization

All the data gathered from the above study would help understand the characteristics behind all the approximate accelerators, but the behavior in a full system would be study in the next chapter and how can it surpass its exact counterpart and software usage.

## Chapter 4

# Interfacing accelerators and a softcore processors

With the design of approximate accelerators, the next step towards a complete multicore system leads to the construction of a model that implements a singl core and an accelerator. By doing this, it become clearer the requirements and appropriate setting in order to proceed into a larger, multi-core design. The architectures presented are based on the NIOS II softcore processor, which consists on a high performance 32 bits design elaborated from a Hardvar architecture, and it is been optimized for applications on FPGAs, enabling configuration of several capabilities, at real time, accordingly to performance needs.

The NIOS II softcore, as a standalone processor, has several advantages in its use in designing complex systems that incorporate a mixture of custom logic and Altera own IPs (Intellectual Property). It allows the use of two different versions of processors, NIOS II/f is adapted for faster performance and has the most configurable options, such as a unique memory management and protection units, removal of master ports, external interrupt controller, advance arithmetic logic units and more. On the other hand, the NIOS II/e is an economy core, it is design in order to have the smallest core possible size, resulting in a limiting option and functions; but such is reliable option in slave architectures when not many resources are needed for CPU operation.

The interface and implementation design was done in the Altera Quartus II software, which contains the Qsys Pro tool. This integration system allows to save time and effort by applying automatic interconnect logic to use along with IPs functions and subsystems. Qsys allows to include custom HDL designs, but in order to do so, it is necessary that these are enclosed by one or several interfaces depending on the architecture specific requirements. For any custom component to be used in Qsys, one has to declared the new component creation enabling the import of the design files. After these are imported, they need to be synthesized in order to Qsys check the logic, and mapped the inputs/outputs signals to a corresponding interface. In the case being it will be analyzed three different interface include methods for the involvement of the accelerators: the first using one slave, the next includes two masters and one slave, and a last one utilizing DMA transactions and slave logic.

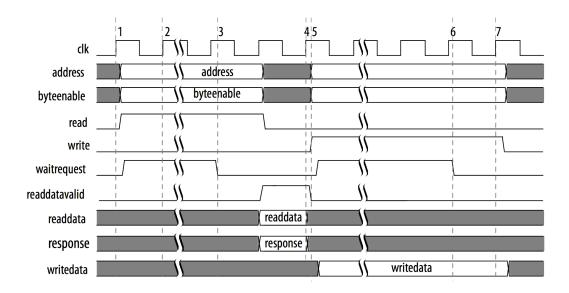

The library present at Qsys, shows a gallery of components already develop that sustains the interactions protocols between subsystems. Varying from streaming interfaces to memory operations, most of the components use the Avalon Memory Mapped maser/slave interface, in order to make specific transfers for both data and commands. In Figure 4.1, it can be seen the signals needed for such implementation, as well as the timing diagram revolving around the specifics of both read and write operations. In the read case, the address command is set so the interface can access an specific action or memory space, the read bit becomes high until waitrequest is deasserted and one cycle after the readdata value is transfer. The write action works very similar, the main difference relies on the fact that the writedata is kept for the duration of the write and waitrequest signal as the waitrequest is deasserted the writedata keeps its value until the write signal turns to low. By introducing this interfaces to the system, is possible to interact between the NIOS II processor, since this is configured as a master, and a custom slave that involves any of the previous accelerator designs.

Once the complete design is finished and generated in Qsys tool, the next step goes into importing the ".qip" file into the Quartus software. This is necessary in order to add all the design files into the project, both customs and from the Altera suite. By naming the Qsys file the same as the top module is possible to generate the component that encapsulates the whole system into the schematic file ".bdf". Finally is possible to start compiling the project to get the ".sopcinfo" and ".sof" files. The first one relates to the hardware information extracted from the Qsys design, this file is loaded as an input in the beginning of the programming in the NIOS II Eclipse integrated development environment (IDE), this way the tool knows the specific component libraries it needs to add in the project, and also possible processor targets for the software. The second file correspond

Figure 4.1: Avalon Memory Mapped Interface Transfers (taken from [1]).

to the downloadable direct volatile configuration, this would set the structure needed in the target FPGA as it is programmed directly into the SRAM cells.

For programming the NIOS II processor Eclipse IDE brings a specific C-code variant, that permits an easier construct and incorporates every element of the hardware design. Facilitating access to any given component by set of commands or Avalon specific address. The NIOS II processor in conjunction with the IDE, also has the advantage of a specific Hardware Abstraction Layer (HAL) which brings a series of specific functions and libraries. This grants the user a more versatile option for configuring specific targets in hardware and managing the desired flow easily. The Binary Space Partitioning (BSP) file, available with each application develop in the IDE, incorporates every library and header files for the execution of the program. The BSP "system.h" header file displays every component characteristics and its address, making possible to reference any part of the design in the application just by naming the specific component or port in it, doing a more precise map in complete designs. For its use in software design, each library is treated as any other in C programming, declaring it, and the needed headers, at top of the file before the coding starts.