Instituto Tecnológico de Costa Rica

Escuela de Ingeniería Electrónica

# TEC Tecnológico de Costa Rica

# Characterization and Validation of Interconnect Models for a PCIExpress Bus

Graduation Project report to qualify for the title of Electronics Engineer with the Licentiate's degree

Javier Andrés Aparicio Morales

Cartago, Costa Rica June 19, 2018 Instituto Tecnológico de Costa Rica Escuela de Ingeniería en Electrónica Graduation Project Evaluation Board

Graduation project presented as a requirement to opt for the title of Electronics Engineering with the academic degree of Licentiate in Electronics Engineering, of the Instituto Tecnológico de Costa Rica.

## **Evaluation** Committee

Tecnológico de Costa Ric Ingeniería Electi M.Sc. Roberto Molina Robles ergio Ar ola Valverde Reviewer Reviewer

Dr.-Ing Renato Rímolo Donadio Advisor

The members of this Court attest that the present graduation work has been approved and meets the standards established by the School of Electronic Engineering.

Cartago, June 13, 2018

## Declaration of authenticity

I declare that the present Project of Graduation has been carried out entirely by my person, using and applying literature referring to the subject and introducing own knowledge.

In the cases in which I have used bibliography, I have proceeded to indicate the sources by means of the respective bibliographic citations. Consequently, I assume full responsibility for the work done and for the content of the corresponding final report.

Javier Andrés Apariçio Morales Cartago, June 13, 2018 ID: 1-1575-0288

# Abstract

In this work a segmented approach to model a PCI Express PCB-buses channel is analyzed. The channel models are built with a 3D full-wave approach in order to compare the results obtained from 2D and 3D simulations, with segmented models that were previously available. The goal is to verify the accuracy of the segmented models and methodologies, in order to assess if a segmented methodology would still be feasible for the next generations systems (e.g. PCIe 5.0). In the development of this work the construction process and necessary simulations to analyze the data transmission are shown, considering the motherboard transition from the via array supporting the package to the PCIe interface connector. Models of vias and transmission lines are developed in order to characterize the PCIe buses.

Keywords: DC-Blocking Capacitors, Differential Signaling, Interconnects, PCIExpress, S Parameters, Signal Integrity.

## Resumen

En este trabajo se analiza un enfoque segmentado para modelar un canal de buses PCB PCI Express. Los modelos de canal se construyen con una aproximación de onda completa 3D para comparar los resultados obtenidos de las simulaciones 2D y 3D, con los modelos segmentados que estaban previamente disponibles. El objetivo es verificar la precisión de los modelos y metodologías segmentadas, con el fin de evaluar si una metodología segmentada todavía sería factible para los sistemas de próxima generación (por ejemplo, PCIe 5.0). En el desarrollo de este trabajo, el proceso de construcción y simulaciones necesarias para analizar la transmisión de datos se mostrarán, teniendo en cuenta la transición de la placa madre desde el arreglo de vías que soporta el paquete hasta el conector de interfaz PCIe. Se desarrollarán modelos de vías y líneas de transmisión para caracterizar los buses PCIe.

Palabras clave: Capacitores de Bloqueo CD, Interconexiones, Integridad de Señal, Parámetros S, PCIExpress, Señales Diferenciales.

# Acknowledgment

First of all I want to thank God for allowing me to be with health, wisdom and understanding until the final stage of my career at TEC. I know that without Him I could not have overcome all the obstacles and challenges that came before me to be where I am now.

Next I want to thank my parents Eliécer and Patricia and my sister Priscilla for having always been with me, although in many moments I know that I could have disappointed them with some personal attitude due to everything that involves being in this great institution, this is why that this project and teaching is for you and I will never find a way to reward them for everything they did for me. I thank Alexa who was also in my university teaching process from very early on, where she was in my most difficult moments and who was a person who understood everything at the time and knew how to help me and always understand my way.

I also want to thank all the teachers of my university education who in some way or another always taught me something, especially the professors of the last two years who were the ones who finished forging my academic teaching. I want to give a special thanks to Dr.-Ing Renato Rímolo Donadio who allowed me his confidence to carry out this project, as well as being a guide during the realization of it, where always he had time to attend me and correct me when was necessary, I will always thankful. I want to thank also to M.Sc. Sergio Arriola for all the help that gave me and for always support us in the most difficult moments of the realization of the project.

Finally I want to thank especially Daniel León, Gabriel Rodríguez and Rolando Coto who were part of my training as a person and professional. Thanks is not a sufficient word for everything you did for me, at the time each of you adopted me as a brother, and I will be eternally grateful for that. At the beginning I thought that my time at the University was going to be solitary but I was wrong about that and now I'm taking three great friends. A special thanks to Brenda Solís, to be part of the group at the end of this stage.

To all the above and those not mentioned, thank you for sharing this stage with me.

Javier Aparicio Morales

Cartago, June 19, 2018

# Contents

| 1        | Intr | roducti            | ion                             | 1  |

|----------|------|--------------------|---------------------------------|----|

|          | 1.1  | Objec <sup>.</sup> | tives                           | 3  |

|          |      | 1.1.1              | General Objective               | 3  |

|          |      | 1.1.2              | Specific Objectives             | 3  |

|          | 1.2  | Work               | organization                    | 3  |

| <b>2</b> | The  | eoretica           | al Foundation                   | 4  |

|          | 2.1  | Printe             | ed Circuit Boards (PCB's)       | 4  |

|          |      | 2.1.1              | PCB Types                       | 5  |

|          |      | 2.1.2              | Vias and Their Effects          | 5  |

|          | 2.2  | Signal             | and Power Integrity             | 8  |

|          |      | 2.2.1              | Signal Integrity                | 8  |

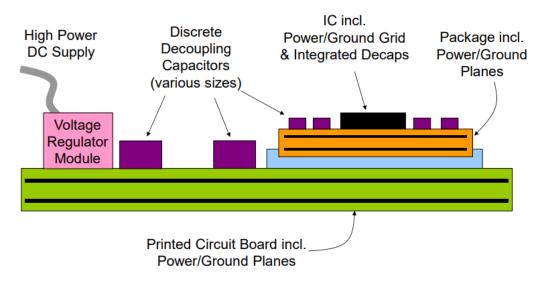

|          |      | 2.2.2              | Power Integrity                 | 14 |

|          | 2.3  | Transı             | mission Lines                   | 15 |

|          |      | 2.3.1              | Microstrip Lines                | 17 |

|          |      | 2.3.2              | Differential Transmission Lines | 17 |

|          | 2.4  | PCIEz              | xpress                          | 19 |

| 3        | Mo   | del Ge             | neration and Validation         | 23 |

|          | 3.1  | Desigr             | n Flow                          | 23 |

|          | 3.2  | Chann              | nel Specifications              | 24 |

|          | 3.3  | Transı             | mission Line                    | 25 |

|          | 3.4  | Via M              | lodel                           | 32 |

| 6        | Bib | liography                                              | 74 |

|----------|-----|--------------------------------------------------------|----|

| <b>5</b> | Con | clusions and Recommendations                           | 73 |

|          | 4.9 | Simulation Time                                        | 71 |

|          | 4.8 | Full PCB Path                                          | 69 |

|          | 4.7 | Transmission line, Via and DC-Blocking Capacitor       | 67 |

|          | 4.6 | Transmission Line and DC-Blocking Capacitor            | 65 |

|          | 4.5 | Transmission Line and Via                              | 62 |

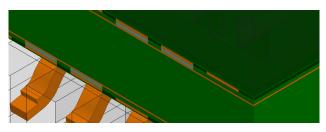

|          | 4.4 | PCIe Connector                                         | 61 |

|          | 4.3 | DC-Blocking Capacitor                                  | 59 |

|          | 4.2 | Vias                                                   | 57 |

|          | 4.1 | Transmission Line                                      | 53 |

| 4        | Mo  | del Comparison and Analysis                            | 53 |

|          |     | 3.7.4 Full PCB Path                                    | 50 |

|          |     | 3.7.3 Transmission line, Via and DC-blocking Capacitor | 49 |

|          |     | 3.7.2 Transmission lines and DC-Blocking Capacitor     | 47 |

|          |     | 3.7.1 Transmission lines and Vias                      | 45 |

|          | 3.7 | Combined Models                                        | 44 |

|          | 3.6 | PCIe Connector                                         | 38 |

|          | 3.5 | DC-Blocking Capacitors                                 | 35 |

# List of Figures

| 1.1  | Direct topology of a PCIe link [4]                                                                                     | 2  |

|------|------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Four layer PCB with blind via (1), buried via (2) and through hole via (3).<br>Taken from [6]                          | 4  |

| 2.2  | Types of Vias in a Multilayer PCB. Taken from [11]                                                                     | 6  |

| 2.3  | Cross-section of a signal and ground via in a multilayered PCB. Taken from [13]                                        | 7  |

| 2.4  | Symmetry of differential lines using vias. Own creation                                                                | 7  |

| 2.5  | Connection of the capacitors at surface level. Taken from $[17]$                                                       | 8  |

| 2.6  | Waves propagation through the line up to a load. Taken from $[19]$                                                     | 9  |

| 2.7  | N-port network with traveling waves. Taken from $[19]$                                                                 | 9  |

| 2.8  | General idea of mutual inductance and mutual capacitance. Taken from $\left[2\right]$ .                                | 11 |

| 2.9  | NEXT and FEXT in two transmission lines. Taken from $[21]$                                                             | 11 |

| 2.10 | Capacitor elements: (a) parallel plate capacitor; (b) gap capacitor; and (c) interdigitated capacitor. Taken from [19] | 12 |

| 2.11 | Response of a sequence of bits. Taken from [22]                                                                        | 13 |

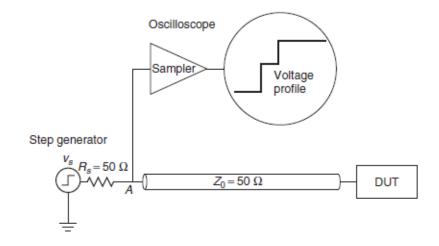

| 2.12 | Generic TDR measurement setup. Taken from $[2]$                                                                        | 13 |

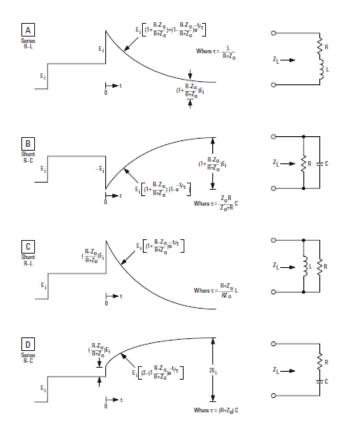

| 2.13 | Response of the DUT in terms of capacitive and inductive behavior. Taken from [23]                                     | 14 |

| 2.14 | Basic PDN Elements. Taken from [25]                                                                                    | 15 |

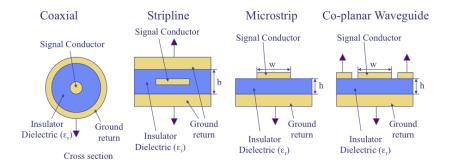

| 2.15 | Transmission lines types. Taken from [28]                                                                              | 16 |

| 2.16 | RLGC model of a transmission line. Taken from $[30]$                                                                   | 16 |

| 2.17 | Microstrip transmission line. Taken from [32]                                                                          | 17 |

| 2.18 | Differential Transmission Line. Taken from [33]                                                                        | 17 |

| 2.19 | Basic link of the PCIe interface point to point. Taken from $[38]$                                                     | 20 |

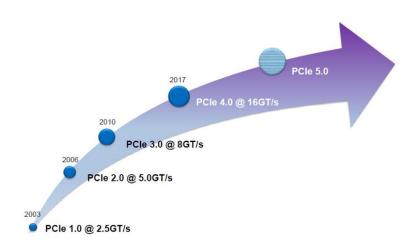

| 2.20 | Speed evolution of the PCIe connector. Taken from [39]                                 | 20 |

|------|----------------------------------------------------------------------------------------|----|

| 2.21 | Common and differential mode voltage of PCIe connector. Taken from $\left[40\right]$ . | 21 |

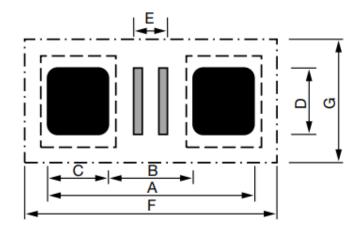

| 2.22 | Diagram of capacitor under the standard 0402. Taken from [41] $\ldots$ .               | 22 |

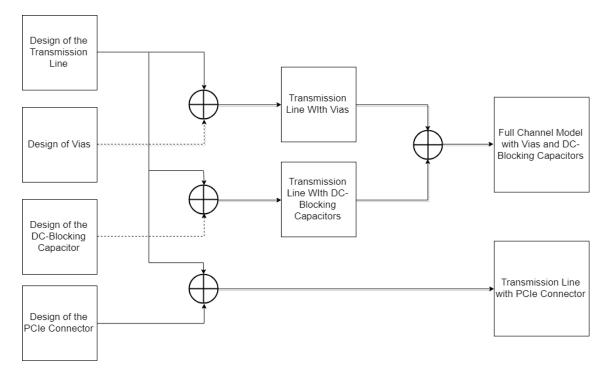

| 3.1  | General flow design of the 3D PCIe bus                                                 | 23 |

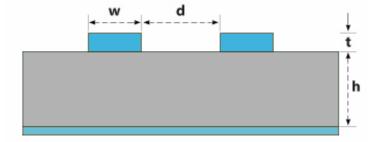

| 3.2  | Guide of the variables of the table 3.2. Taken from $[35]$                             | 25 |

| 3.3  | Differential Transmission line for the BO model from HFSS                              | 26 |

| 3.4  | Port assignment of the differential line                                               | 26 |

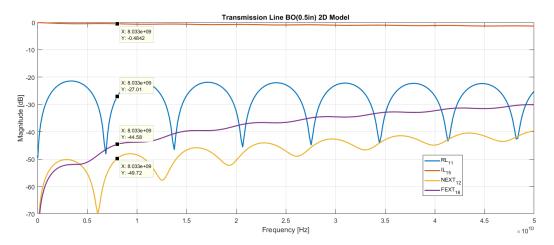

| 3.5  | S Parameters of the breakout transmission line                                         | 27 |

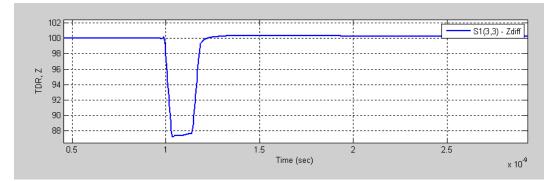

| 3.6  | TDR response of the breakout transmission line                                         | 27 |

| 3.7  | Main Route transmission line model                                                     | 29 |

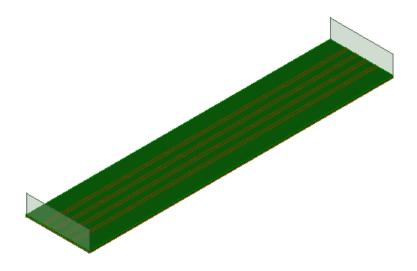

| 3.8  | S Parameters of the MR model                                                           | 29 |

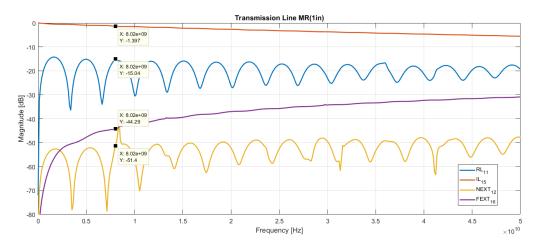

| 3.9  | TDR analysis for the MR line                                                           | 30 |

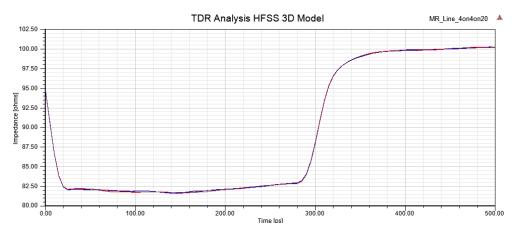

| 3.10 | 2D view of a section of the BO model                                                   | 30 |

| 3.11 | S Parameters of the 2D BO model                                                        | 31 |

| 3.12 | Section of the 2D MR model with a length in the outsider lines of 50 mil in each side  | 31 |

| 3.13 | S Parameters of the 2D MR model                                                        | 31 |

| 3.14 | Via model built in HFSS                                                                | 33 |

| 3.15 | Via model built in HFSS                                                                | 34 |

| 3.16 | S Parameter of the via modeled in HFSS                                                 | 35 |

| 3.17 | TDR test apply to the via model built in HFSS                                          | 35 |

| 3.18 | 3D model of the DC-blocking capacitor                                                  | 36 |

| 3.19 | 3D model of the DC-blocking capacitor simulated in HFSS $\ldots$ $\ldots$ $\ldots$     | 36 |

| 3.20 | Assignation of lumped elements, top view                                               | 37 |

| 3.21 | S parameters of the capacitor with two lumped elements modeled in HFSS .                                            | 38 |

|------|---------------------------------------------------------------------------------------------------------------------|----|

| 3.22 | S parameters of the capacitor with three lumped elements modeled in HFSS                                            | 38 |

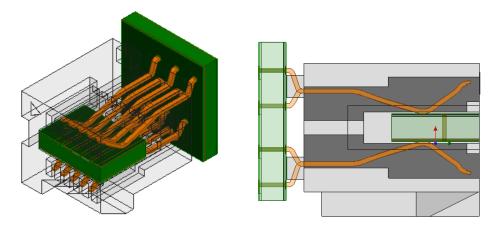

| 3.23 | PCIe connector obtained from Solidworks                                                                             | 39 |

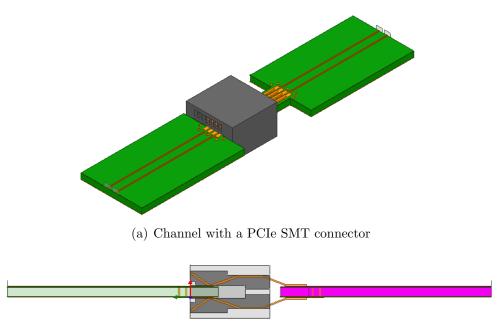

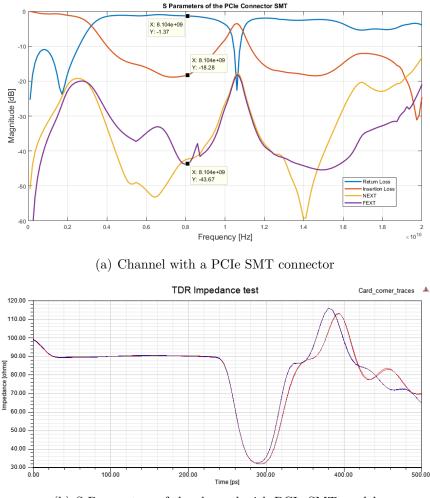

| 3.24 | PCIe SMT connector simulated in HFSS                                                                                | 40 |

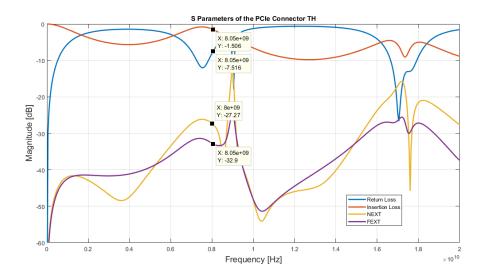

| 3.25 | Simulation results of the channel with PCIe SMT connector $\ldots \ldots \ldots$                                    | 41 |

| 3.26 | Rows assignment of a PCIe connector                                                                                 | 42 |

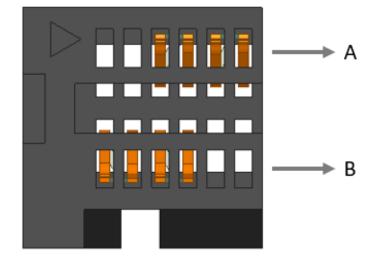

| 3.27 | S Parameters of the simulation of PCIe connector without embedded card                                              | 43 |

| 3.28 | Model of the through hole connector in HFSS                                                                         | 44 |

| 3.29 | S Parameters of the simulation of PCIe connector with embedded cards                                                | 44 |

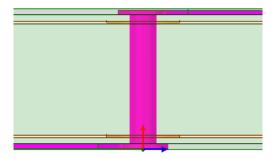

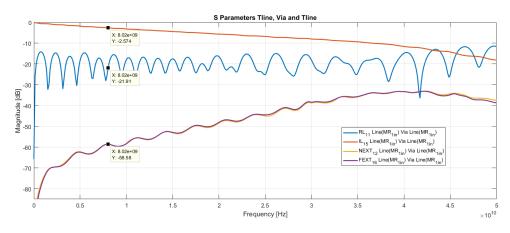

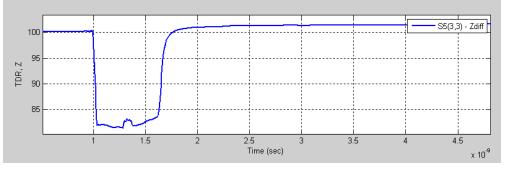

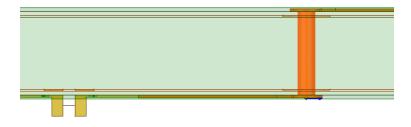

| 3.30 | Transmission Line, Via and Transmission Line Model simulated in HFSS $$                                             | 45 |

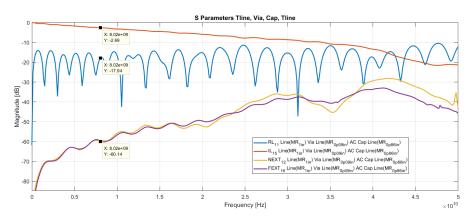

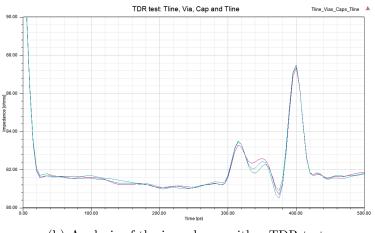

| 3.31 | Behavior of the model described by their S parameters and TDR test $\ldots$ .                                       | 46 |

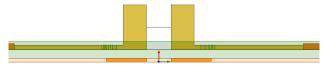

| 3.32 | Different views of the model TL, DC-block Capacitor and TL; and the lumped elements between the metal contact areas | 47 |

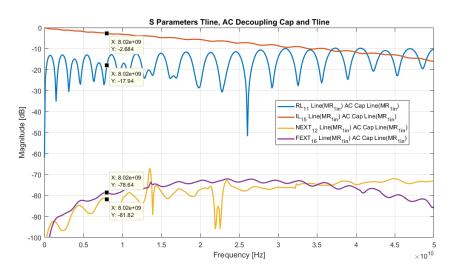

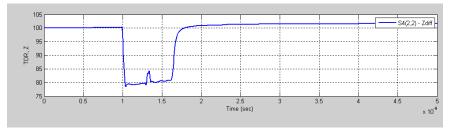

| 3.33 | Frequency and time analysis of the TL and Capacitor model built in ${\rm HFSS}$ .                                   | 48 |

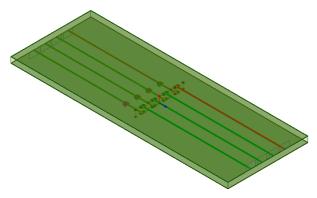

| 3.34 | Model with involves transmission lines, vias and capacitors $\ldots \ldots \ldots$                                  | 49 |

| 3.35 | Simulations results that involve transmission lines, vias and capacitors                                            | 50 |

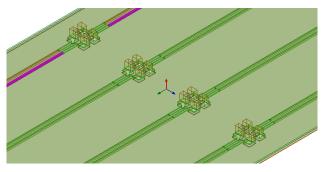

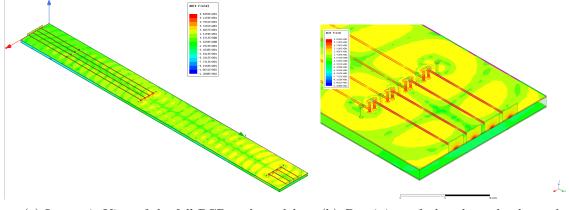

| 3.36 | Full PCB path simulated in HFSS                                                                                     | 51 |

| 3.37 | Simulations results of the channel between the motherboard an the entry previous the PCIe connector                 | 52 |

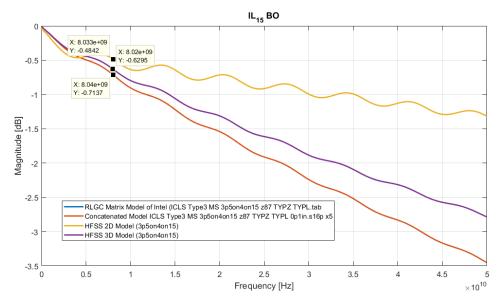

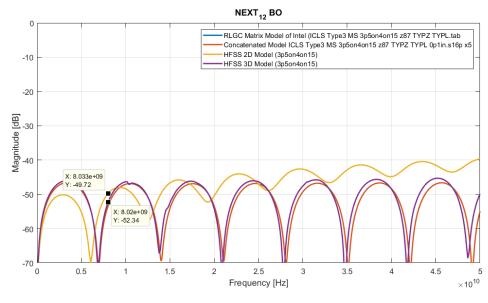

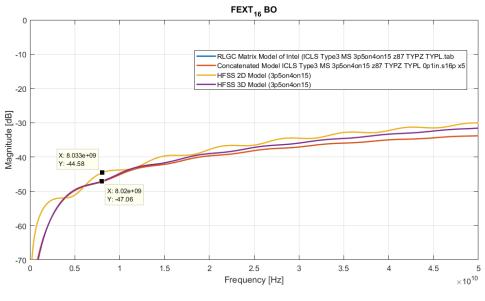

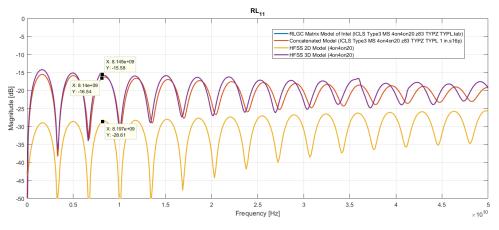

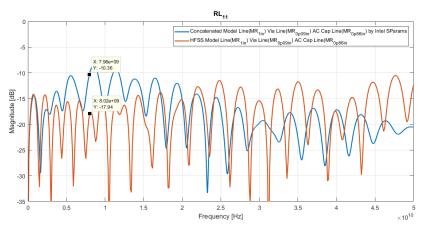

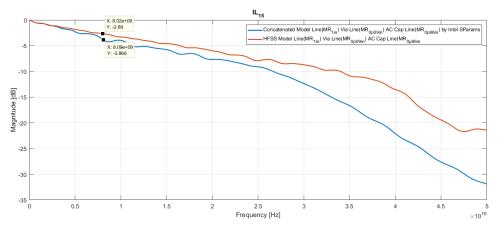

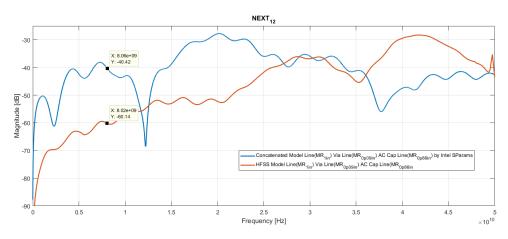

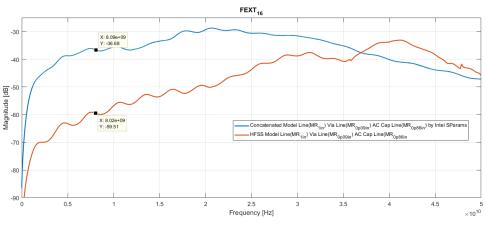

| 4.1  | Correlation of the transmission line of breakout type                                                               | 55 |

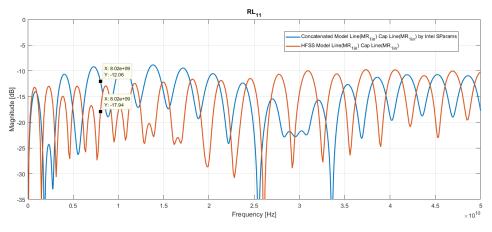

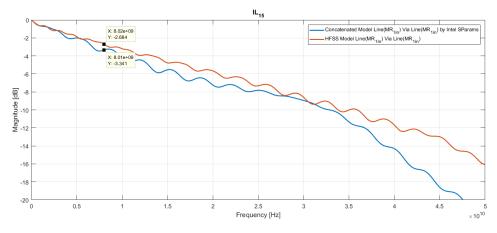

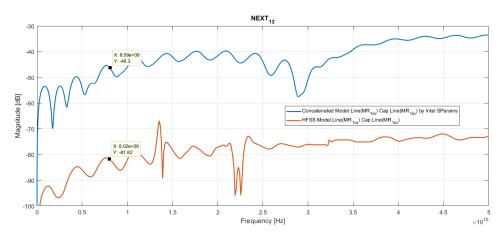

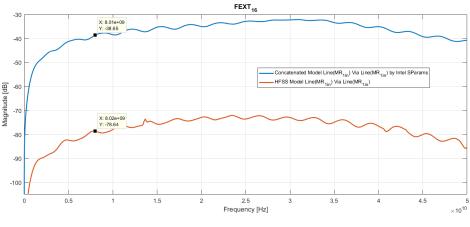

| 4.2  | Correlation of the transmission line of main route type                                                             | 57 |

| 4.3  | Correlation of the Via model                                                                                        | 59 |

| 4.4  | Correlation of the DC-Blocking Capacitor                                                                            | 61 |

| 4.5  | Correlation of the PCIe Connector                                                                                   | 62 |

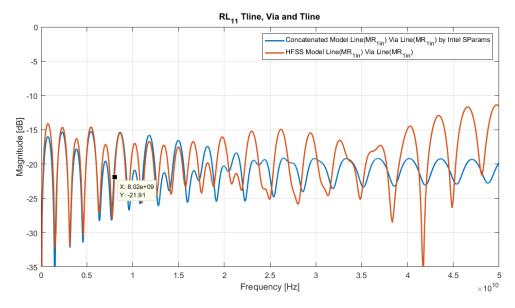

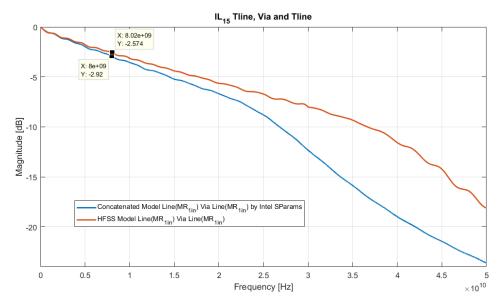

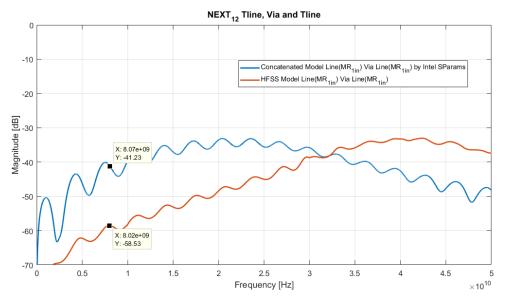

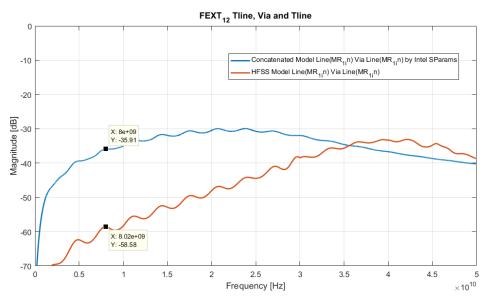

| 4.6  | Correlation of the TL, Via and TL model                                                                             | 65 |

| 4.7 | Correlation of the TL, Capacitor and TL model          | 67 |

|-----|--------------------------------------------------------|----|

| 4.8 | Correlation of the TL, Via, TL, Capacitor and TL model | 69 |

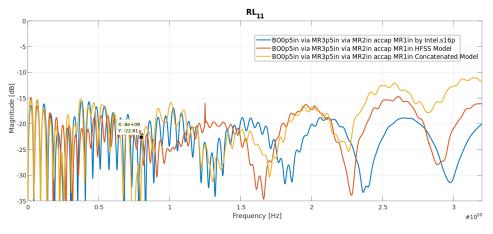

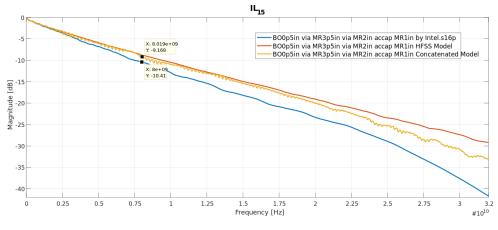

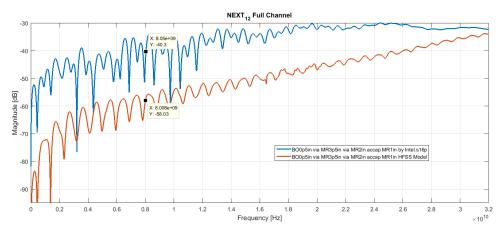

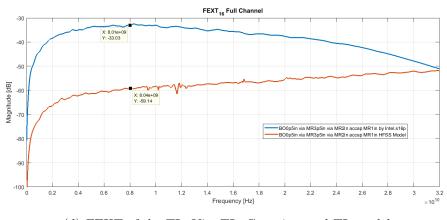

| 4.9 | Correlation of the Full PCB Path Model                 | 70 |

# List of Tables

| 2.1 | Summary of the issues of Signal Power Integrity  | 15 |

|-----|--------------------------------------------------|----|

| 2.2 | Dimensions of capacitor 0402 standard            | 21 |

| 3.1 | Channel Specifications of the four layer stackup | 24 |

| 3.2 | Specifications of the transmission lines         | 25 |

| 3.3 | Specifications for the construction of the vias  | 33 |

| 3.4 | Pins distribution of a PCIe connector            | 42 |

| 4.1 | Simulation comparison by different resources     | 71 |

## 1 Introduction

The Instituto Tecnológico de Costa Rica works on research projects in the field of signal integrity, which consists of the study of the electrical problems that arise in high speed digital designs and the possible solutions to them. This field of interest also belongs to Intel, where they also seek to analyze and verify the transmission of data at high speeds. With the same purpose of research held by ITCR and Intel, a joint collaboration will be carried out to analyze and compare the scope of the project with previous research that exists on the subject.

Signal integrity in modern systems is a concern due to the fact these computer systems are currently operating at speeds in the Gb/s range. Therefore, it is important that the performance of data buses can operate at high speeds without loss of information [1]. It is then sought that the channel designs consider a sufficient bandwidth to transmit these volumes of information. The growth of bandwidth, generates problems at the physical level. Signal integrity problems of a channel include the parasitic effects on discontinuities such as connectors, material losses, and electromagnetic coupling.

Problems with the waveform of the signals also occur. The problem is a wave degradation, distortion or alteration of the waveform. It must be considered that being digital circuits, the signals are binary, therefore the effect on these systems is to achieve the interpretation of the logic levels [2]. Other effects related to high data rate generate are reflections, as well as parasitic effects that arise from the materials that make up the communication channel [3].

PCI Express (PCIe) buses use a set of differential pairs to carry very high speed information between the CPU and the device of interest. Some typical uses of PCIe include graphics cards and storage devices. The fourth generation of the standard uses binary signals at 16 Giga-samples/second (GS/s). The fifth generation (in the process of standardization) will be extended to 32 GS/s [4].

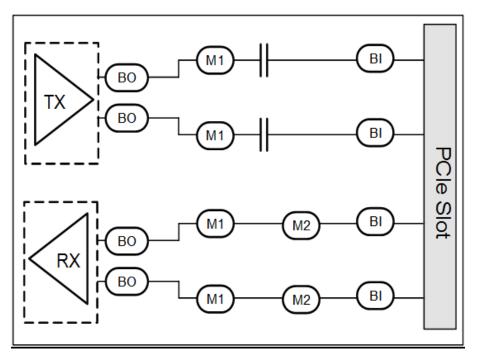

The traditional analysis technique for PCIe buses consists of the mathematical concatenation of separate models, corresponding to the main elements that the signal must pass through. These include the packaging, the socket, the buses, the PCB with vertical interconnections (vias), the DC-blocking capacitors and the connector itself. This topology is depicted in figure 1.1.

Figure 1.1: Direct topology of a PCIe link [4]

Currently, a segmented methodology for the signal paths is being used. Some models are obtained from wave simulators in two dimensions, some others in three dimensions, and some are obtained from measurement results. The concatenation is carried out through the technique of synthesis of S parameters. Although this methodology has been validated in the past, by means of correlations with real measurements. The speeds of operation have increased very significantly and there is doubt about the validity of the method for higher speeds.

Therefore, it is sought to validate the method by segmentation of a PCIe bus through a three dimensional model of the same topology, where the main characteristics of the signal transmission channel at the simulation level are contemplated. To achieve the characterization of a three dimensional model, it must be taken into account how the model is constituted, this to consider all the dimensions it has, as well as the electrical characteristics it has.

Taking into consideration the technical specifications of the topology, the next step is to construct the 3D models that constitute the PCIExpress bus at PCB level. Both, independent parts of the models and the concatenated signal paths are compared. Other important considerations are the impedances in the differential pairs, the materials by which the components are built, as well the transmission gains and reflection that exist in the channel's discontinuities. Also DC-blocking caps are included, in order to block the DC component of the signal.

The construction of a three dimensional model will allow to determine the most significant

electrical effects that can be observed by the S parameters. Among the effects are the insertion loss, return loss, crosstalk and impedance profile [3]. With the obtained results of the three dimensional model, they will be compared with the results obtained from equivalent models, They are generated by means of synthesis of S parameters of the individual models generated by different methodologies.

This will make it possible to observe differences between both approaches, in order to determine if the use of the segmented models are still valid for the new operating speeds, or if it is necessary to make a change to the three dimensional model since it contemplates more interactions in comparison to the segmented one. It will be shown that similarities, dependences of parameters that must be revised with respect to real platform.

### 1.1. Objectives

#### 1.1.1. General Objective

Evaluate a methodology for modeling high speed electrical channels in PCIe 4.0 interfaces, based on three dimensional models and full wave simulations.

#### 1.1.2. Specific Objectives

- 1. Develop the physical channel model based on the specification of a PCIe bus from a personal computer motherboard.

- 2. Simulate through a wave based approach to complete the channel model, obtaining the microwave parameters as a result of the simulation.

- 3. Validate the simulated three dimensional model with respect to available alternative simulation methodologies.

#### 1.2. Work organization

This report contains various chapters. *Chapter 2* deals with theoretically base terms such as: transmission lines, parameters obtained from the lines, PCB's (Printed Circuit Board), stackups, vias, materials technology, the PCIe connector and signal and power integrity.

In the *Chapter 3* will describe the steps necessary for the realization of high speed channels, where the corresponding results and analysis will be attached. Everything will be done in three dimensional models using a full-wave approach.

Finally, the *Chapter 4* a correlation will be made between the results obtained from chapter three and the results that Intel has about these channels through segmented methods. This correlation will seek to validate the segmentation of the channels or if it's necessary emigrate to three dimensional models for the development of these channels.

## 2 Theoretical Foundation

In this section, concepts such as printed circuit boards, how they are made up, materials and components that are included in the printed circuit boards will be addressed. A vital issue in the transmission of high speed signals will be mentioned and this is the signal and power integrity. These envelop a general level analysis in the frequency and time domain. The transmission lines, which are the paths to transmit signals, are essential in high data speed channels and will be also mentioned. Finally, the PCI Express connector will be mentioned. It will be treated how it is constituted, physical and electrical characteristics it has, as well as how the connector works.

## 2.1. Printed Circuit Boards (PCB's)

The section on printed circuits boards will be developed, where topics such as the types of PCB's, elements containing PCB's and the materials that are usually used in manufacturing processes will be discussed in greater depth.

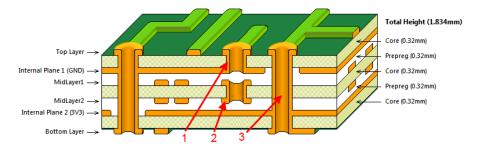

A PCB (Printed Circuit Board) or PWB (Printed Wire Board) is a mechanism to support and electrical. Perform connections of electronics components through conductive traces, pads and other characteristics recorded in copper sheets on a non-conductive substrate are allowed [5]. Figure 2.1 is observed a four layer PCB with a transversal cut. Besides, there are different types of PCB's in terms of the number of layers or types. In addition, these must be complied with the next characteristics [6]:

- Power source of energy for the other layers.

- Dissipation of energy from its components.

- Serve as support for the components.

- Achieve to interconnect the circuit components with various layers making up the PCB.

Figure 2.1: Four layer PCB with blind via (1), buried via (2) and through hole via (3). Taken from [6]

### 2.1.1. PCB Types

As it was mentioned implicitly in the characteristics. A laminated PCB can be of different forms, these are [6]-[7]:

- PCB of one layer: Conductive layer and a dielectric is consisted. This type can contain an upper layer of soldermask and silkscreen. It is used in low cost and high production circuits due to the simplicity with which this type of board is allowed.

- Two layer PCB: Two conductive layers are composed. They can be connected through vias or with the use of surface mount technologies (SMT). The connections are made in the plates at a surface level without the need to use vias [8]. Meaning that these plates use most of the time only one of the conductive layers.

- PCB with more than two layers: In more complex designs are used when a greater number of interconnections are used. Also to avoid unwanted effects such as heat or electromagnetic phenomena.

- Flexible PCB: Flexible and non-rigid materials are used. The great advantage is that can be used on surfaces that are bent. In addition to reducing the cost and weight compared to a rigid plate.

## 2.1.2. Vias and Their Effects

As shown in figure 2.1, there are different types of vias that to the main traces of the conductive layers are connected. These routes according to the signal topology and the reference levels that are part of the transition are classified. A type is the through hole via, which all the layers of the PCB pass through. There is the blind via that crosses only a section of the layers and it is visible only by one of the outer layers of the PCB. Finally, there is the buried via that is internally and it is not visible in any of the outer layers of the PCB [9].

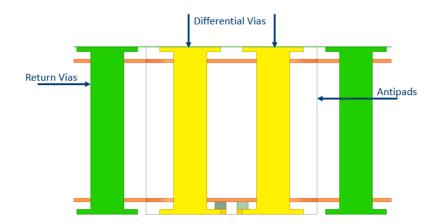

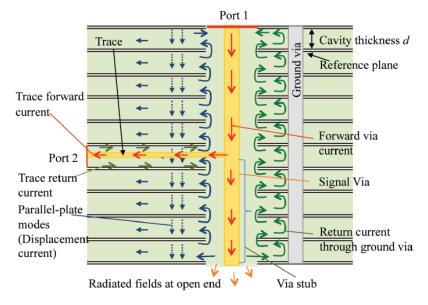

Effects in the signals transmission of the common or differential lines are produced by signal vias. The most loss are generated by these vias because field lines are created by the antipads around the vias and an increase in capacitive coupling is generated. This is represented as an additional discontinuity in signal propagation [10].

The signal vias with antipads are used, as the reference and power planes from the main signal can be isolated. There are different structures such as rectangular, circular, oval. Structures that use oval antipads are the ones that have the lowest reflection. Figure 2.2 is depicted an example of vias in a PCB, where the reference vias, antipads, and the signal vias are included [11].

Another type of via is the return via. In greater quantity to reduce the crosstalk effects they are used, which between the signal vias and the reference planes are originated. The signal to noise ratio is maintained by this via. A portion of the currents of the vias flow over the reference planes are allowed. These vias nearby to the signal vias must be, to eliminate unwanted effects, which in the parallel plates are originated [9]-[12].

A cross-section of a signal via is depicted in figure 2.3. It can be seen that the signal travels in this via and with a stripline is connected . A return current will travel back to the via input (upper side of the figure), through the power or reference vias if exist on the PCB. If these vias do not exist, the current will return as a displacement current between the reference planes. Signal losses and interactions with other PCB elements are generated by this displacement. At the level of electric fields around the vias, modes on the parallel plates are generated, which results in a loss of power and reduction of signal strength. Finally, the highest impedance coupling between the vias and the traces to avoid reflections that result in power losses must be presented. A considerable number of return vias allow the signal loss to be reduced considerably [13].

Figure 2.2: Types of Vias in a Multilayer PCB. Taken from [11]

Figure 2.3: Cross-section of a signal and ground via in a multilayered PCB. Taken from [13]

Copper in a PCB is used. For the conductive traces, the power, and reference planes are used. Other layers such as dielectrics, use a material called prepreg. It is a fiber sheet impregnated with resin, which allows pressure and heat to join stacked cores. The core is another cured dielectric bonded together by two metal plates. Another material that can be used as a dielectric is FR4. The arrangement of these layers together with the conductors is called *stackup* [9]-[14].

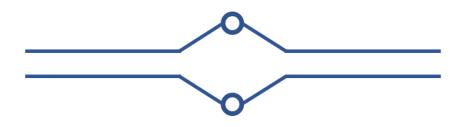

The traces on the superficial layers, as well as the internal, must have symmetry and not have angles of  $90^{\circ}$  in the traces. This not to generate effects such as interference and discontinuities through the line. On the other hand, when it is necessary to make capacitor connections at surface level in the traces. It is recommended not to use a large number of them due discontinuities and increase the losses in high frequency by to parasitic effects can be generated [15]-[16]. Figure 2.4 and 2.5 are shown how the symmetry of the traces should be when using differential channels. In addition to how the capacitors should be connected to the surface level with the traces of the outer layers of the PCB [17].

Figure 2.4: Symmetry of differential lines using vias. Own creation

Figure 2.5: Connection of the capacitors at surface level. Taken from [17]

### 2.2. Signal and Power Integrity

Currently, computer systems demand high rates of data transmission, which implies that must be operated at high frequencies, in the order of GHz. This implies that there are signal integrity problems as well as power problems in the channels. In this section will talk about what should be considered when performing high speed analysis.

## 2.2.1. Signal Integrity

It is the analysis, design, and validation of the interconnections, in order to guarantee the transmission of the signal, avoiding reflections and losses to the maximum [18]. The analysis in time and frequency domain is related. For example in the frequency domain can be analyzed by S parameters and in the time domain is used an analysis called time domain reflectometry (TDR).

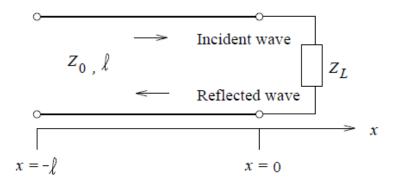

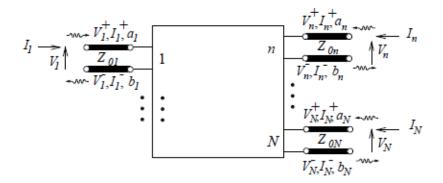

The analysis in the frequency domain normally are related with the utilization of microwave network parameters called S parameters. These parameters represent an equivalent circuit of elements as impedances, inductors, and capacitors. The S Parameters have Nports input and M-ports of exit. Due that in high frequency is worked, it is necessary to establish resistive terminals in the ports that won't be used at the moment of the measure in order to prevent reflections or interference. The S parameters with forward and backward traveling waves on a transmission line are related, also with the power flow [19].

Measures as reflection coefficient or transmission coefficient indicate how much of the power is reflected and transmitted respectively. Figure 2.6 is depicted the propagation of waves through a line up to a load. The incident wave and reflected wave are observed that by the reflection and transmission coefficients are represented [19]. In general, these parameters in a matrix are represented, where the size of it, depends on the number of ports that device under test (DUT) has.

Figure 2.6: Waves propagation through the line up to a load. Taken from [19]

A N-port network is a generalization of the DUT, where in figure 2.7 is shown the general example and as was told, can be a matrix of  $N \times N$  size as [19]:

| $S_{11}$ | $S_{12}$ | $S_{13}$ |     | $S_{1N}$       |

|----------|----------|----------|-----|----------------|

| $S_{21}$ | $S_{22}$ | $S_{23}$ |     | $S_{2N}$       |

| $S_{31}$ | $S_{32}$ | $S_{33}$ |     | $S_{3N}$       |

| :        | :        | :        | •.  | :              |

| $S_{N1}$ | $S_{N2}$ | $S_{N3}$ | •   | $\dot{S}_{NN}$ |

| $D_{N1}$ | $D_{N2}$ | $D_N3$   | ••• | $[O_{NN}]$     |

A parameter  $S_{ij}$  is a measure of a specific input and exit port, where port j is the transmission of the incident wave and port i is the reflected wave. The coefficients can be defined as:

- $S_{ii}$ : reflection coefficient seen looking port i

- $S_{ij}$ : transmission coefficient from j to i

Figure 2.7: N-port network with traveling waves. Taken from [19] 9

If the DUT has 4 single ports or more, making a conversion to mixed mode is allowed. This mode is a combination of the single ports and if is only used the single mode, it does not provide much insight information about the common and differential mode about the reflection and transmission. The mixed mode is used to know about the differential and common behavior. For the conversion to the mixed mode a four port example will be used but in general, is described as [20]:

$$[S^{mm}] = [M][S][M]^{-1} \tag{1}$$

where

$$[S^{mm}] = \begin{bmatrix} S_{dd11} & S_{dd12} & S_{dc11} & S_{dc12} \\ S_{dd21} & S_{dd22} & S_{dc21} & S_{dc22} \\ S_{cd11} & S_{cd12} & S_{cc11} & S_{cc12} \\ S_{cd21} & S_{cd22} & S_{cc21} & S_{cc22} \end{bmatrix}$$

,

$$[S] = \begin{bmatrix} S_{11} & S_{12} & S_{13} & S_{14} \\ S_{21} & S_{22} & S_{23} & S_{24} \\ S_{31} & S_{32} & S_{33} & S_{33} \\ S_{41} & S_{42} & S_{43} & S_{44} \end{bmatrix} \text{ and } [M] = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 1 & 1 & 0 & -1 \\ 0 & 0 & 1 & 1 \end{bmatrix}$$

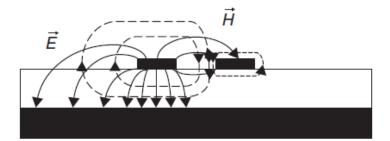

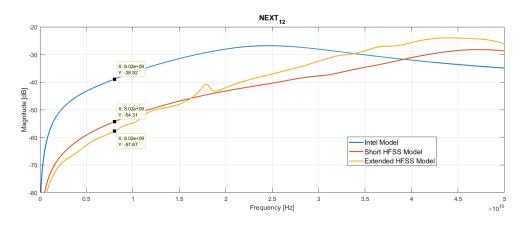

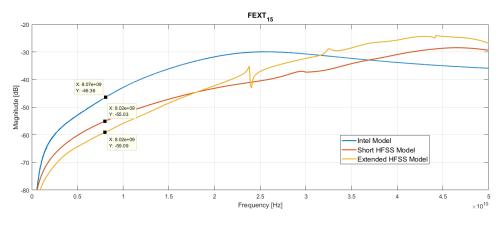

A signal along the line in an electromagnetic waveform is propagated. Between two or more conductors are established. When existing more than a conductor line and they are nearby between each other, the electric and magnetic fields of the signal will interact with adjacent conductors. A coupling of energy from one line to other is induced when a stimulus is applied and is called *crosstalk*. For example in digital systems many lines in parallel through packages are routed. Connectors, PCB's and the crosstalk is important to contemplate it. Signal integrity by the crosstalk is affected. The characteristic impedance and propagation velocity are modified. Also the noise margins are reduced [2].

For crosstalk, the mutual inductance and capacitance by coupled of multiple conductors due to the magnetic field (mutual inductance) and electric field (mutual capacitance) are caused. Mutual inductance  $L_M$  induces a current from a driven line onto a quiet line by means of the magnetic field. While the mutual capacitance  $C_M$  is the coupling of conductors by the electric field [2]. Figure 2.8 is observed the principle of mutual inductance and capacitive are[2].

Figure 2.8: General idea of mutual inductance and mutual capacitance. Taken from [2]

Finally, crosstalk either at the beginning of the stimulus or the end of the line can be measured, in other words, the load. The first method is called NEXT and with the coupled of energy at the beginning of two nearby lines are related. The second is the FEXT and between the source and the final of the next line is measured, in figure 2.9 is observed how the crosstalk has to be measured [21].

Figure 2.9: NEXT and FEXT in two transmission lines. Taken from [21]

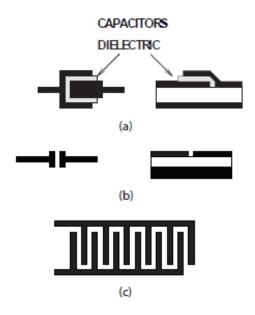

Another requirement in RF circuits is the use of lumped elements for many purposes like matching networks, lossless DC connection, harmonic tuning and to ensure stability at frequencies below the cutoff frequency [19]. The primary lumped elements on RF circuits are resistors, capacitors, and inductors. In PCIe channels, the used of capacitors are necessary to block the DC component. Figure 2.10 shows different lumped capacitors, and for this lumped element exists different types such as [19]:

- Metal-dielectric-metal capacitor: using the interconnect metalization.

- Metal-dielectric-semiconductor capacitor: it's used in MOS transistor.

- Semiconductor junction capacitor: Either the capacitance of pn junction or Schottky barrier.

Figure 2.10: Capacitor elements: (a) parallel plate capacitor; (b) gap capacitor; and (c) interdigitated capacitor. Taken from [19]

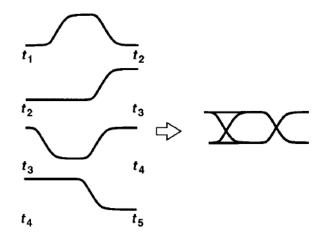

For the analysis of the transmissions lines, time domain analysis is another possibility to see the transmission of the signals. The matching of the line with a stimulus and see the response through the time can be observed. A common test pattern in time domain is a PRBS (Pseudo Random Binary Sequence), which can emulate the random nature of binary coded information. To see this behavior, an eye diagram is used. All the bits into a short interval are folded in this diagram and an accumulation of distorted edges and levels voltages are displayed [22].

An example of this diagram is observed in figure 2.11 where four bits are observed in the diagram. It can be seen the opening of the eye indicates that it is possible to differentiate between a "high" and "low" level. This opening to the level voltage of the bit is related and depends on the system in which voltage as a high level or low level is taken. Another fact that can be studied from the diagram is the time transition of the bits. Different times of the bit transitions produce an issue called jitter and this is the difference between all the transitions of the bits. A good jitter is when the changes occur approximately at the same time. The distortion of the transmission happens for the mismatch of the impedance, noise and, demand of a system. Beyond of frequency of operation will cause a closing of the eye, which also would increases the jitter [22].

Figure 2.11: Response of a sequence of bits. Taken from [22]

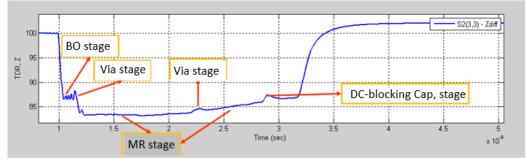

A technique is used in time domain analysis is the Time Domain Reflectometry (TDR). This technique use the premise of multiple reflections derive an impedance profile of the DUT. To make this measure a diagram like in figure 2.12 is used. A step function is used that is the stimulus and is driven to the DUT through a 50  $\Omega$  cable. With an oscilloscope the waveform at A is observed, which represents the voltage profile of the reflected waves. This voltage to an impedance profile is converted, which to measure the characteristic impedance and propagation delay of the line can be used. By the waveform of the impedance profile, a DUT can have inductive or capacitive behavior and also see exactly, where the discontinuity is due to the elements of the system [2]. A response of the TDR in terms of inductive and capacitive behavior is observed in figure 2.13, where a decrease of the plot is a capacitive trend and when increased is an inductive trend [23].

Figure 2.12: Generic TDR measurement setup. Taken from [2]

Figure 2.13: Response of the DUT in terms of capacitive and inductive behavior. Taken from [23]

## 2.2.2. Power Integrity

Responsible to analyze and design the network source of the system, starting with coupling, assignment planes and stackup. An important element for the analysis of the power integrity is the PDN (Power Delivery Network) which candles for a stable source voltage [18]-[24]. For a good analysis of the PDN, several elements must be analyzed and these are:

- DC Resistance: By the geometry of the net is determined, also is a conductor material. To reduce the resistance is preferable to use wide traces and avoid discontinuities.

- Capacitor Loop Inductance: By this parameter, the effectiveness of a decoupling capacitor is quantified. To achieve the decoupling, the reference and power planes should be near to the top and bottom layers. Use capacitors near of this planes to avoid discontinuities are recommended.

- Target Impedance: To calculate the impedance of all power network is used, starting from S parameters and TDR analysis are calculated.

All the elements of the PDN can be depicted in figure 2.14. The DC resistance is showed caused by the source voltage. Decoupling in various ways either using DC-blocking caps

or power and reference planes can be given. Finally, all the network must have a target impedance that is the operation value for the system works well [25]. Table 2.1 is showed the issues either for signal integrity or power integrity that have been discussed previously.

Figure 2.14: Basic PDN Elements. Taken from [25]

Table 2.1: Summary of the issues of Signal Power Integrity

| Element          | Issues                                                          |  |  |  |

|------------------|-----------------------------------------------------------------|--|--|--|

| Signal Integrity | Attenuation, Reflection, Dispersion, Interference and Crosstalk |  |  |  |

| Power Integrity  | Voltage Drop, Noise and Crosstalk                               |  |  |  |

## 2.3. Transmission Lines

As mentioned, the fundamental part in the transmission of electrical signals are the medium by which are transmitted, for instance, in the transmission of signals between the motherboard, interfaces, and peripherals. The transmission lines are the most used because operate in the speed ranges in which this work is being developed.

The transmission lines to transmit electrical energy and signals from one point to another are used, from a source to some load [26]. These from two or more parallel conductors are composed that connect the source with the load. There are different types of lines, which can be observed in figure 2.15. Between the types are the coaxial cables, the microstrip lines, and striplines. The lines can be differential and common. For the design of PCB's in high frequency microstrips are used due they are the most common [27]-[28].

Figure 2.15: Transmission lines types. Taken from [28]

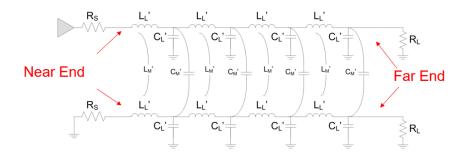

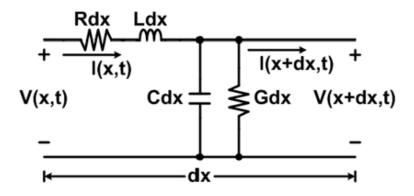

A transmission line from their lumped elements can be modeled using a differential line segment and their associated lumped elements per unit length. These elements are resistances (R), inductors (L), conductances (G) and capacitors (C), and a combination of all are known as RLGC matrix. A representation of this, is observed in figure 2.16. The equations to model the transmission line with RLGC elements are [29]-[30]-[31]:

$$\frac{\partial \mathbf{v}(x,\omega)}{\partial x} = (\mathbf{R}(\omega) + \mathbf{j}\omega\mathbf{L}(\omega))\mathbf{i}(x,\omega)$$

(2)

$$\frac{\partial \mathbf{i}(x,\omega)}{\partial x} = (\mathbf{G}(\omega) + \mathbf{j}\omega\mathbf{C}(\omega))\mathbf{v}(x,\omega)$$

(3)

Figure 2.16: RLGC model of a transmission line. Taken from [30]

With the equations 2 and 3 the propagation constant  $\gamma$  and the impedance Zo of the line can be obtained. These equations are described as [29]:

$$\gamma = \sqrt{(R + j\omega L)(G + j\omega C)} \tag{4}$$

$$Zo = \sqrt{\frac{(R+j\omega L)}{(G+j\omega C)}}$$

(5)

## 2.3.1. Microstrip Lines

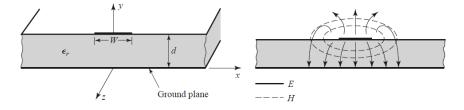

The microstrip lines are the most popular lines because by a photolithographic process are manufactured. In addition are easy to minimize and integrate passive and active microwave devices. The conductive plane that is the main trace has a width W and a reference plane. Both by a dielectric of thickness d and a relative permittivity  $\epsilon_{\rm r}$  are separated. The description of the microstrip is depicted in figure 2.17 as well as a sketch of the field lines [32].

Figure 2.17: Microstrip transmission line. Taken from [32]

## 2.3.2. Differential Transmission Lines

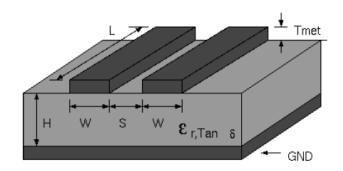

These type of lines consist of two conductive traces separated by a specific space with a common reference plane. These are used to cancel the effects generated by transmitting a single signal on a single line. Therefore with a differential mode, there are a positive signal and another negative. This configuration causes the effects of the fields to be eliminated and thus avoid degradation of the signals [33]. This topology is depicted in figure 2.18.

Figure 2.18: Differential Transmission Line. Taken from [33]

As mentioned, using a differential mode helps to avoid signal degradation, but more specifically help to [34]:

- 1. Reduction of collapse in the lines.

- 2. Reduction of electromagnetic interference.

- 3. Improvement in noise immunity.

- 4. Less sensitivity to attenuation.

A correct differential pair occurs when uniformity in the cross sections, symmetry in the width of the line and the spacing of the dielectric is presented. Finally, there must be a coupling of the source, the line, and the load. The first parameter to approximate in a differential line is the impedance of this, and the following equation is used [35]:

$$Z_{\rm d} = \frac{174}{\sqrt{\epsilon_{\rm r} + 1.41}} \ln \frac{5.98h}{0.8w + t} (1 - 0.48e^{-0.96\frac{d}{h}}) \tag{6}$$

Where:

- $\epsilon_{\rm r}$  is the relative permittivity of the dielectric.

- *h* is the thickness of the dielectric.

- w is the width of the trace.

- t is the thickness of the trace.

As the lines are not ideal, these will have losses. They can be represented as reflections in the line discontinuities. To represent the losses, the coefficients of reflection and transmission are used. These coefficients indicate how much of the power and transmitted through the medium is reflected [27]. These are parameters that manage to describe the behavior of a transmission line.

Other losses that are generated in the transmission lines are [2]-[36]-[37]:

- The effect of the dielectric produces that the waves transmission is being in function of the frequency. Since the fundamental frequency, the transmitted power will be minimum. Besides it gets complicated when the dielectric isn't homogeneous because will present more discontinuities than usually.

- DC loss is found and depends on the resistivity of the conductor in a total area in which the current is flowing. This loss can be represented as:

$$R = \frac{L\rho}{Wt} \tag{7}$$

Where L is the length of the line,  $\rho$  is the resistivity of the conductor material, W and t are the width and the thickness of the line respectively.

• The skin effect is other loss and is a physical phenomenon related to high frequency transmission on a wire. The electromagnetic field of the wire causes most of the electrical current to become crowded at the edges of the wire. Thus causes that effective resistance of the cable is changed and the current through the wire flows in the skin of the conductor. An increased signal attenuation at higher frequencies is produced. Also can be called as skin depth and can be represent as:

$$\sigma = \sqrt{\frac{\rho}{f\mu\pi}} \tag{8}$$

Where  $\rho$  is the resistivity of the metal, f is the frequency and  $\mu$  is the permeability of free space.

## 2.4. PCIExpress

This section contains the basic features of the interface that is used in this work which is the PCI Express. How this connector is constituted, the velocities that can manage and some considerations to built the channel will be shown. It's important to remember that not only is the PCIe connector but also there are buses from a motherboard to the connector. Hence, all these details in sought to get the best transmission of the signals must be considered.

This interface is a bus or network of communications of high speed in short lengths and with low latency for the interconnection of devices and card among themselves inside a chassis. Among the main features that this interface has are [38]:

- 1. The network by full duplex point to point links is built. Each link by lanes is composed, where each lane is full duplex and consists of two pairs of threads, a pair of transmission and another of reception. The voltage transmitted is differential, which helps to the noise immunity. A diagram of the link is shown in figure 2.19.

- 2. The transmission is serial, it means that in each lane the transmission of bits in both directions is serial to avoid problems of jitter in the receiver.

- 3. The bus speed is scalable by adding more lanes to the link where it can be scaled by 1 (x1), 2 (x2), 4 (x4), 8 (x8), 16 (x16) and 32 (x32) lanes per link. Depending on the number of lanes the data transmission is given.

- 4. Possibility of changing and connecting hot cards, especially in servers.

Figure 2.19: Basic link of the PCIe interface point to point. Taken from [38]

Currently, with the PCIe 4.0 is managed to reach speeds up to 16 GB/s per lane. This evolution in the speed of the connector is shown in figure 2.20 [39]. As described in chapter one, a typical PCB link used with this interface is modeled. It contains the breakout in the channel and the characteristics that the breakout must have are [4]:

- The maximum length of seven inches is allowed if is greater than seven then, loss of information will exist.

- The length of each channel must be the same in each lane and must be connected with as few layers as possible.

- The insertion loss permitted is -4 dB at a frequency of 8 GHz and the return loss lesser than -15 dB at the same frequency as for insertion loss. To achieve this, low loss dielectrics are used.

- The impedance of these channels is 100  $\Omega$  in differential mode and 50  $\Omega$  in common mode. For greater accuracy, the channel must have a tolerance of  $\pm$  20% of the mentioned values.

Figure 2.20: Speed evolution of the PCIe connector. Taken from [39] 20

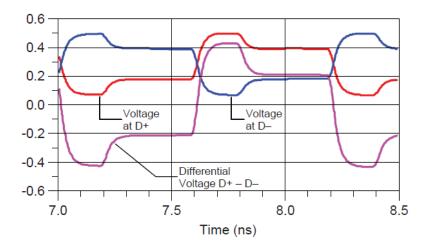

Given the PCIe operates with differential channels, the interface is managed with differential voltages. A conductor has a negative voltage  $V_{D_-}$  and another positive  $V_{D_+}$ . The differential voltage is defined as  $V_{DIFF} = V_{D_+} - V_{D_-}$  and the common mode voltage  $V_{CM}$  is obtained from the average of the differential voltages, means  $V_{CM} = (V_{D_+} + V_{D_-})/2$ . Figure 2.21 is exemplified the voltage levels of common and differential mode of the breakout, that are connected to the interface PCIe [4]-[40].

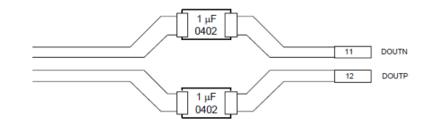

The channels used by PCIe require serial capacitors that allow a blocking of the CD component between the reception and transmission stage. The capacitance values used are based on the 0402 standards, which specify the dimensions of the capacitor as length, width and height [41]. The values of capacitance allowed by PCIe 4.0 have a minimum value of 176 to 265 nF as the maximum value [4].

The measurements that the capacitor has, they are given by the 0402 standard which is a SMT assembly. In figure 2.22, the guide to build the capacitor is shown, where the letters represent measures that are shown in the table 2.2 [41].

Figure 2.21: Common and differential mode voltage of PCIe connector. Taken from [40]

Table 2.2: Dimensions of capacitor 0402 standard

| Standard | A (mm) | B (mm) | C (mm) | D (mm) | E (mm) | F (mm) | G (mm) |

|----------|--------|--------|--------|--------|--------|--------|--------|

| 0402     | 1.50   | 0.40   | 0.50   | 0.50   | 0.10   | 1.75   | 0.95   |

Figure 2.22: Diagram of capacitor under the standard 0402. Taken from [41]

## **3** Model Generation and Validation

This chapter deals with the modeling of the channel and its building blocks. Each element, has a simulation. The signal integrity and the TDR is analyzed to see the target impedance of the block, in view of complying with the impedance of the system.

## 3.1. Design Flow

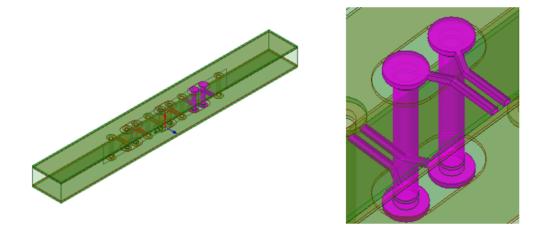

Figure 3.1 is shown the general blocks of the bus. The basic models have to be done first and these are the transmission line, vias, DC-Blocking capacitors and a model of the PCIe connector.

Figure 3.1: General flow design of the 3D PCIe bus

Once the basics models with their respective results are validated. The combined of the basic models must be made. These are three models, which are transmissions lines with vias, transmissions lines with DC-Blocking capacitors and a small card, which is connected to the PCIe connector. Finally, a full channel model with the combined of the capacitors, transmission lines, and vias is built. The goal is to see the response of the channel. The stage between the transmission of a motherboard up to the PCIe connector by the small blocks are conformed.

For the development of the blocks of the figure 3.1, an electromagnetic simulation environment is used. This is Ansys HFSS, it is suitable for high speed designs. In general, to obtain a result from the simulator, a mesh must be defined. An iterative algorithm solves the fields of the model and refines the mesh until the S parameters converge below a threshold defined by the user. Once the algorithm converged, the solving process is started. The software can use different methods to make the sweep and for this work will be using the *Finite Element Method* (FEM), which handles complex materials and geometries. For the 2D simulations the *Boundary Element Method* (BEM) is used. This approach is a numerical method to resolve equations in partial derivatives linear that have been formulated as integral equations [42].

Another tool that will permit the analysis of the blocks is a mathematical software called Matlab. This will allow to analyze the S Parameters obtained from the HFFS simulator. Measures relate to the transmission and reflection of the signals can be studied. Besides, make transformations from single to differential, as well as to concatenate the S parameters, to make the larger models [43].

## 3.2. Channel Specifications

The building block models are developed considering a four layer stackup. Some basic models as the transmission lines or the DC-Blocking capacitors can be modeled using only two layers of the four. Table 3.1 show the specifications of the different layers, wherein the case of the microstrip lines are two types that in later subsections will be developed. These specifications are available and also used for the segmented approach.

| Routing | Layer           | Tline | Thickness | Dielectric | Loss    |

|---------|-----------------|-------|-----------|------------|---------|

| Layer   | Description     | Type  | (mil)     | Constant   | Tangent |

|         | Soldermask      |       | 0.65      | 3.4        | 0.031   |

| 1       | Breakout (BO),  | MS    | 1.9       |            |         |

|         | Main Route (MR) | NID I |           |            |         |

|         | Prepreg         |       | 2.75      | 3.7        | 0.017   |

| 2       | Power           | PWR   | 1.1811    |            |         |

|         | Core            |       | 49.01575  | 4.125      | 0.015   |

| 3       | Ground          | GND   | 1.1811    |            |         |

|         | Prepreg         |       | 2.75      | 3.7        | 0.017   |

| 4       | Breakout (BO),  | MS    | 1.9       |            |         |

|         | Main Route (MR) |       |           |            |         |

|         | Soldermask      |       | 0.65      | 3.4        | 0.031   |

Table 3.1: Channel Specifications of the four layer stackup

For the range of frequency that will be covered for all the models, a broadband sweep will be used. This band covers from DC up to 50 GHz, with a step of 0.125 GHz and a total points of the sweep are 400 with an error of the 4%. A TDR analysis will be applied, and the principal feature that this analysis has, its the time rise which is 40 ps.

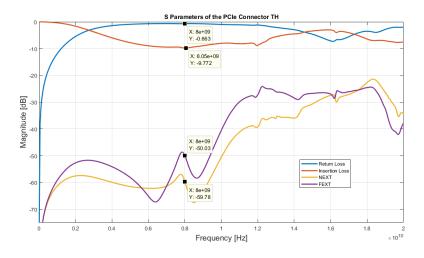

#### 3.3. Transmission Line

In this section the transmission line models will be modeled that PCIe buses use. These are two models, where one is located near to the motherboard and the other is the main route that allows the signal to be carried from the motherboard to the prior stage to the connector.

The construction of the transmission lines contains two types of lines. The first is the breakout (BO), where these are the lines that come from the motherboard, that are nearby than the main route (MR) lines. They are used to connect the motherboard with the PCIe connector. The target impedance of the lines must be 85  $\Omega$  in differential mode. For calculate this impedance, a microstrip calculator was used with a guide of the variables in figure 3.2. The next dimensions to build the lines were used and are shown in the table 3.2, where the length variables are in mil [35]:

| Tline | Trace<br>Width (w) | Trace<br>Separation (d) | Trace<br>Thickness (t) | Dielectric<br>Thickness (h) | Dielectric<br>Constant |

|-------|--------------------|-------------------------|------------------------|-----------------------------|------------------------|

| BO    | 3.5                | 4                       | 1.9                    | 2.75                        | 3.7                    |

| MR    | 4                  | 4                       | 1.9                    | 2.75                        | 3.7                    |

Table 3.2: Specifications of the transmission lines

Figure 3.2: Guide of the variables of the table 3.2. Taken from [35]

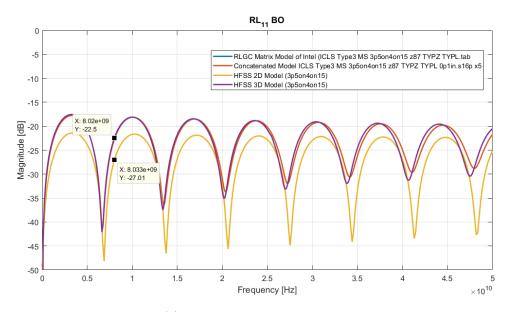

The impedance through the line for the BO is approximately 84.96  $\Omega$  and for the MR line is 79.42  $\Omega$ . It is important to consider that the calculator assumes ideal widths of the line. It means that the EDW doesn't exist. The EDW is the settling of the copper. The impedance of the line by the effect of this settling is influenced. The EDW for both models is 0.5 mils on each side of the line.

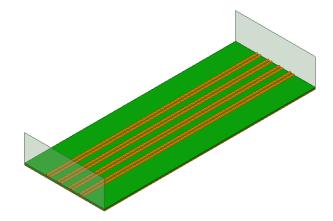

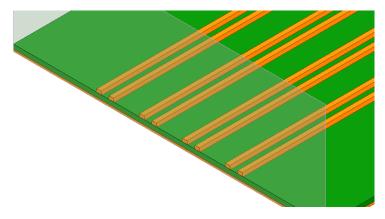

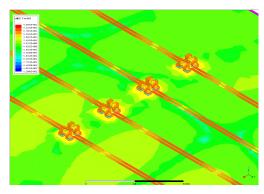

Four differential pairs for both models have been modeled. A length of 500 mils for the BO model and 1000 mils for the MR model. In figure 3.3 is observed the differential transmission line built in HFSS, where this model was excited by *Waveports*. This port can be seen as the transparent sheet. The criterion in terms of height and width for the port is 15 times the thickness of the dielectric and the reference plane for the height. While for the width is 10 times the width of the trace, if the width of trace is higher than the thickness of the dielectric [44]. The port is started from the reference plane and goes up to the signal layer. The port is depicted in figure 3.4.

Figure 3.3: Differential Transmission line for the BO model from HFSS

Figure 3.4: Port assignment of the differential line

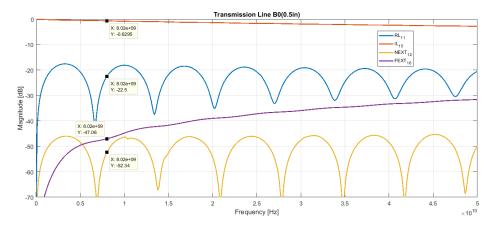

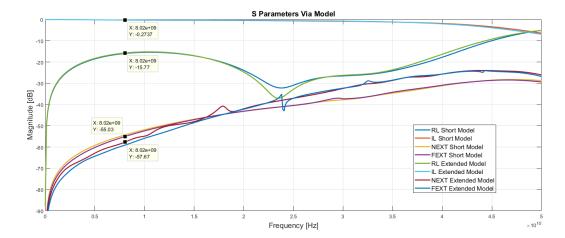

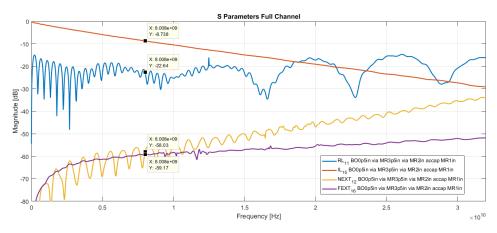

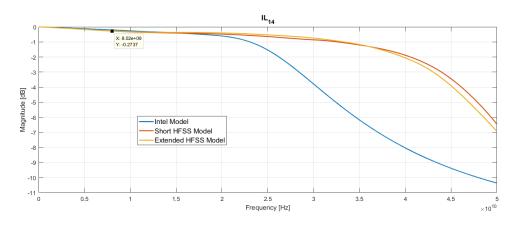

The results to analyze of each line are the return loss, insertion loss, crosstalk (NEXT and FEXT) and the response in the time domain (TDR). In figure 3.5 are shown the measures mentioned. At first look, the line has the typical behavior of a transmission line. The reflection parameter has periodic resonances, while the transmission parameter decreases as the frequency increases.

Figure 3.5: S Parameters of the breakout transmission line

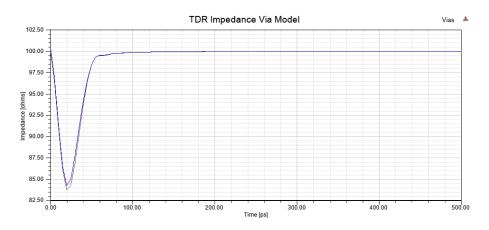

From figure 3.5, most of the power is transmitted. Besides the reflection is below the -15 dB, so is complying with the criteria for the BO stage. Also, the crosstalk doesn't affect a lot this line, because is below the reflection parameter. To verify the impedance of the line, a TDR analysis is used to check the response of the line due to a stimulus. This can be shown in figure 3.6, where the impedance is below the 88  $\Omega$ , which is near to the target impedance of the system.

Figure 3.6: TDR response of the breakout transmission line

All the models that were built contemplate a loss model. As the materials that are used are dependent on the frequency. So to get a better approximation and result, these loss model are used. Exist different loss models as [45]-[46]:

• Debye: It is referred to the relaxation response of a dielectric medium to an external, oscillating electric field. This relaxation is often described in terms of permittivity as a function of frequency, which can be described by the Debye equation. This equation is usually expressed in the complex permittivity  $\epsilon$  of a medium as a function of the field's frequency  $\omega$ . HFSS allows specifying an upper and lower measurement frequency, and the loss tangent and relative permittivity values at the same frequencies.

- Piecewise Linear: This defines the material property values as a restricted form of a piecewise linear model with exactly 3 segments (flat, linear, flat). It must be specified property's values at an upper and lower corner frequency. Then between these corners, the software linearly interpolates the material properties. Above and below the corner frequencies, the software (HFSS) extrapolates the property values as constants.

- Multipole Debye: The software dynamically generates frequency dependent expressions for relative permittivity and loss tangent from the data of the relative permittivity and loss tangent versus frequency.

- Djordjevic-Sarkar: This model loss is used for low loss dielectric materials commonly used in PCB's and packages. This model uses an infinite distribution of poles to model the frequency response.

The loss model Djordjevic-Sarkar is used, because for this model only needed a specific value of the dielectric constant and the loss tangent at a specific frequency. The Debye model needs two values of the same characteristics at different frequencies, which implies inaccuracy in the models. The values of the table 3.1 were measured at a frequency of 5 GHz.

To get more accurate with the models, a roughness model was set. The roughness is a representation of the traces through small spheres, to set the roughness in HFSS the radius of the spheres and the Hall-Huray Surface Ratio must be known, which are a relation between the trapezoid area, the number of the spheres that will be modeled and the radius of the same. These data were provided as all the previous data and the radius that were used in the models was 0.5  $\mu$ m and a ratio of 1.78.

The next transmission line is the main route line and was modeled. This with a length of 1000 mils. The line is depicted in figure 3.7, and the biggest difference of this model respect BO is that this uses different widths mentioned in table 3.2, as well as the length of the line. The dark green layer of the model is the soldermask, which is above the traces. In this model is shown in comparison with the BO model, due it was necessary to first show the transmission lines. And for this one, to verify that all models use all the layers mentioned in table 3.1. The S parameters are shown in figure 3.8. For the excitation, waveport was used and has the same criteria as the BO model.

Figure 3.7: Main Route transmission line model

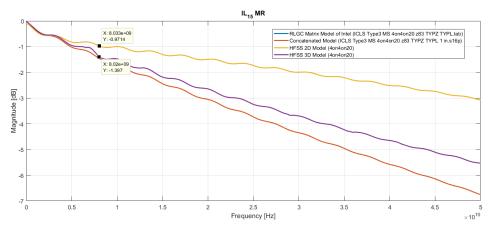

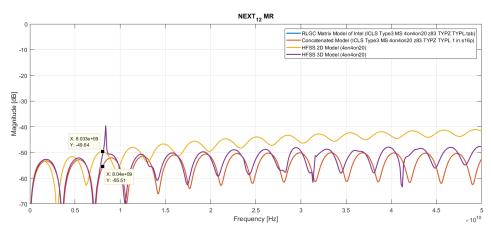

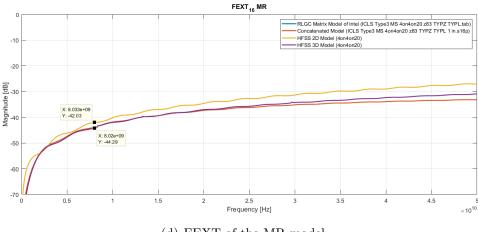

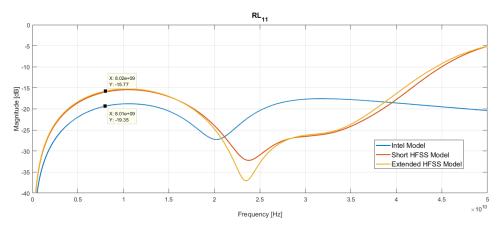

Figure 3.8: S Parameters of the MR model

As it is observed in figure 3.8, the transmission is -1.397 dB that represents most of the transmission of the power at the fundamental frequency of 8 GHz. Besides, the crosstalk doesn't affect the adjacent lines because the coupling between the differential lines is low. The response in the time domain of this line is shown in figure 3.9. The line has a resistive behavior due the graph is below of the target impedance of 85  $\Omega$ , approximately the line is in 83  $\Omega$  and doesn't have great changes during the stimulus. The graph was taken from HFSS.

Figure 3.9: TDR analysis for the MR line

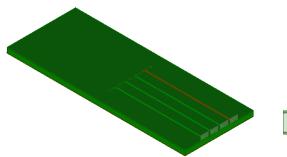

Ansys HFSS can model geometries from their 2D views. It is an option to get faster results, assuming that the 2D section does not change over time. An advantage of this solver is the time that it takes to simulate a model, it is around 30 min or less. While a 3D project could take at least a couple of hours. Besides, the computational resources that are used, are also bigger. This option to model 2D views is only for transmission lines because all the layers have the same length (depth). The 2D solver of HFSS can describe the line from their RLGC parameters that in the end can be transformed to S parameters.

Also, the breakout (BO) and main route (MR) lines with the 2D tool were modeled. First, the results of the BO will be shown, in figure 3.10 is observed the model. The excitations have to be assigned to the conductors. In this case, exist eight conductors and the reference plane, which is in the bottom layer. The results either the RLGC matrix or the S parameters can be extracted, where it just necessary define the depth of the line and the reference impedance. The results of the 2D BO line are shown in figure 3.11.

Figure 3.10: 2D view of a section of the BO model

Figure 3.11: S Parameters of the 2D BO model

The results of the figure 3.11 shown the same trend as the results of the figure 3.5. It implies the most of the power is transmitted. The same happens with the crosstalk, it is observed that the next and fext don't influence on the rest of the lines. To approximate this line the Djordjevic-Sarkar loss model was used, with the reference measurements that have been provided. The 2D models can't be applied an analysis in time domain, the TDR analysis can use only in 3D models. In figure 3.12 is shown the 2D MR model, where this model is very similar to the 2D BO model. The difference is in the length and the width that the lines have. It is specified in table 3.2 and figure 3.13 is shown the results of the main route model in 2D.

Figure 3.12: Section of the 2D MR model with a length in the outsider lines of 50 mil in each side

Figure 3.13: S Parameters of the 2D MR model 31

This result using the Debye loss model was obtained. Due the Djordjevic-Sarkar model also was used and the power was -40 dB, which it is something desirable but far away from the reality. Even these results are far from the results obtained in figure 3.8. The lines have a high transmission and a low reflection. To set the Debye loss model in the prepreg layer the next data were used:

- Frequency: 1 GHz as lower and 8 GHz as higher

- Dielectric Constant: 3.5 as lower and 3.7 as higher

- Loss tangent: 0.015 as lower and 0.017 as higher

For the soldermask layer the Debye loss model was approximated with the next data:

- Frequency: 1 GHz as lower and 8 GHz as higher

- Dielectric Constant: 3.2 as lower and 3.4 as higher

- Loss tangent: 0.029 as lower and 0.031 as higher

Something to consider is that the Debye loss is an approximation. The measures at different frequencies is unknown. For this case, the other value was put with some criteria. To get accuracy, measurements at different frequencies must be made to use in the right way this loss model.

## 3.4. Via Model

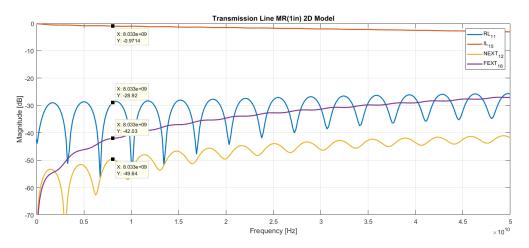

This subsection contains the built of a via. In chapter 2 was mentioned that can be ground via or signal via. For the modeling, the dimensions of the diameters of the different cylinders that compose the vias and spacing between them are shown next. The data were provided and are shown in table 3.3:

| Section                | Dimension (mil)                                                                              |  |  |

|------------------------|----------------------------------------------------------------------------------------------|--|--|

| Drill                  | 12                                                                                           |  |  |

| Pad                    | 22                                                                                           |  |  |

| Antipad                | 32                                                                                           |  |  |

| Thickness pad          | Main trace's thickness                                                                       |  |  |

| Thickness drill        | $2^{*}(\text{prepreg's thickness} + \text{reference's thickness}) + \text{core's thickness}$ |  |  |

| Pitch between Negative | 30                                                                                           |  |  |

| and Positive via       | 50                                                                                           |  |  |

| Distance between       | 60                                                                                           |  |  |

| differential vias      |                                                                                              |  |  |

| Distance between       |                                                                                              |  |  |

| differential vias      | 30                                                                                           |  |  |

| and ground vias        |                                                                                              |  |  |

Table 3.3: Specifications for the construction of the vias

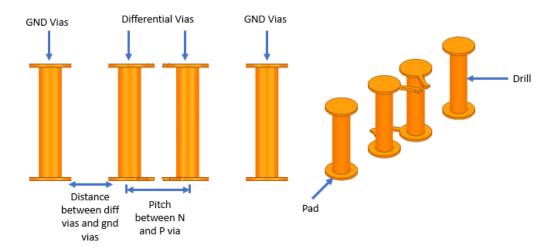

All these elements, have different proposes that were mentioned in chapter 2. For example the antipad, drill, pad and ground vias. Figure 3.14 is shown the via model. The only element that isn't mentioned in the figure is the antipad. This was described previously and is a dimension that only applies to the signal vias and not for the ground vias. The spacings have to be respected because permit that the differential pairs don't influence in other pairs.

Figure 3.14: Via model built in HFSS

The vias were modeled as an array of three differential pairs, where between them are ground vias just like the figure 3.14. This model has all the layers, because the vias are through hole in the PCIe buses models. Due only the vias are modeled, and for the excitations are using waveports and are on the edges of the radiation box, imply that the traces which are out of the via, can't have a considerable length. This would introduce transmission lines effects because also would modeled the access lines. Also as part of the simulations results, a model with a card with more width is attached, the same as the length of the card.

Figure 3.15 are shown two subfigures, in the subfigure a is shown the model realized in HFSS, with the ground vias and the differential vias. The length of the trace outside of the antipad is 27.5 mil. Also can be shown the extraction of the antipad in the copper layers, which are the inner layers of the stackup. In the subfigure b is shown a front view of the board of the via and can be observed all the layers of the stackup and how these are distributed.

(a) Whole design and extraction of the antipad in the copper layers

(b) Stackup of the vias with a frontal view

Figure 3.15: Via model built in HFSS

The simulation results will be shown below. The same electrical parameters and a TDR analysis will be analyzed to see the behavior and impedance of the via. Figures 3.16 and

## 3.17 are showed the analysis in frequency and time respectively.

Figure 3.16: S Parameter of the via modeled in HFSS

Figure 3.17: TDR test apply to the via model built in HFSS

A bandwidth up to 40 GHz with a loss of -2 dB for the response in the frequency domain of the via is shown. Most of the power is transmitted and the minimum of the power is reflected. While the crosstalk doesn't have a considerable influence in the pairs of the board. Hence, for the fundamental frequency of the PCIe 4.0, the via operates with the minimum lost power. The response in the TDR is observed in figure 3.17. The small behavior of the transmission line that the model has is observed. After that the response, in an inductive is changed because the graph starts to go up as a normal inductive element saw in chapter 2.

## 3.5. DC-Blocking Capacitors

This subsection consists of the characterization of the DC-Blocking capacitor. The principal function of the capacitor is blocking the DC component and decoupling the signals between the transmission and reception stages. The goal is to model the losses that a capacitor can generate in high frequency, due at high frequency the behavior of the capacitor is totally different at DC. This subsection will show the 3D model in HFSS as the results obtained from the simulation.

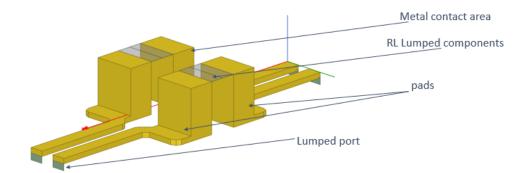

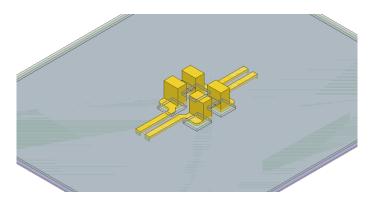

To get results near at the segmented models, a capacitor model was provided. It is with the standard of 0201, and is different to the mentioned in chapter 2 but has a capacitance permitted in the standard that the PCIe buses use. This capacitance is 220 nF. As mentioned, it is looked to model the high frequency loss, for that a library was used. It's just necessary to put the standard of the capacitor and the normal value of the same and the library provides the values of the lumped elements of the capacitor.

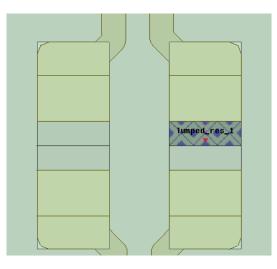

From the library, the inductance has a value of 177.865 pH and the resistance has a value of 27.918 m $\Omega$ . In figure 3.18 is shown the 3D model of the capacitor, where the principal parts of the same are marked. These are the metal contact, the RL lumped components, the pads and the lumped ports. The model with lumped port is used because the model was defined to approximate without transmission lines. Also, an advantage of this is that it's not necessary to put the port in the edges of the radiation box. It is had a certain flexibility to model the component with more area for the other layers. The model that was simulated is depicted in figure 3.19 with the prepreg, soldermask and reference layer.

Figure 3.18: 3D model of the DC-blocking capacitor

Figure 3.19: 3D model of the DC-blocking capacitor simulated in HFSS 36

As appreciated from figure 3.19, the reference layer has four extractions, which exactly have the same measures of the capacitor's pads. This is realized to ensure the minimum reflection of the power by another factor that doesn't be itself. The modeling of the lumped elements was realized with an assignation of *lumped RLC element* that HFSS has. When chosen this assignation, just the value of the lumped element is defined and reviewed that the current flow goes on the same way for both lumped elements (R and L). The position of the lumped elements could be three and are the top, middle or bottom of the capacitor. The middle was chosen to have the middle result of the capacitor and not have an extreme result due to the position of the lumped elements. The lumped element (R) assignation is shown in figure 3.20, wherein the other rectangle that is below is the assignation of the inductance element.

Figure 3.20: Assignation of lumped elements, top view

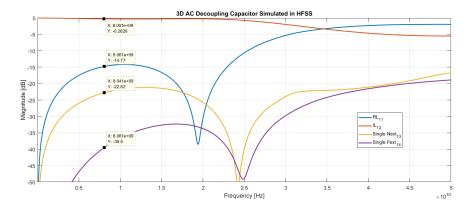

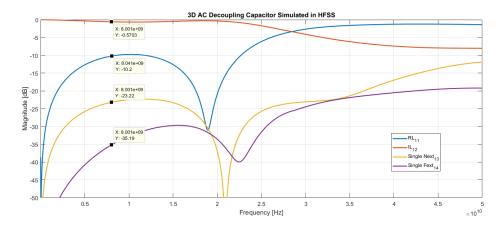

The results of the model are shown in figure 3.21. In general, most of the power is transmitted at the fundamental frequency. The losses that are generated by the capacitor, doesn't affect a lot in the transmission. It will be necessary to corroborate this measure with some complex cases, where involves transmission lines and capacitors as a first approach. A problem with this model is that can't be generated a TDR analysis because the ports utilized were lumped type. This implies that the port can't read the nearby lines that could be transformed in differential pairs. Besides, only one differential pair is modeled and by that, the crosstalk in differential mode can't be analyzed. So only was analyzed in single mode and was shown in figure 3.21, where the influence of the crosstalk is despised it.

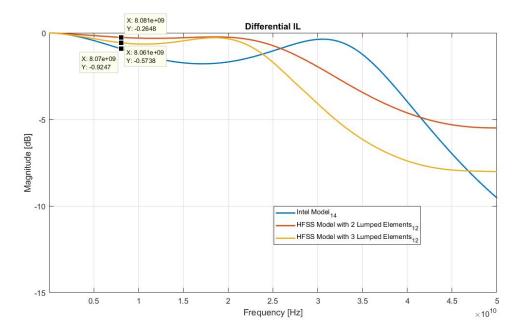

Figure 3.21: S parameters of the capacitor with two lumped elements modeled in HFSS

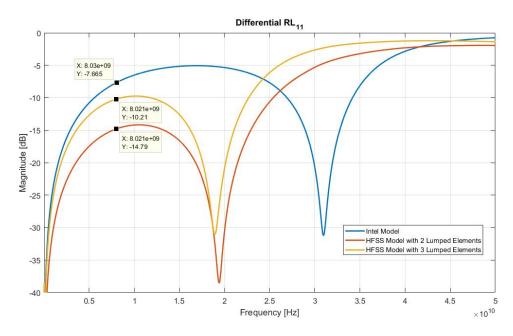

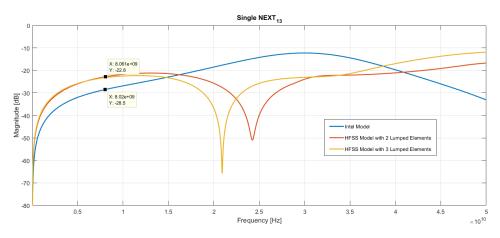

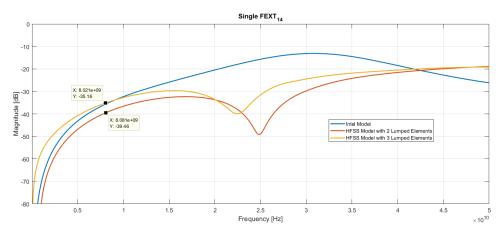

Another model was executed to include a third lumped element that was the capacitance with a value of 135.932 nF obtained from the same library. The results are shown in figure 3.22, and in comparison with the previous results, the big difference is the reflection. These are increased and are expectable because the model has more losses than had before. But for the fundamental of 8 GHz, the reflected energy is minimum. Also, in this case, a TDR cannot be applied due for the same reasons as the two lumped element model.

Figure 3.22: S parameters of the capacitor with three lumped elements modeled in HFSS

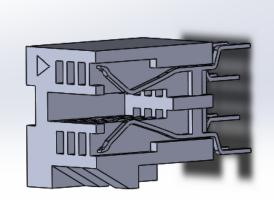

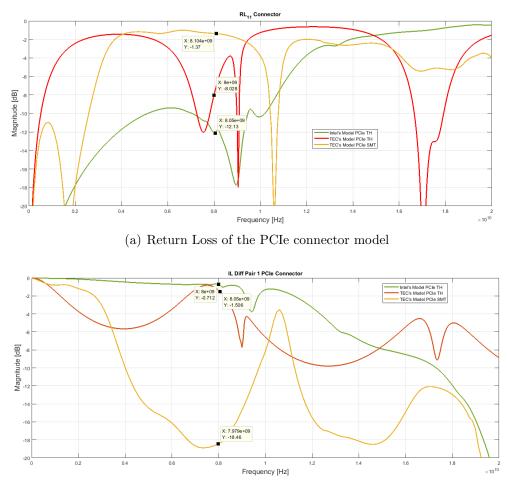

## 3.6. PCIe Connector