### Instituto Tecnológico de Costa Rica

Escuela de Ingeniería Electrónica

Maestría en Electrónica

# TEC Tecnológico de Costa Rica

# Design of Elastic Buffers for USB Transceivers in a 180-nm CMOS process

Master thesis presented in partial fulfillment of the requirements to obtain the degree of Master of Science in Electronics – Microelectronics

Javier Andrés Aparicio Morales

Cartago, Costa Rica

September, 2021

Instituto Tecnológico de Costa Rica Escuela de Ingeniería en Electrónica Master Thesis Evaluation Record

Master's thesis presented to the current Evaluation Committee as a requirement to qualify for the master's degree of the Instituto Tecnológico de Costa Rica

#### Evaluation Committee

Firmado por RONNY GIOVANNI GARCIA RAMIREZ (FIRMA) PERSONA FISICA, CPF-01-1137-0229. Fecha declarada: 11/02/2022 08:13 AM Esta representación visual no es fuente de confianza. Valide siempre la firma.

> Dr.-Ing Ronny García-Ramírez Reviewer

JUAN JOSE MONTERO RODRIGUEZ (FIRMA) 0600'

Dr.-Ing Juan Montero Rodríguez External Reviewer ALFONSO CHACON RODRIGUEZ (FIRMA) PERSONA FISICA, CPF-01-0702-0796. Fecha declarada: 11/02/2022 01:47:03 PM Razón: Doy fe Lugar: Cartago Contacto: alchacon@tec.ac.cr

Dr.-Ing Alfonso Chacón-Rodríguez Reviewer

JOHAN CARVAJAL Firmado digitalmente por JOHAN CARVAJAL GODINEZ (FIRMA) GODINEZ (FIRMA) -06'00'

Dr.-Ing Johan Carvajal-Godínez Master's Coordinator

RENATO RIMOLO Firmado digitalmente por RENATO RIMOLO DONADIO (FIRMA) DONADIO (FIRMA) Fecha: 2022.02.10 21:01:06 -06'00'

Dr.-Ing Renato Rímolo-Donadio Advisor

The members of this Evaluation Committee attest that the present Master's Thesis work has been approved and that fulfills the requirements set by Electronics Engineering School.

Cartago, September 1, 2021

### Declaration of authenticity

I herewith declare that I wrote this thesis on my own and did not use any unnamed sources or aid. Thus, to the best of my knowledge and belief, this thesis contains no material previously published or written by another person except where due reference is made by correct citation. This includes any thoughts taken over directly or indirectly from printed books and articles as well as all kinds of online material.

Javier Andrés Aparicio Morales Cartago, September 1, 2021 ID: 1-1575-0288

This work is licensed under a Creative Commons "Attribution-NonCommercial-ShareAlike 4.0 International" license.

# Abstract

In this work, the design and implementation of elastic buffers at pre-silicon level are addressed. The buffers are designed to be part of USB 2.0 and 3.0 transceivers. Based on a register-transfer level (RTL) description in Verilog and a digital design framework implemented in Synopsys, the design implementation and synthesis are performed using a XFAB 180-nm CMOS process design kit. A high-level simulation framework for USB transceivers was also developed, which allows the incorporation of the building blocks of transmitters and receivers at different abstraction levels, as well as different channel models in terms of S-Parameters.

Strategies for high-speed design, such as clock equalization, were applied to complete the design. Although the designs could be successfully characterized and simulated, only the 2.0 version could reach the specified speed. The 3.0 version can work up to a frequency of 3.8 GHz, but cannot reach the required speed due to process limitations.

Keywords: Digital Flow Synthesis, Elastic Buffer, Links, Timing, Transceiver, USB.

### Resumen

En este trabajo se aborda el diseño y la implementación de buffers elásticos a nivel de presilicio. Los buffers se diseñan para formar parte de transceptores USB 2.0 y 3.0. A partir de una descripción a nivel de transferencia de registros (RTL) en Verilog y un entorno de diseño digital implementado en Synopsys, se realiza la implementación del diseño y la síntesis utilizando un kit de diseño en proceso XFAB de 180 nm CMOS. También se desarrolló un entorno de simulación de alto nivel para transceptores USB, que permite incorporar los bloques construidos de transmisores y receptores a diferentes niveles de abstracción, así como diferentes modelos de canal en términos de parámetros S.

Para completar el diseño se aplicaron estrategias de diseño de alta velocidad, como la ecualización del reloj. Aunque los diseños pudieron caracterizarse y simularse con éxito, sólo la versión 2.0 pudo alcanzar la velocidad especificada. La versión 3.0 puede trabajar hasta una frecuencia de 3.8 GHz, pero no puede alcanzar la velocidad requerida debido a las limitaciones del proceso.

Palabras clave: Buffer Elástico, Enlaces, Flujo de Diseño Digital, Temporizado, Transceptor, USB. to my parents, sister and my dear Alexa

## Acknowledgment

First of all I want to thank God for allowing me to be with health, wisdom and understanding during this program. Next, I want to thank my parents Eliecer and Patricia, as well as my sister for always supporting me during this stage. I appreciate all the support they gave me during the internship. I thank Alexa, for always being with me, encouraging me at every moment.

I appreciate the ITCR for providing me with a scholarship to continue my university studies. I want to give a special thanks to Dr.-Ing Renato Rimolo-Donadio who gave me his confidence to carry out this project, besides being a guide during the realization of the project, where he always had time to attend me and correct me when necessary. I also appreciate the fact that he supported me to participate in the internship, which was a great learning experience, and I will always thank him for everything I have learned. Special thanks to Dr.-Ing Alfonso Chacón and Dr.-Ing Ronny García for being part of the evaluation committee. My gratitude with M.Sc. Sergio Arriola-Valverde for all the help that gave me and for always support me with his advices.

Special thanks to Gabriel Rodíguez who was someone I lived for a long time with and was always there to help in whatever was needed. I want to thak to the VLSI group (Luis, Bernardo, Felipe and Daniel) for all the experiences lived in the specialization courses, as well as outside of them. Finally, my thanks to the communications lab team (Andres, Jose and Sofia) who collaborated in the development of this project until the end.

Javier Aparicio Morales

Cartago, September, 2021

## Contents

| 1        | Intr | oducti  | on                                      | 1  |

|----------|------|---------|-----------------------------------------|----|

| <b>2</b> | Elas | stic Bu | ffer Architectures                      | 3  |

|          | 2.1  | Elastic | Buffers                                 | 3  |

|          |      | 2.1.1   | Synchronous Elastic Buffers             | 5  |

|          |      | 2.1.2   | Asynchronous Elastic Buffers            | 9  |

|          | 2.2  | Compa   | arison of distinct elastic buffers      | 10 |

|          | 2.3  | Summa   | ary                                     | 11 |

| 3        | Frai | meworl  | k Simulation of USB Transceivers        | 12 |

|          | 3.1  | Frame   | work Simulation for USB Transceivers    | 12 |

|          | 3.2  | Transn  | nitters for USB 3.0                     | 14 |

|          |      | 3.2.1   | Scramblers                              | 14 |

|          |      | 3.2.2   | 8b/10b Encoders                         | 15 |

|          |      | 3.2.3   | Serializers                             | 16 |

|          |      | 3.2.4   | Transmitter Differential Drivers        | 17 |

|          | 3.3  | Interco | onnect for USB 3.0 and 2.0 Transceivers | 21 |

|          | 3.4  | Receiv  | er of USB 3.0 Transceivers              | 22 |

|          |      | 3.4.1   | Receiver Differential Drivers           | 23 |

|          |      | 3.4.2   | Clock and Data Recoverys (CDR)          | 26 |

|          |      | 3.4.3   | Deserializers                           | 27 |

|          |      | 3.4.4   | K28.5 Detectors                         | 28 |

|          |      | 3.4.5   | Elastic Buffers                         | 28 |

|   |      | 3.4.6   | 8b/10b Decoders                              | 28 |

|---|------|---------|----------------------------------------------|----|

|   |      | 3.4.7   | Descramblers                                 | 29 |

|   | 3.5  | Transı  | mitter of USB 2.0 Transceivers               | 30 |

|   |      | 3.5.1   | Transmitter Control FSM                      | 30 |

|   |      | 3.5.2   | Sync Generators                              | 32 |

|   |      | 3.5.3   | EOP Generators                               | 33 |

|   |      | 3.5.4   | Serializers                                  | 33 |

|   |      | 3.5.5   | Bit Stuffers                                 | 34 |

|   |      | 3.5.6   | NRZI Encoders                                | 34 |

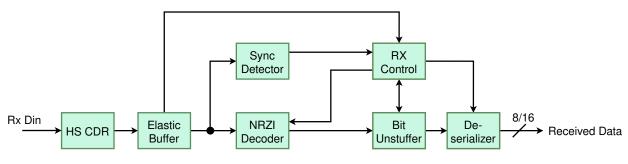

|   | 3.6  | Receiv  | ver of USB 2.0 Transceivers                  | 36 |

|   |      | 3.6.1   | High-Speed Clock and Data Recoverys (HS CDR) | 36 |

|   |      | 3.6.2   | Elastic Buffers                              | 37 |

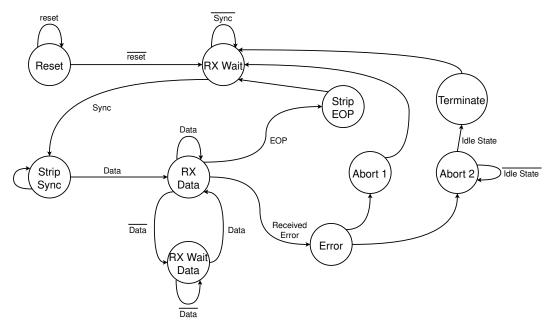

|   |      | 3.6.3   | Receiver Control FSMs                        | 37 |

|   |      | 3.6.4   | Sync Detectors                               | 38 |

|   |      | 3.6.5   | NRZI Decoders                                | 39 |

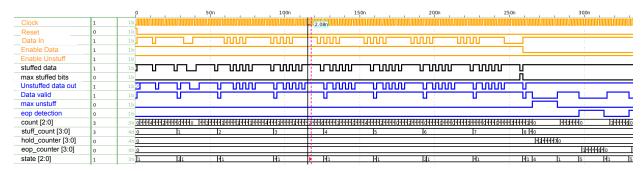

|   |      | 3.6.6   | Bit Unstuffers                               | 39 |

|   |      | 3.6.7   | Deserializers                                | 41 |

| 4 | Elas | stic Bu | ıffer Design                                 | 42 |

| 1 |      |         |                                              |    |

|   | 4.1  | Model   | ing and Requirements for the Elastic Buffer  | 42 |

|   |      | 4.1.1   | USB 3.0 Standard                             | 42 |

|   |      | 4.1.2   | USB 2.0 Standard                             | 49 |

|   | 4.2  | Digita  | l Flow Synthesis                             | 55 |

|   |      | 4.2.1   | Front-End                                    | 56 |

|          |     | 4.2.2 Back-End                                          | 57 |

|----------|-----|---------------------------------------------------------|----|

|          | 4.3 | Simulation Results                                      | 58 |

| <b>5</b> | Tra | nsceiver Link Simulation with Design of Elastic Buffers | 67 |

|          | 5.1 | USB 3.0 Transceivers                                    | 67 |

|          | 5.2 | USB 2.0 Transceivers                                    | 76 |

| 6        | Cor | clusions and Recommendations                            | 80 |

# List of Figures

| 1.1  | Simplified process steps for the design of a digital IC block using a top-down approach          | 1  |

|------|--------------------------------------------------------------------------------------------------|----|

| 2.1  | Simplified block diagrams for USB transceivers                                                   | 4  |

| 2.2  | Block diagram and trade-offs of elastic buffer architectures                                     | 5  |

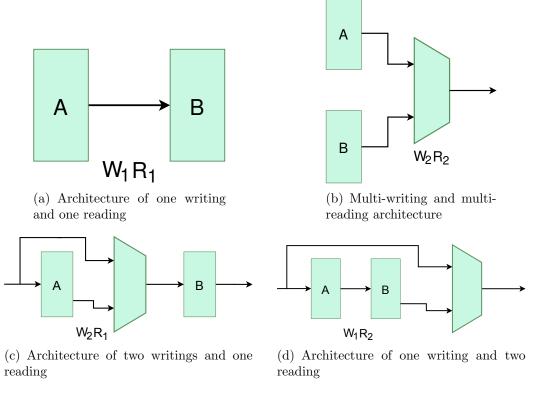

| 2.3  | Elastic buffer data flow architectures. Adapted from [14]                                        | 7  |

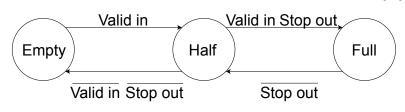

| 2.4  | State diagram of the EB control unit. Adapted from [18]                                          | 7  |

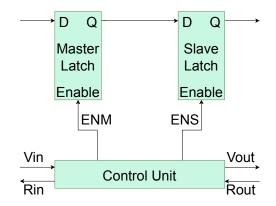

| 2.5  | Topology of the EB master-slave flip-flop. Adapted from [19]                                     | 8  |

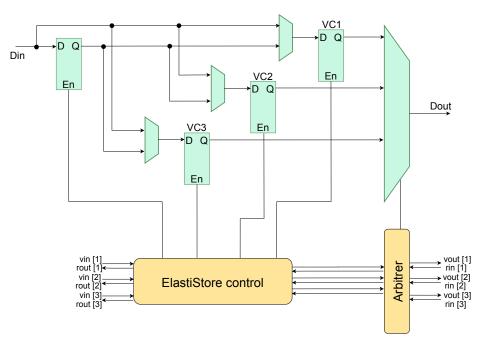

| 2.6  | Elastistore architecture. Adapted from [18]                                                      | 8  |

| 2.7  | EB block diagram for a USB 3.0 implementation. Adapted from $[21]$                               | 10 |

| 3.1  | Framework for simulation of USB transceivers                                                     | 13 |

| 3.2  | USB 3.0 transmitter simplified block diagram                                                     | 14 |

| 3.3  | Scrambler block diagram description event-driven simulation of its behavioral AMS model          | 15 |

| 3.4  | 8b/10b encoder block diagram description and event-driven simulation of its behavioral AMS model | 16 |

| 3.5  | Serializer block diagram and event-driven simulation of its behavioral AMS model                 | 17 |

| 3.6  | Transmitter differential driver simplified block diagram                                         | 18 |

| 3.7  | FFE block diagram description and simulation of its behavioral AMS model                         | 19 |

| 3.8  | LVDS circuit description and event-driven simulation of its behavioral AMS model                 | 20 |

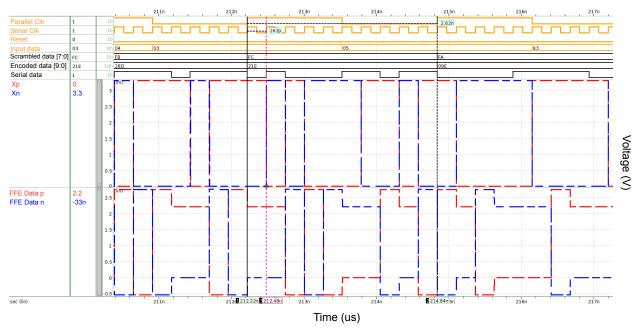

| 3.9  | Interconnect description and simulation at mixed-signal level                                    | 21 |

| 3.10 | USB 3.0 receiver simplified block diagram                                                        | 22 |

| 3.11 | Receiver differential driver block diagram                                                       | 23 |

| 3.12 | CTLE circuit representation. Adapted from [45]                                                   | 23 |

| 3.13 | Receiver driver implementation at behavioral AMS level                                            | 25 |

|------|---------------------------------------------------------------------------------------------------|----|

| 3.14 | Simplified operation and block diagram of the CDR                                                 | 26 |

| 3.15 | Deserializer circuit description and event-driven simulation of its behavioral AMS model          | 28 |

| 3.16 | Clock domains representation of USB transceiver                                                   | 29 |

| 3.17 | 8b/10b decoder description and event-driven simulation of its behavioral AMS model                | 29 |

| 3.18 | Descrambler event-driven simulation of its behavioral AMS model at 500 $\rm MHz$                  | 30 |

| 3.19 | USB 2.0 transmitter simplified block diagram                                                      | 30 |

| 3.20 | Transmitter control FSM state diagram description and implementation at behavioral level          | 32 |

| 3.21 | Sync generator simulation results at 480 MHz                                                      | 32 |

| 3.22 | EOP generator simulation results at 480 MHz                                                       | 33 |

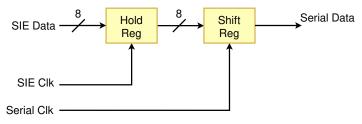

| 3.23 | Serializer block diagram description and event-driven simulation of its behavioral AMS model      | 34 |

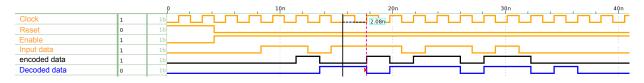

| 3.24 | Bit stuffer flow diagram description and event-driven simulation of its behav-<br>ioral AMS model | 35 |

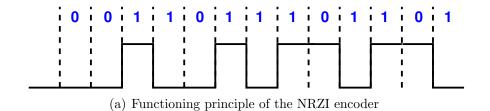

| 3.25 | NRZI encoder description and event-driven simulation of its behavioral AMS model                  | 36 |

| 3.26 | USB 2.0 receiver simplified block diagram                                                         | 36 |

| 3.27 | Receiver control FSM state diagram description and implementation at be-<br>havioral level        | 38 |

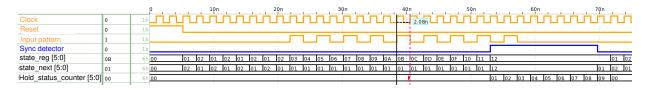

| 3.28 | Sync detector simulation results at 480 MHz                                                       | 39 |

| 3.29 | NRZI encoder simulation results at 480 MHz                                                        | 39 |

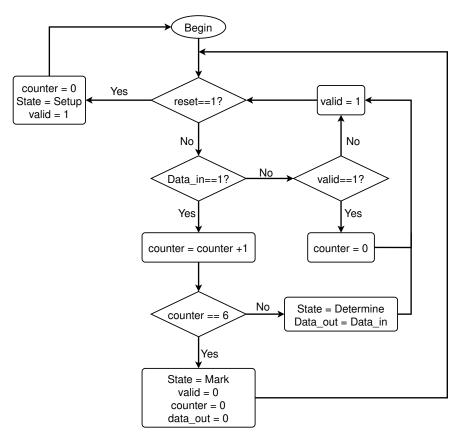

| 3.30 | Bit unstuffer flow diagram description and implementation at behavioral level                     | 40 |

| 3.31 | Deserializer simulation results at 60 MHz                                                         | 41 |

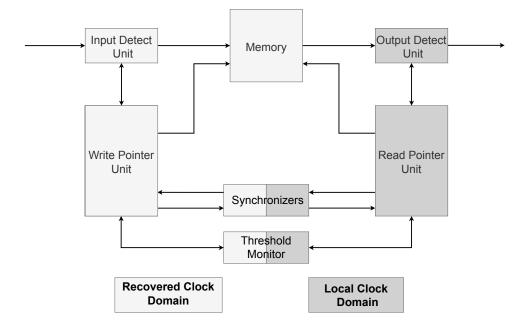

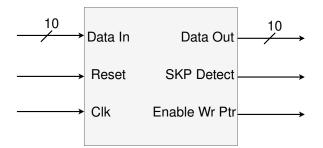

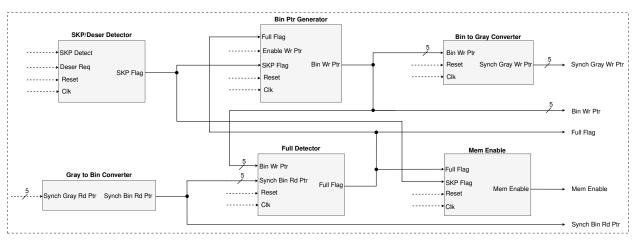

| 4.1  | Simplified block diagram of Elastic Buffer for USB 3.0                                            | 43 |

| 4.2  | Block diagram of the Input Detect Unit of the Elastic Buffer for USB 3.0 $$ .       | 44 |

|------|-------------------------------------------------------------------------------------|----|

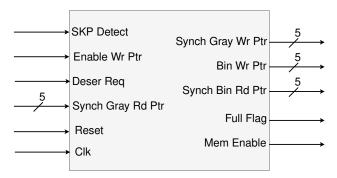

| 4.3  | Write Pointer Generator of the Elastic Buffer for USB 3.0                           | 45 |

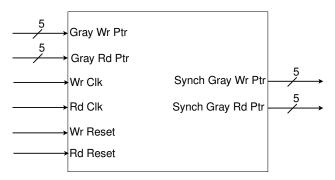

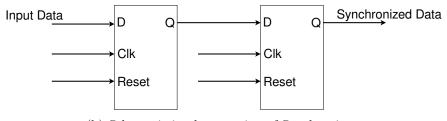

| 4.4  | Synchronizers of the Elastic Buffer for USB 3.0                                     | 46 |

| 4.5  | Block diagram of the Threshold Monitor Unit of the Elastic Buffer for USB 3.0       | 47 |

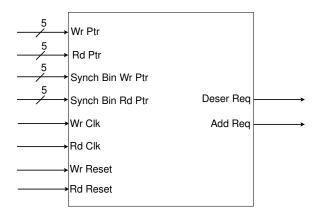

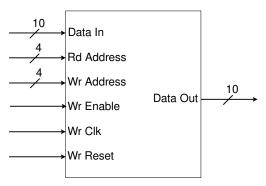

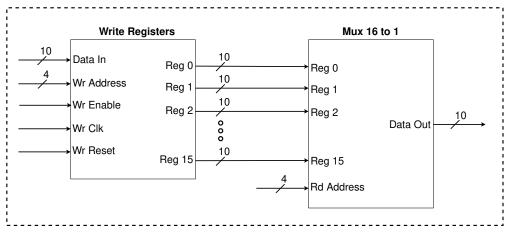

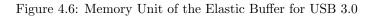

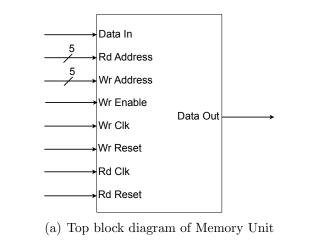

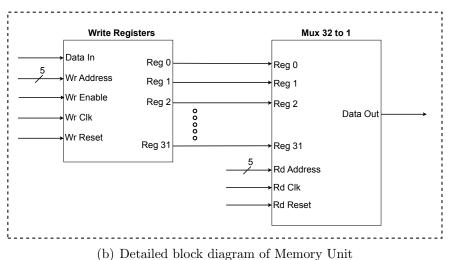

| 4.6  | Memory Unit of the Elastic Buffer for USB 3.0                                       | 48 |

| 4.7  | Read Pointer Generator of the Elastic Buffer for USB 3.0                            | 48 |

| 4.8  | Block diagram of the Output Detect Unit of the Elastic Buffer for USB 3.0 $$ .      | 49 |

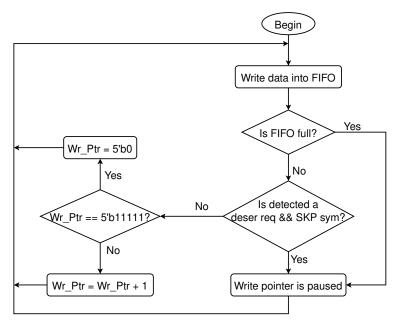

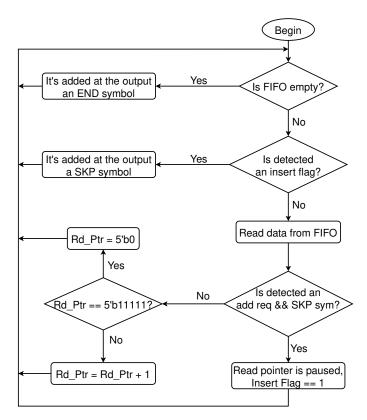

| 4.9  | Flow diagram for the addition operation                                             | 50 |

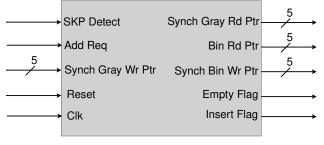

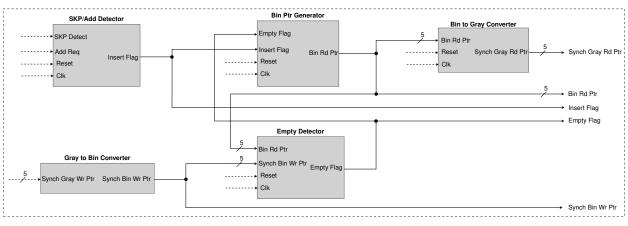

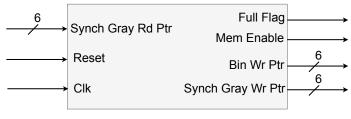

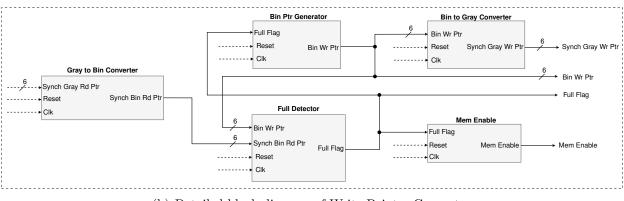

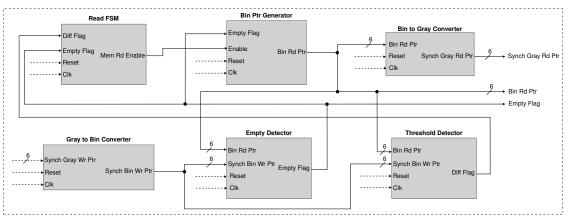

| 4.10 | Simplified block diagram of Elastic Buffer for USB 2.0                              | 51 |

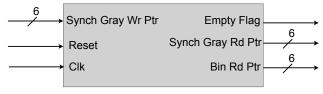

| 4.11 | Write Pointer Generator of the Elastic Buffer for USB 2.0                           | 52 |

| 4.12 | Simplified block diagram of Synchronizers for USB 2.0                               | 52 |

| 4.13 | Memory Unit of the Elastic Buffer for USB 2.0                                       | 53 |

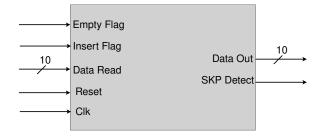

| 4.14 | Read Pointer Generator of the Elastic Buffer for USB 2.0                            | 54 |

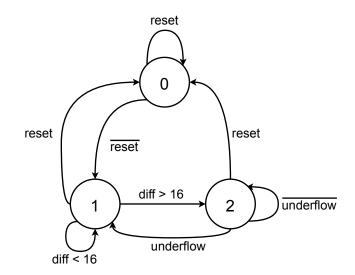

| 4.15 | FSM state diagram for reading operation for USB 2.0                                 | 54 |

| 4.16 | Flow diagram for a digital flow synthesis                                           | 55 |

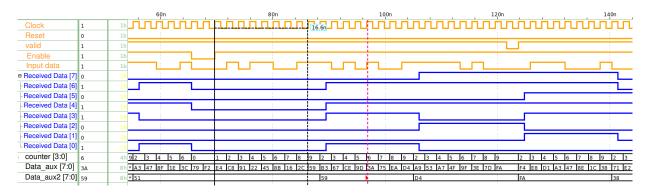

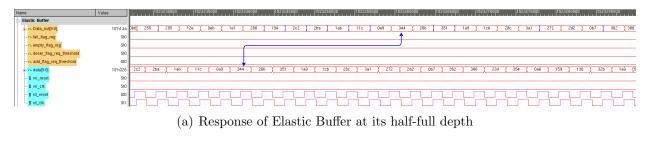

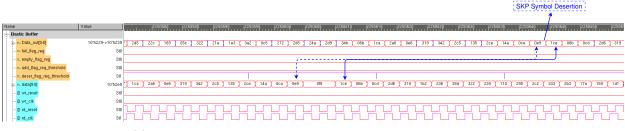

| 4.17 | Simulation results of Elastic Buffer for USB 3.0 standard                           | 59 |

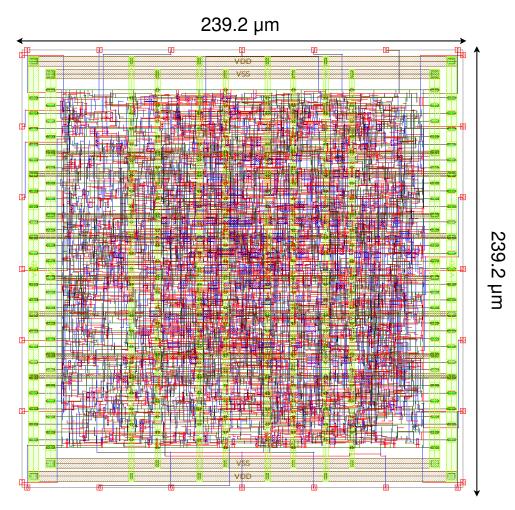

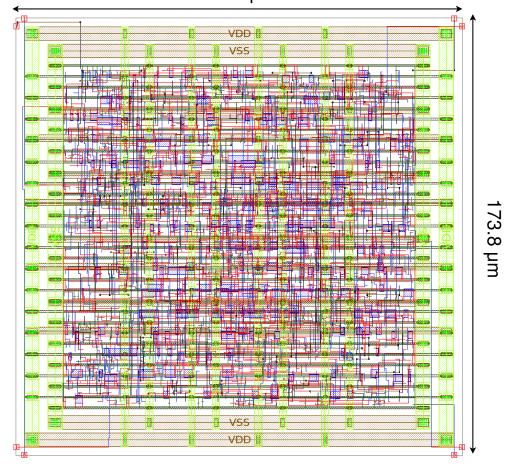

| 4.18 | Layout of the Elastic Buffer for the USB 3.0 standard                               | 60 |

| 4.19 | Timing report of critical path of the Elastic Buffer for the USB 3.0 standard       | 62 |

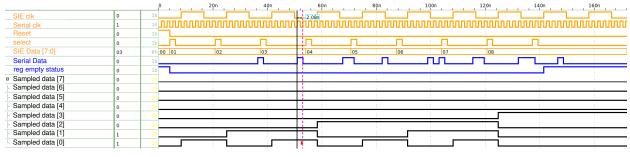

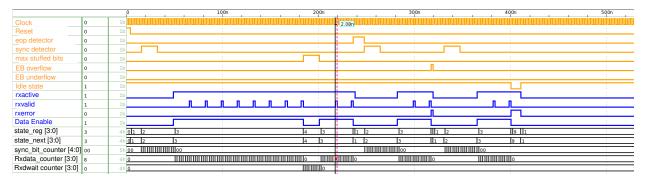

| 4.20 | Simulation results of Elastic Buffer for USB 2.0 standard                           | 63 |

| 4.21 | Layout of the Elastic Buffer for the USB 2.0 standard                               | 64 |

| 5.1  | USB transceiver validation framework for the 3.0 standard $\ldots$                  | 68 |

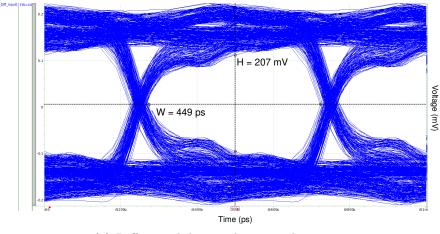

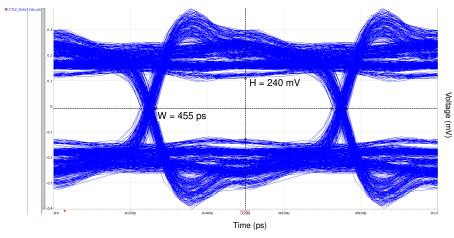

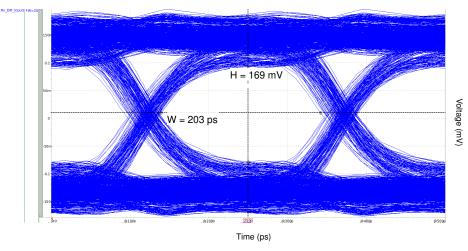

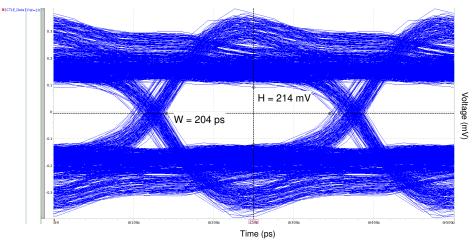

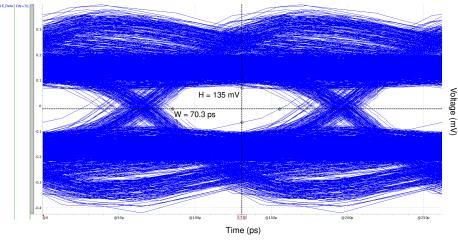

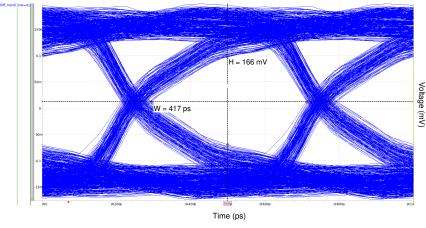

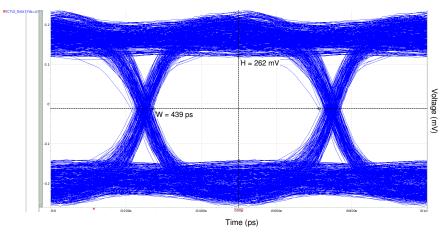

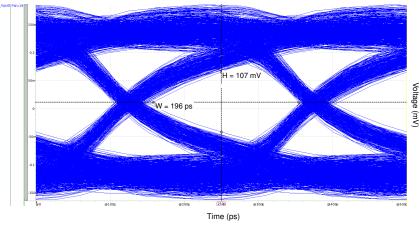

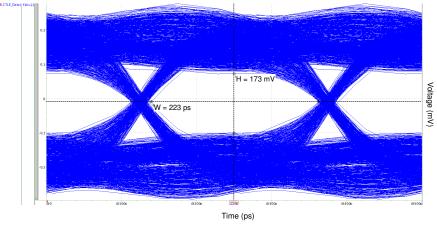

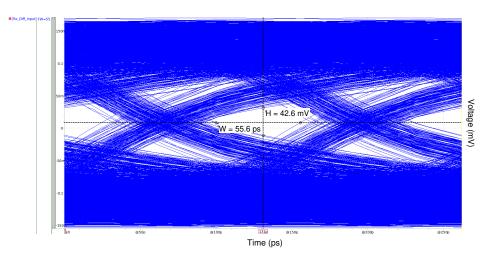

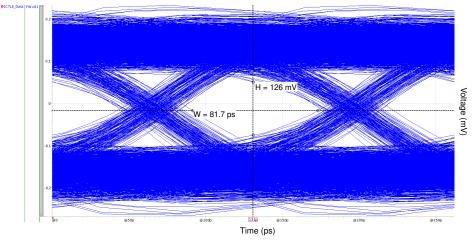

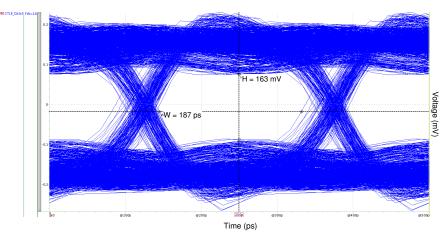

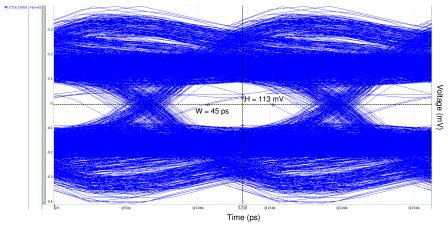

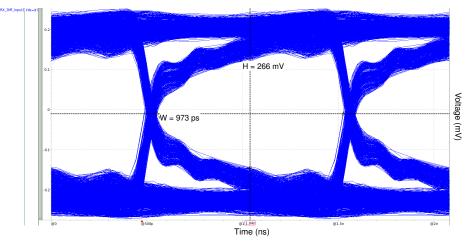

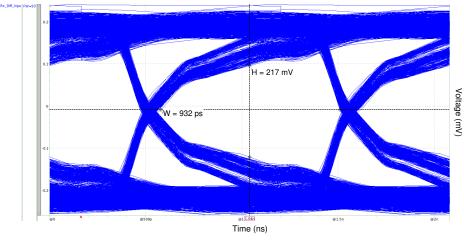

| 5.2  | Eye-Diagrams comparison at the input receiver stage at 1 Gbps and 1 meter of length | 70 |

| 5.3  | Eye-Diagrams comparison at the input receiver stage at 2 Gbps and 1 meter of length | 71 |

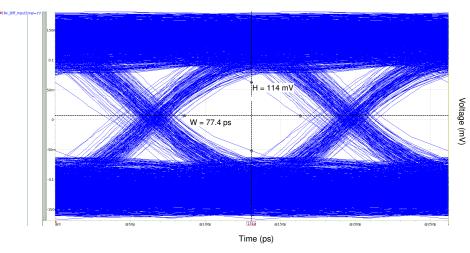

| 5.4  | Eye-Diagrams comparison at the input receiver stage at 3.81 Gbps and 1 meter of length                                     | 72 |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

| 5.5  | Eye-Diagrams comparison at the input receiver stage at 1 Gbps and 2 meters of length                                       | 73 |

| 5.6  | Eye-Diagrams comparison at the input receiver stage at 2 Gbps and 2 meters of length                                       | 73 |

| 5.7  | Eye-Diagrams comparison at the input receiver stage at 3.81 Gbps and 2 meters of length                                    | 74 |

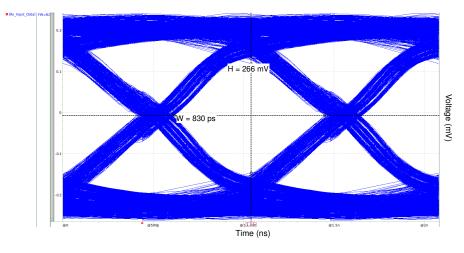

| 5.8  | Eye-Diagrams comparison at the input receiver stage at different data rates<br>and 1 meter of length with CTLE enhancement | 75 |

| 5.9  | USB transceiver validation framework for the 2.0 standard $\ldots$                                                         | 77 |

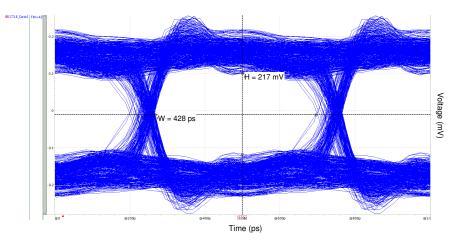

| 5.10 | Eye-Diagrams comparison at the input receiver stage at 480 Mbps with several lengths                                       | 79 |

| 5.11 | Eye-Diagram comparison at the input receiver stage 480 Mbps and 1 meter of length with error insertion                     | 79 |

## List of Tables

| 2.1 | Variable comparison between different implementations of elastic buffers $\ . \ .$ | 10 |

|-----|------------------------------------------------------------------------------------|----|

| 3.1 | CTLE values of their transfer function                                             | 24 |

| 4.1 | Timing constraints for the Elastic Buffer                                          | 56 |

| 4.2 | Comparison results of Elastic Buffer for USB 3.0 standard                          | 61 |

| 4.3 | PVT typical scenario of Elastic Buffer for USB 3.0 standard                        | 61 |

| 4.4 | PVT fast scenario of Elastic Buffer for USB 3.0 standard                           | 62 |

| 4.5 | PVT slow scenario of Elastic Buffer for USB 3.0 standard                           | 63 |

| 4.6 | Results of Elastic Buffer for USB 2.0 standard                                     | 65 |

| 4.7 | PVT typical scenario of Elastic Buffer for USB 2.0 standard                        | 65 |

| 4.8 | PVT fast scenario of Elastic Buffer for USB 2.0 standard                           | 65 |

| 4.9 | PVT slow scenario of Elastic Buffer for USB 2.0 standard                           | 66 |

### 1 Introduction

Nowadays, *Medical Devices* (MD) have gain attention in the last years due to its capabilities for disease detection, monitoring, and control. A medical device is a machine, gadget, or implantable to be used on humans for medical purposes [1, 2, 3]. Recently, the Integrated Circuit Design Laboratory (DCI Lab) of the Electronics Engineering Department at the Instituto Tecnologico de Costa Rica has been working on the development of integrated circuits (IC) for Implantable Medical Devices (IMD). Last year, a RISC-V based microprocessor tailored for IMD applications was tapped out and validated [4, 5], targeting its first application as part of a cardiac stimulation prototype [6].

Since the proper interfaces with external devices and compatibility with well established standards is mandatory for modern IMD solutions, next generations of this microcontroller IP require to extended the supported communications interfaces. An ubiquitous interface is the universal serial bus (USB), which reaches speeds in the multi-gigabit range for its latest specifications [7]. This work is a contribution to the initiative of creating a propietary USB transceiver IP block for its incorporation of custom IC designs developed by the DCI Lab.

In particular, this works deals with the design and implementation of an important building block of the receiver: the elastic buffer. It is in charge of handling slight timing differences between the input received stream clock domain and the one of the internal receiver circuitry.

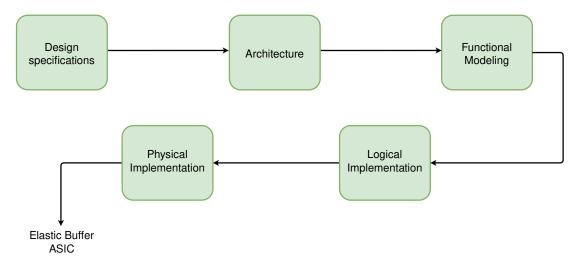

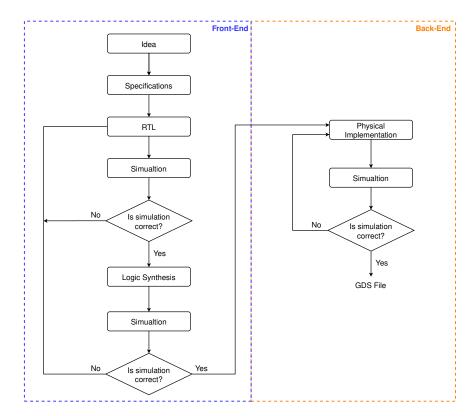

The development of buffers that can work below the standards 2.0 and 3.0 is addressed, using a top-down digital IC design flow, depicted in figure 1.1. The first block is related to the definition of the specifications of the elastic buffer, such as the operating frequency, power, size, buffer depth. Then, the architecture that is used for the elastic buffer is chosen, and then a functional model at high-level description is proposed and it is implemented up

Figure 1.1: Simplified process steps for the design of a digital IC block using a top-down approach

to a pre-silicon level through the logical and physical synthesis design flows.

The design of custom elastic buffers were implemented on a 180-nm CMOS process; to achieve this, first, possible architectural solutions were explored in order to define the specifications and high-level design of the buffers. Then, the designs were implemented at RTL level, for the standard USB 2.0 and 3.0, following a top-down digital design flow with the Synopsys IC framework. The physical design was also proposed and validated with post-layout annotations and simulations.

A USB transceiver simulation framework is also proposed in this work, which allows to consider the other functional blocks and channel models for pre-silicon validation purposes. For ensuring the operation of the transceiver, a behavioral view was used for other blocks than the elastic buffer, for which a detailed implementation was not yet available.

This work is organized as follows: in chapter 2 the literature related to elastic buffer architectures is reviewed. In chapter 3, the high-level simulation framework for USB 3.0 and 2.0 transceivers is presented. The design and implementation of the elastic buffers, from their specifications up to the pre-silicon level, are gathered in chapter 4, where results merely for the elastic buffer implementations were considered. Then, serial transceivers simulations through mixed-signal with the design of elastic buffer are carried out in chapter 5, and, finally, conclusions and recommendations are presented in chapter 6.

### 2 Elastic Buffer Architectures

This chapter contains a literature review related to implementations of elastic buffers at integrated circuit level. Two types of elastic buffers are mentioned, namely synchronous and asynchronous, and their differences are discussed. Implementations based on the USB standard are also included. Finally, a comparison of different types of elastic buffers found in the literature is presented, which is used to select the most suitable architecture considering the constraints associated with the selected process and standard constraints.

#### 2.1. Elastic Buffers

The scope of this work is focused on the implementation of elastic buffers, using a serial transceiver based on an industrial standard. Such standards are the USB with its 3.0 and 2.0 versions. The reasons for using a serial path instead of a parallel one are the complexity and cost of the IC and packaging. Additionally, signal and power integrity are compromised as data rates increase. Increasing the number of lines in the circuits, along with a shrinking transistor channel length, make the proper functioning of an electronic system a challenge.

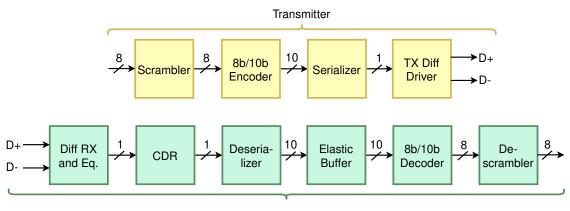

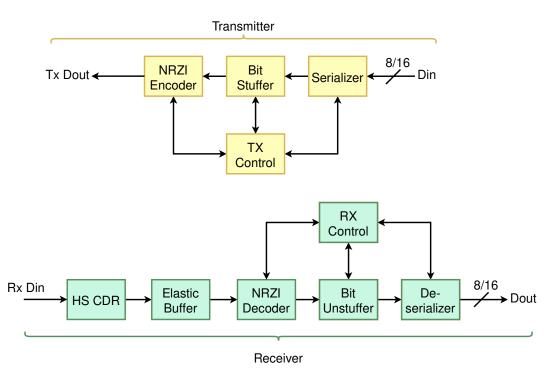

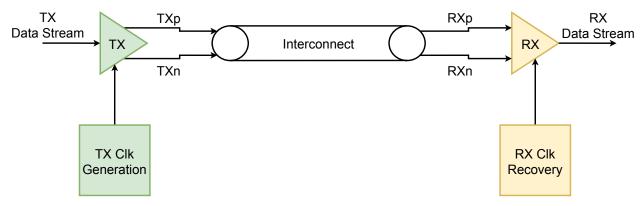

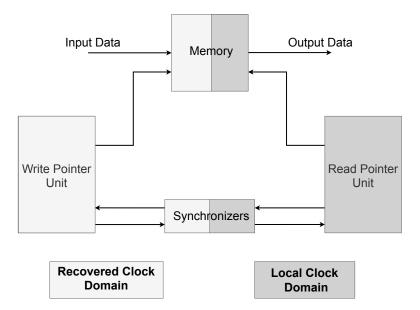

Typical serial transceivers at a simplified block diagram level are shown in figure 2.1 [8, 9], where the yellow blocks correspond to the transmitter and the green blocks to the receiver. Both stages of the aforementioned figure are not directly connected, an interconnect is presented between the stages, which is responsible for carrying the signals from one place to another. Moreover, this interconnect adds losses such as reflections, crosstalk, attenuation, and dispersion to the transmitted signals that might be harmful.

Synchronization in digital systems is vital to their operation and for ensuring it, the clock signal must be the same in both stages of the transceiver. The synchronization of the serial link relies on the clock signal that is sent along with the information that flows through the

Receiver

(a) Simplified block diagram of a serial transceiver for USB 3.0 standard. Adapted from [8]

(b) Simplified block diagram of a serial transceiver for USB 2.0 standard. Adapted from [9]

Figure 2.1: Simplified block diagrams for USB transceivers

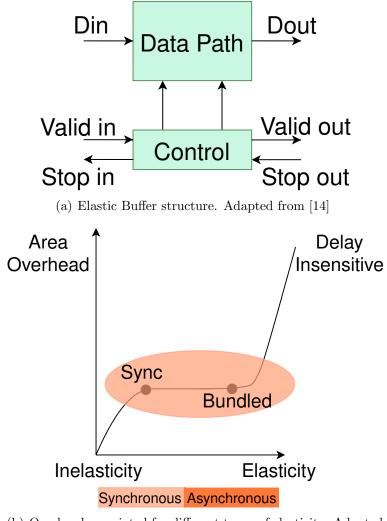

USB link and the stage in charge of this task is the *Clock and Data Recovery (CDR)* block at the receiver stage. Since the clock signal is recovered by the CDR, variations in the data might be introduced because the same clock of the transmitter stage is not being used and hence, the system must be capable of tolerating such variations. There will be occasions when the recovered clock will be faster or slower than the reference signal of the receiver stage, therefore, the block that can tolerate such variations is the elastic buffer. The EB may operate with handshaking protocols or the addition of special symbols, which add delays in the data flow without changing the original content sent from the transmitter [10, 11]. The goal of the elastic buffer is to provide synchronization in the serial link with a local clock domain at the receiver, along with the clock from the received data [12]. Additionally, the advantages offered by the elastic buffer are the reduction in area, power, and delays [13], whose variables are analyzed in this chapter for different architectures of elastic buffers.

The main idea of the elastic buffer is shown in figure 2.2 (a), which includes the control unit and data path blocks as well as the control signals. Either by handshaking protocol or by the use of special symbols, it is able to control the data flow that passes through the serial link [14, 15]. A trade-off is present in the use of elastic buffer, depicted in figure 2.2 (b), since there is a compromise between elasticity and area overhead for different types of circuits. While more elasticity is achieved, the area overhead at a certain moment will increase tremendously. Nevertheless, a certain degree of elasticity can be achieved without a high penalty cost in terms of area. The main difference between the different types of EBs is the control unit and the clock domain they use, because the topology used for the data path, essentially is the same in both types of EBs [16].

(b) Overhead associated for different types of elasticity. Adapted from [16]

Figure 2.2: Block diagram and trade-offs of elastic buffer architectures

#### 2.1.1. Synchronous Elastic Buffers

A synchronous EB can be implemented with master-slave flip-flops for the data path block and a control unit. The two latches that conform the flip-flop, use different enable signals that are given by the control unit. Depending on the status of each latch detected by the control unit, a valid or invalid signal of whether or not to allow the flow of information will be sent. This type of EB uses the same clock signal in the system, where an approach in [14] is with AND and NOT gate arrays, which handle the control unit. These arrays are used to activate the invalid signal, indicating the stopping of the input data, because the current data that is being processed, have not passed completely through the master-slave flip flop that models the data path block of the figure 2.2 (a). If the control signal is valid, the stream of information will be continued without any problem.

The control signals can be classified into three states for an EB. The first one is the *Transfer* state and this occurs when the receiver, which is the second latch of the flip-flop accepts data from the transmitter (the first latch of the flip-flop). The second one is the *Inactive* state and this occurs when the transmitter is not sending any data. The last state is *Retry* state, which happens when the receiver is not able to accept the data and the transmitter is trying to send new data [14].

The elastic buffer seeks to reduce latency to a minimum and for ensuring the previous premise, the latency of the sending signal  $L_f$ , which is the valid signal, and the response signal  $L_b$ , which is the stop signal. Latency must have a value greater than zero; however, this value cannot be high since this would decrease the frequency response of the system. Therefore, the latency value of each signal mentioned must at least be one [14] and this is shown in the equation (1).

$$L_f = L_b = 1 \tag{1}$$

With the previously mentioned, the number of data that the elastic buffer can handle is the sum of both latencies. This entails that the minimum capacity of the EB to operate, based on the equation (1) is 2. Several implementations of elastic buffers are described in figure 2.3, where each one allows several writings and readings that can be performed in the EB [14]. Figure 2.3 shows the different possible combinations: (a), one write and one read, (b)two writes and two reads, (c) two writes and one read, and (d) one write and two reads. The writings and readings for the indicated architectures, are performed through muxes and buffers in first instance. The independent handling of each buffer or latch is achieved with the control signals and handshaking protocol. It is possible to obtain less power consumption, area and latency by using latches to capture each data instead of flip-flops [14].

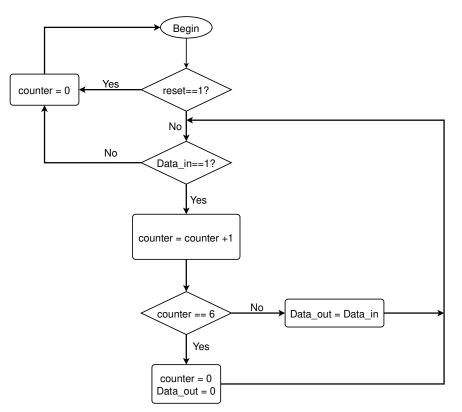

The operation of the data path is addressed by a control unit where *Finite State Machine* (FSM) controls the information flow through the signals generated by handshaking. The control is composed by three states, the first one corresponds to an empty state, the second one corresponds to a medium state and the last one is the complete state. The empty state indicates that no valid data was captured in the data path. In the medium state, the output latch holds the valid data, while the full state indicates that both latches have valid data, which causes the control unit to stop sending data for processing the current data. The state diagram is shown in figure 2.4, where an equivalent circuit of this diagram can be obtained with OR, AND and NOT gates [17, 18]. The preceding description assumes the minimum latency case that is 2, therefore, this indicates that two latches are used to represent latency.

In [19, 20], the data path block is modeled by a master-slave flip-flop and this is depicted

Figure 2.3: Elastic buffer data flow architectures. Adapted from [14]

Figure 2.4: State diagram of the EB control unit. Adapted from [18]

in the figure 2.5, where each latch has different enablers coming from the control unit, to allow the transfer of information. The minimum implementation of the EB latency has been shown in this chapter, which corresponds to two and simultaneously corresponds to the same number of latches used for the data flow. Nevertheless, the number of latches can be increased to get a greater data width, which for the USB 3.0 standard would correspond to 10 bits and for the USB 2.0 standard to one bit. The reviewed authors mention that for the implementation at the physical level, the routing of the EB wires must be optimal, for reducing the overhead that the FSM and the latches could add to the system. Increasing the width of the wires and using repeaters to reduce delays are manners to reduce the overhead [20].

Figure 2.5: Topology of the EB master-slave flip-flop. Adapted from [19]

Among the most typical applications where the elastic buffers are used, there is the *Network on Chip* (NoC). The elasticity that the EB provides is very useful for the interconnection of different NoCs. Since there are many virtual channels in NoCs, a proposal of *Elastistore* is mentioned in [18], where the addition of latches and muxes for each virtual channel are proposed. These channels at the end are managed by an arbiter that is a larger control unit than the conventional EB control that is called *Elastistore Control*. For the generation of the final data output, a mux is used where all the outputs of the virtual channels are connected. In figure 2.6, the Elastistore architecture is described, where each virtual channel uses a latch and a mux. The state machine of this architecture is based on the same principle as the state machine previously described for the EB; therefore, the EB allows the integration of functions for many applications and thus reducing the complexity of the system.

Figure 2.6: Elastistore architecture. Adapted from [18]

#### 2.1.2. Asynchronous Elastic Buffers

Asynchronous elastic buffers can be classified in two groups, which are the four-phase and two-phase approaches. The four-phase protocol is based on handshaking signals, where positive and negative edges of the request and acknowledgment signals are expected. The four-phase implementation is also known as a return-to-zero event, due to the negative edges of the control signals. Its operation is based on the enable signal of the first latch coming from the control unit. The positive edge of the enable signal is presented with the data transfer completion with the next latch; in other words, the negative edge of acknowledge signal and the remaining latches will follow the behavior of the first handshaking when the word width is larger than two bits. Considerations such as the non-overlapping clock for transparent latches should be taken into account, which indicates that the transmission cannot occur simultaneously [16].

The two-phase family has no semantic difference between the positive or negative edges of the signal. A latch called *Capture-Pass* is used in this family. The events in the capture and pass of signals are alternated to allow the latch to capture and pass information alternatively [16]. The capture and pass signals are delays that indicate the capture and pass operations. There are compromises between the two families presented. The two-phase family might present a lower power consumption and achieve higher performance because it avoids a return to zero events. Nevertheless, the two-phase family is more complex to design in terms of logic than the four-phase family.

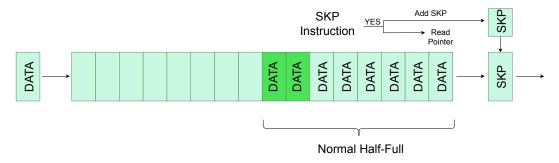

In [21], an elastic buffer architecture is proposed for the USB 3.0 serial standard. The use of special symbols that are 10-bit data is used for this standard. The *SKP* symbol allows it to be used in the information flow depending on the difference presented between the local domain clock and the clock recovered from the incoming data. If the recovered clock is faster than the local clock, redundant data should be removed or new data added to the buffer should be avoided because more data is being handled than allowed. The opposite happens when the local clock is faster than the retrieved clock, where the SKP signal must be added to the buffer to compensate for the lack of data. For USB, a based of 16 slots is used where each slot has a width of 10 bits and it is sought that half of these slots are always in use. This type of implementation reduces the complexity of the EB, because the handshaking protocol is not the main source of control of the EB, rather the difference between clocks and buffer occupation. The SKP symbol alleviates the EB design because when a difference between clocks exists, the symbol will act depending on the difference obtained. The block diagram that exemplifies the described above, is shown in figure 2.7.

Figure 2.7: EB block diagram for a USB 3.0 implementation. Adapted from [21]

#### 2.2. Comparison of distinct elastic buffers

Table 2.1 shows a comparison of different implementations found in the literature, based on most relevant metrics that characterize the performance of elastic buffers. Only one work is implemented in FPGA, while the remaining works are implemented at CMOS level with technology-node variations from 32 nm up to 180 nm. The clock that the elastic buffer uses to operate varies from 10 MHz up to 7.1 GHz; it is observed that as the process decreases, a higher operating frequency can be achieved.

Table 2.1: Variable comparison between different implementations of elastic buffers

| Work | Architecture                            | Tech   | Clock               | Cells | Area                | Delay     | Power            | Width   |

|------|-----------------------------------------|--------|---------------------|-------|---------------------|-----------|------------------|---------|

| [20] | Synchronous EB for routing NoCs         | 65nm   | 2 GHz               | 4143  | $14730 \ \mu m^2$   | 2.7  ns   | 0.12 mW          | 64 bits |

| [22] | Synchronous EB for routing NoCs         | 45nm   | 2 GHz               | 5691  | $15080 \ \mu m^2$   | 1.8 ns    | NA               | 64 bits |

| [18] | Synchronous EB for routing NoCs         | 40nm   | NA                  | NA    | $62000 \ \mu m^2$   | 2 ns      | NA               | 64 bits |

| [19] | Synchronous EB for routing NoCs         | 45  nm | NA                  | NA    | $17000 \ \mu m^2$   | 3.6 ns    | 2.6 mW           | 64 bits |

| [23] | Synchronous EB for routing NoCs         | 45  nm | NA                  | NA    | $52000 \ \mu m^2$   | 1.8 ns    | 38 mW            | 64 bits |

| [24] | Synchronous EB for routing NoCs         | 45  nm | 1.1 GHz             | NA    | $3070 \ \mu m^2$    | 0.91 ns   | 330 mW           | 64 bits |

| [25] | Synchronous EB for routing NoCs         | 90 nm  | 10 MHz              | NA    | $33.8636 \ \mu m^2$ | NA        | $653.14 \ \mu W$ | 24      |

| [26] | Synchronous EB                          | 45nm   | 500  MHz            | NA    | $1099 \ \mu m^2$    | NA        | 452.13 nW/MHz    | 64 bits |

| [17] | Synchronous EB for FIR filter           | 180 nm | $216 \mathrm{~MHz}$ | 7821  | NA                  | NA        | 78 mW-ns         | 16 bits |

| [27] | Synchronous EB in FPGA implementation   | NA     | 890  MHz            | 52    | NA                  | 1.123  ns | 3473.83 mW       | 8 bits  |

| [28] | Synchronous EB under process variation  | 32 nm  | 7.1 GHz             | NA    | 960 $\mu m^2$       | 0.538     | $542 \ \mu W$    | NA      |

| [21] | Asynchronous EB for USB 3.0 application | 65  nm | 500  MHz            | NA    | $11290 \ \mu m^2$   | 0.218  ns | 4.164 mW         | 10 bits |

| [29] | Asynchronous EB for USB 3.1 application | 180 nm | $318 \mathrm{~MHz}$ | 1279  | $33027 \ \mu m^2$   | NA        | 22.102  mW       | 32 bits |

It should be noted that the evaluation of the elastic buffer topology by itself is not performed in all the mentioned works in table 2.1. For instance, the elastic buffer allows the handling of many routers in a network-on-chip, therefore the evaluation of the NoC system is reported instead of the performance of the elastic buffer only. The delay shown in the above table is quite similar for all works, regardless of whether they operate at high or low frequency. In terms of power, there are variations from 542  $\mu W$  up to the order of mW. The word width is an important parameter because if it is larger, this implies a more complex logic in the data path to pass the data to the output.

#### 2.3. Summary

Overall, the main advantage that the elastic buffer offers is the is vaster control over the information flow, which allows avoiding losing or corrupting information. The implementation of the elastic buffer can be performed with two approaches, which are asynchronous and synchronous. The synchronous one uses the same clock for the whole architecture, while the asynchronous one uses different clocks; both approaches can use the handshaking method, whereas half-full approach is only used on the asynchronous one.

The half-full method is the best option to implement the EB in both USB standards. The control for the 3.0 version is based on the use of SKP symbols, while for the 2.0 a data threshold must be passed. Thus, further stages are independent of the EB performance. Considerations as the word width to be processed must be considered for the USB 3.0 standard. It could result in a large area requirements or impose tighter timing requirements.

The operating frequency of the EB for the USB 3.0 standard is 10 times less than data rate and hence, this frequency would be around 500 MHz. Since the USB 2.0 standard considers a single serial data path through the whole transceiver, the operating frequency is the same for all the blocks. The aim of this work is focused on high-speed serial links, which causes only the implementation of the high-speed link that works at a frequency of 480 MHz for the 2.0 version.

### 3 Framework Simulation of USB Transceivers

The description of the main USB 3.0 and 2.0 transceiver building blocks is presented in figure 2.1. The overall framework and mixed-signal simulation environment that can incorporate channel models is explained in this chapter. The transmitter, receiver, and the channel composition are explained as part of the simulation framework used to evaluate the design of the different building blocks. Different levels of abstraction can be incorporated to the simulation framework for each building block, from its behavioral Verilog-AMS version up to its post-layout implementation, as it is detailed next.

#### 3.1. Framework Simulation for USB Transceivers

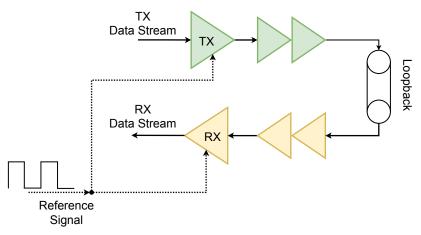

In figure 3.1 (a), it can be observed how a full USB link is simulated. This includes the main blocks which are the transmitter (Tx), interconnect channel, receiver (Rx) and the clock generator at the Tx and the recovery timing unit at the Rx. The simulation configuration used in this work is a loopback, as illustrated in figure 3.1 (b), where the interconnect channel is incorporated in the Tx/Rx connection. It is observed how the reference signal feeds the transmitter and receiver. The objective of the framework is to evaluate that the data sent through the transmitter are the same at the output of the receiver stage. Through a mixed-signal simulation environment in Verilog-AMS, analog and digital models are included, as well as the models generated for the EBs through the digital design flow that is detailed in chapter 4. The simulation and validation results using this framework are shown in chapter 5.

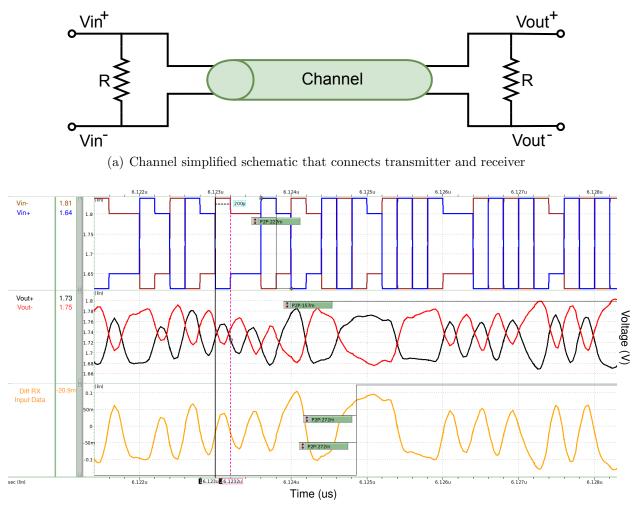

The representation of the interconnect is based on S-parameters, where for simulating such channels, a netlist is created and extracted in *Custom Compiler* of Synopsys. The representation is generated including the instantiation of a block that includes the S-parameters from a characterization presented in [30]. The coupling of this block is represented with a differential pair connection. The termination resistance at the Tx and Rx sides are considered

(a) Simplified diagram of the simulation setup for a single differential lane

(b) Loopback configuration used for USB transceiver simulations

Figure 3.1: Framework for simulation of USB transceivers

in the simulation, as it will be discussed later. The simulator used for mixed-signal analysis is the *Custom Waveview* of Synopsys. The framework simulations are performed through scripts, which are documented in [31]. This means that the description of each of the blocks that integrate the transceiver is included through coding lines in Verilog-AMS to represent either their analog or digital behavior. The interconnect and the elastic buffer are modeled from a derived netlist. The channel mode is imported from a touchstone S-Parameter file, and the EB is a generated from the IC post place and route netlist obtained by the Synopsys digital synthesis framework, using tools such as *Design Compiler* and *Integrated Circuit Compiler*.

Since both the digital and analog domains are required in the simulations, analog to digital (AD) and digital to analog (DA) converters must be used in the AMS simulation framework. Digital signals such as clock, reset, data and control signals are injected at the input of the transceiver before being connected to the channel, and are transformed to the analog domain at the equalizer and Tx driver. The conversion is based on a description in Verilog-AMS, where characteristics such as the number of bits to be converted (1 bit for the USB link), and the maximum voltage level (3.3 V for both links) can be adjusted. The signals should remain analog up to the first digital block of each USB transceiver at the receiver (deserializer for 3.0 and EB for 2.0). Before converting the signals back to the digital domain, comparators are used in order to determine if the receiver input differential voltage represents a higher or lower value. Once the comparator generates the value, analog-digital converters (ADCs) are used. Settings as the number of bits to represent and midpoint level can be adjust. More details about digital-analog converters (DAC) and ADC can be found in [31].

The descriptions of the USB 3.0 and 2.0 transceivers are detailed next. Each transceiver contains transmitter and receiver blocks, in which the analog and digital models are detailed. The interconnect that is used in the loopback is included, with its characterization and model

extraction from S-parameters.

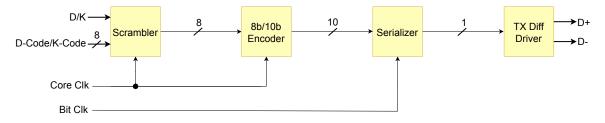

#### 3.2. Transmitters for USB 3.0

The first part of the transceiver belongs to the transmitter, which is depicted in figure 3.2. It has four blocks, which are the scrambler, encoder, serializer, and differential driver. Each block is explained below and modeled at a behavioral level. It is used the environment of mixed-signal that combines digital and analog behaviors. The general specifications based on USB 3.0 standard are the data rate of 5 Gbps with a bit-time of 200 ps for serial data, whereas for parallel data, 10 bits are used with a period of 2 ns.

Figure 3.2: USB 3.0 transmitter simplified block diagram

#### 3.2.1. Scramblers

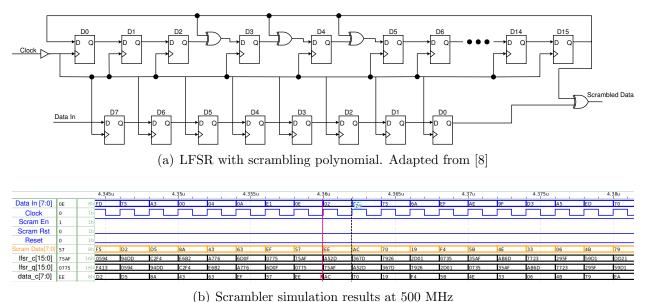

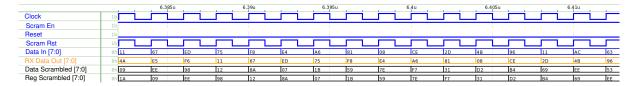

Data scrambling is necessary for serial links as a result of imperfections in the transmission lines. Poor line integrity leads to consecutive bits in error and these errors cannot be corrected or even detected. Scrambling data solves this issue, by adding controlled randomness and spreading error bits in close proximity [32]. The implementation used for the scrambler consists of a linear feedback shift register with the polynomial expression in equation (2) [8], using the open-source code implementation in [33]. The circuit representation of equation (2) is shown in figure 3.3 (a).

$$G(X) = X^{16} + X^5 + X^4 + X^3 + 1$$

(2)

This block is implemented at a behavioral level with the use of a hardware description language as Verilog. A mixed-signal simulation is carried out for modeling the USB transceiver. This block is one of digital type and its simulation results are observed in figure 3.3 (b). The blue signals belong to its inputs, the orange one is the output and the black ones are internal registers that perform some preliminary results. The reference signal has a period of 2 ns since the data is driven in a parallel form and it is also observed with the markers. The input data is performed with the use of several *Pseudo-Aleatory Random Bit Sequence* (PRBS) of different seeds to introduce to the system some randomness in terms of evaluation and not expected predictable patterns. Among the purposes of scrambling, the balance in the number of logic levels is performed for avoiding issues at the receiver stage with the recovery clock [34].

Figure 3.3: Scrambler block diagram description event-driven simulation of its behavioral AMS model

#### 3.2.2. 8b/10b Encoders

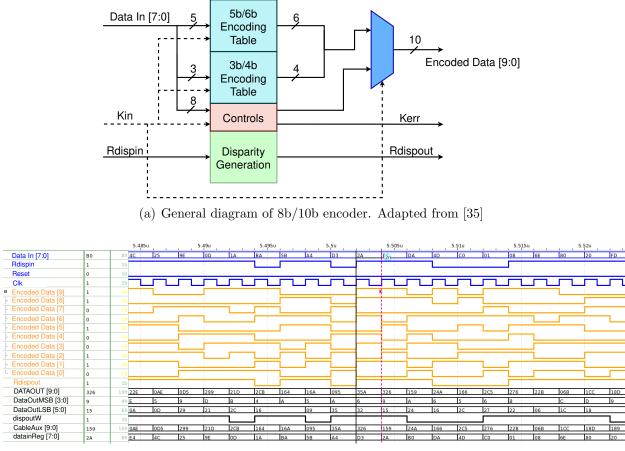

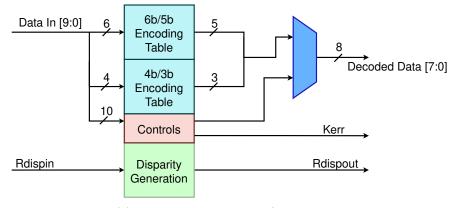

The next block is an encoder 8b/10b that converts an 8-bit input data into 10-bit data. In figure 3.4 (a), it is depicted a general description on how the input data is separated into 3 MSB and 5 LSB. The 3 bits transform into 4 bits, and the remaining 5 bits transform into 6 bits. Two conversion tables are used for making the mapping depending on disparity generation. The disparity generation is implemented with a state machine as follows: if the incoming data show even parity, the next input data maps to a different disparity with respect to the actual data, but if the incoming data have odd parity, the next data block will use the same disparity [35].

There are special characters that are used for control. The first input is called *Kin* to let the encoder knows how to map the 8-bit input. In case the input is an invalid special character, the second signal *Kerr* toggles and the output will be the corresponding information block [36]. Three encoder implementations are explored in [35]; for this work is implemented the decoders and multiplexers approach, which is depicted in figure 3.4 (a). The 8-bit data is converted properly into the 10-bit representation. The decoder transforms the input data to a specific value and the multiplexer determines, which data go out for each decoder since the disparity signal acts as a control line.

The simulation of this block belongs to a digital type, and the procedure as scrambler is applied for the encoder. In figure 3.4 (b) is observed the response of the encoder; the blue, orange and black signals correspond to the inputs, outputs, and internal registers, respectively. Balance in the number of ones and zeros is exploded by this block, in order to facilitate the recovery reference signal in the receiver stage by the CDR. This balance allows a

(b) 8b/10b encoder simulation results at 500 MHz

Figure 3.4: 8b/10b encoder block diagram description and event-driven simulation of its behavioral AMS model

maximum of 5 consecutive bits with the same logic level, otherwise, the codification is wrong. The balance can be observed and counted with the markers of the aforementioned figure. This block is the last one with a slower reference signal, because this block is connected to the serializer. The action of disparity is observed, where the parity signal is changed with respect to its output and input data.

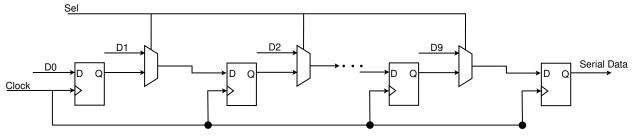

#### 3.2.3. Serializers

The next block is the serializer, which converts data from a parallel arrangement to a stream of bits that can be converged through a single lane. This allows reaching transmission rates at gigabits per second with a dedicated serial channel that is properly designed. The implementation for this work is based on shift registers and multiplexers [37]. For transferring the 10-bit data without losing any bit after the 8b/10b encoder, the serializer must work ten times faster than the parallel blocks such as scrambler and encoder. The faster clock of 5 GHz and the slower one of 500 MHz feed the serial and parallel blocks,

(a) Serializer's simplified schematic. Adapted from [37]

(b) Serializer simulation results at 5 GHz

Figure 3.5: Serializer block diagram and event-driven simulation of its behavioral AMS model

respectively. In figure 3.5 (a), it is observed a simplified circuit for serializing the parallel data. For each 9 clock cycle of the serial reference signal, the mux selector is switched for the propagation of data through the circuit, making the serialization possible.

In figure 3.5 (b), the serializer is modeled at a behavioral level with the same scenario of previous blocks. The difference is the frequency because this block must be 10 times faster. The blue signals are their inputs and these are the clock, reset, and selector. The stream of data is observed with the orange signal and it has period of 200 ps that is the bit-time given by USB 3.0 standard. The black signals perform the shift of parallel data, which are internal signals of the logic. It is observed that the selector is asserted only 1 of 10 possible clock periods. The remaining 9 periods are low and it is for propagating the data through the registers.

#### 3.2.4. Transmitter Differential Drivers

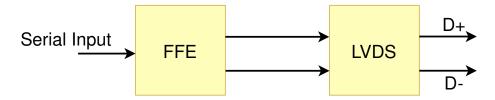

The signals from previous blocks might degrade their levels, which cause *Intersymbol Interference* (ISI) and inadequate interpretations at the receiver caused by the losses that interconnect adds. Therefore, the signals are enhanced before the interconnect to avoid such problems. They are driven by a buffer that allows them to transmit the signal either by their current or voltage levels. *Low-Voltage Differential Signaling* (LVDS) is used for this implementation, since the facility to transmit voltage levels instead of current, along with a decrease in power consumption in an eventual IC implementation. The block diagram of the transmitter driver is observed in figure 3.6. The enhancement of the signal is addressed by the *Feed-Forward Equalizer* (FFE), followed by the LVDS. The output of this driver goes to the physical channel.

Figure 3.6: Transmitter differential driver simplified block diagram

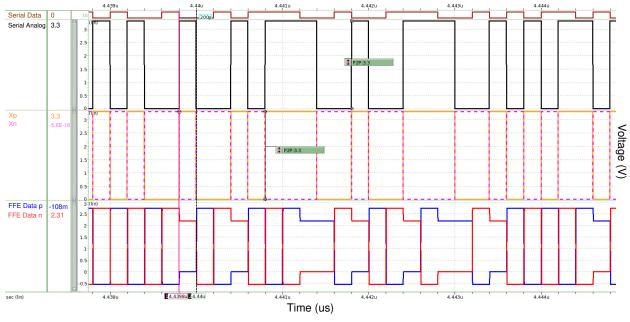

The FFE improves the signals through the use of a discrete filter. The filter is a *Finite Impulse Response* (FIR) topology that means no feedback on the system. The representation of this filter is by a difference equation and the operating principle is observed in figure 3.7 (a). The sum is performed by the input sample and its delayed samples multiplied by a factor called tap. The goal of the filter is to eliminate the post-cursor or pre-cursor of the signal to increase the signal levels [38]. The transfer function of the FFE is observed in equation (3), where the N factor belongs to the number of taps. The minimum number of taps is 2, otherwise, it does not behave as a filter. The number of taps used for this filter is 2 and they are 0.834 and -0.166 as first and second tap, respectively [39].

$$y(n) = \sum_{k=0}^{N} b_k x(n-k)$$

(3)

Since this driver is connected to a physical channel, this must be modeled in an analog manner. The first step is to transform the digital serial data that comes from the serializer. Once this is done, the signal is passed to analog. The generation of the negative signal is necessary in order to accomplish the principle operation of the equalizer, where the positive

(a) FFE equalizer's simplified block diagram. Adapted from [38]

(b) Feed-forward equalizer simulation results at 5 Gbps

Figure 3.7: FFE block diagram description and simulation of its behavioral AMS model

and negative signals are required. In figure 3.7 (b), it is depicted all the previous description, where the input digital data is the brown signal. The black signal shows the transformation of digital to analog, and a variation voltage from 0 to 3.3 V is observed. The generation of the positive and negative signals are observed in the ,solid-orange and dash-pink signals. respectively; these signals are opposite to each other. Finally, the equalization of the signals is performed for providing to the interconnect lower values of noise, distortion, and losses. In the blue and red signals are described the behavior of the equalizer. A decrease in each signal is observed when consecutive bits with the same level voltage is presented; otherwise the high-level is preserved. The main idea of this response is to eliminate either the precursors or post-cursors of the main signal. It is observed that the outputs have a period of 200 ps dictated by the USB 3.0 version.

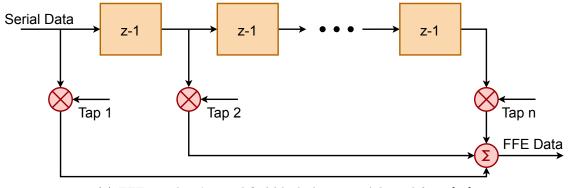

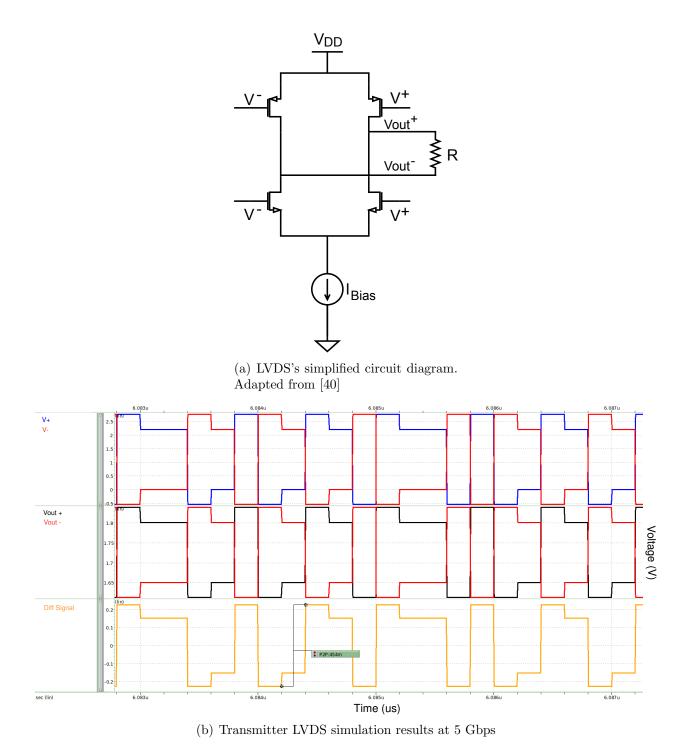

The equalizer is driven by a differential buffer that can be voltage or current. In this work is used voltage signaling because of the simplicity of interpretation [40]. The buffer allows transmitting a lower peak to peak voltage (Vpp). This alleviation enables the transmission of a signal range of 150 mVpp up to 400 mVpp [41, 42]. Several configurations are found in [40, 41, 42], however, the scope of this work is not the implementation of this block. In figure 3.8 (a), it is depicted a configuration for LVDS to give some insight at circuit level; nevertheless, the use of other blocks as *Common-Mode Feedback* (CMFB) is necessary to improve the differential signals. The outputs are connected to a resistance (R) that models the differential impedance of the interconnection that is 90  $\Omega$ .

The output of the equalizer is buffered to an LVDS for matching the interconnect and the transmitter. The block is modeled at analog-behavioral level, where the positive and

Figure 3.8: LVDS circuit description and event-driven simulation of its behavioral AMS model

negative are received and these are conditioned to represent a lower Vpp. In figure 3.8 (b), is observed the simulation results of LVDS, where the red and blue signals (first row) are the inputs. The red and black signals (second row) are the outputs of the LVDS. It is observed the offset of the signals as well the decrease in the Vpp voltage around 225 mV for each

(b) Channel simulation results of 2 meter length at 5 Gbps

Figure 3.9: Interconnect description and simulation at mixed-signal level

one. The difference of such signals is used to evaluate if the incoming signal at the receiver is represented with a high or low value. The difference is represented in the orange signal (third row), where the Vpp injected to the interconnect is near 450 mV. Inevitably, losses caused by interconnect are presented and the receiver will drive a lower Vpp value. It is vital the implementation of a transmitter driver to avoid further loss of signals at higher data rates.

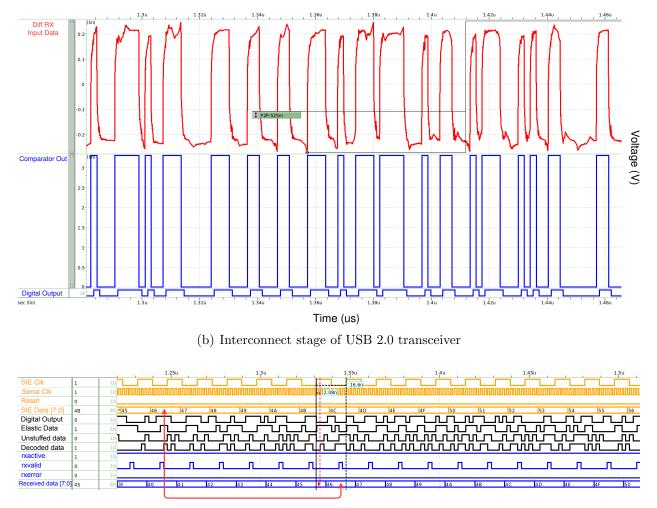

# 3.3. Interconnect for USB 3.0 and 2.0 Transceivers

The physical channel is responsible for carrying the signals from transmitter to receiver. This channel can be made of cables, connector or PCB segments. Characterization of different physical channels is discussed in [30]. At the same time the specifications for USB 2.0 transceiver are covered with this interconnect. Essentially, the channel models the differential pair, where its differential impedance is 90  $\Omega$ . The purpose of the interconnect for this work is to model a complete transceiver, where a channel is included in order to add losses to the signals for getting a realistic response. The used channel for this work is from [30], where the S-parameters are used for the simulation in the mixed-signal environment. In figure 3.9 (a), it is depicted the functioning of the interconnect, where the resistances describe the matching that should exist between both inputs and outputs. The matching along with both LVDS at transmitter and receiver must avoid the arise of losses as well other effects that appear on high-speed interfaces.

The results of the measurement of the interconnect are observed in figure 3.9 (b). The brown and blue signals represent the output of the transmitter LVDS buffer. The outputs are represented with the red and black signals, where losses and distortion are observed in such signals. The differential voltage at the output is observed in the yellow signal. There is a decrease in the magnitude of Vpp since the value passes from 450 mV around 225 mV.

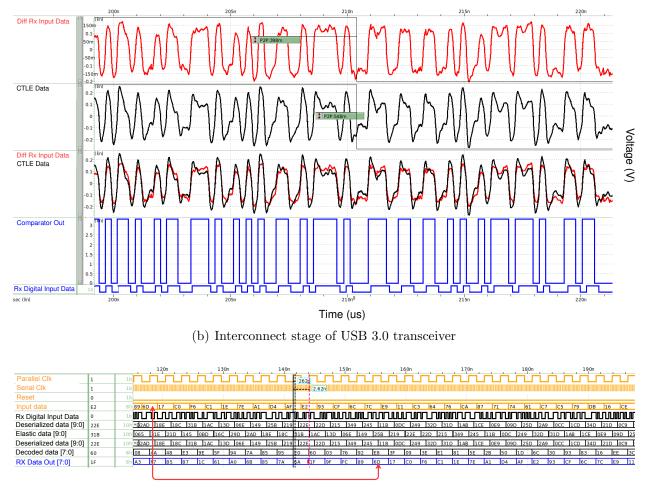

## 3.4. Receiver of USB 3.0 Transceivers

The third part of the transceiver belongs to the receiver, which is depicted in figure 3.10. It has seven blocks, which are the differential receiver driver, CDR, deserializer, elastic buffer, k28.5 detector, decoder, and descrambler. Each block is explained below and modeled at a behavioral level and is used a mixed-signal environment that combines digital and analog behaviors. The same specifications are applied for the receiver based on USB 3.0 standard. The data rate is 5 Gbps with a bit-time of 200 ps for serial data, whereas for parallel data, 10 bits are used with a period of 2 ns. Most of the blocks work in an inverse manner of transmitter because the data must be recovered into an 8-bit data.

Figure 3.10: USB 3.0 receiver simplified block diagram

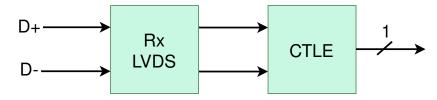

# 3.4.1. Receiver Differential Drivers

The signals at the edge of the interconnect are received by a differential driver, which operates oppositely to the transmitter driver. The signals are treated by the receiver LVDS and then, they are equalized because of the losses that the interconnect adds. These losses are the reflection, crosstalk, dispersion, attenuation, among others [43]. The aforementioned description is depicted in the block diagram of figure 3.11, where the LVDS is the same as the transmitter in terms of operation principle, and the equalizer is a *Continuous Time Linear Equalizer* (CTLE). The aim of the LVDS is to match the signals of the interconnect with the receiver. Such signals are degraded resulting in a lower Vpp than when they were transmitted. It is sought that their differential Vpp is above 200 mVpp [44].

Figure 3.11: Receiver differential driver block diagram

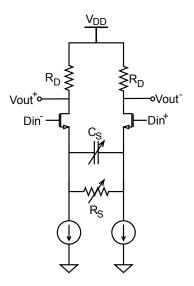

The signals at the output of the receiver LVDS are enhanced by the CTLE. Such equalizers is a continuous equalizer, where the circuit that represents the equalizer is observed in figure 3.12. The differential configuration, along with the array of the passive components as resistances and capacitors, generate the existence of two poles and a zero in the frequency response of the equalizer [45]. The transfer function of the equalizer is observed in equation (4).

Figure 3.12: CTLE circuit representation. Adapted from [45]

$$H(s) = A_{DC} \frac{s - \omega_z}{(s - \omega_{p1})(s - \omega_{p2})}$$

$$\tag{4}$$

Where  $A_{DC}$ ,  $\omega_z$ ,  $\omega_{p1}$  and  $\omega_{p2}$  are described in equations (5), (6), (7), and (8) respectively. The parameters shown in these equation belong to the components of figure 3.12; furthermore, the transconductance corresponds to the transistor pair-differential and  $C_p$  is the load that CTLE drives at the output.

$$A_{DC} = \frac{g_m}{C_p} \tag{5}$$

$$\omega_z = \frac{1}{R_s C_s} \tag{6}$$

$$\omega_{p1} = \frac{1 + g_m R_s/2}{R_s C_s} \tag{7}$$

$$\omega_{p2} = \frac{1}{R_D C_p} \tag{8}$$

In [8], it is mentioned the values of each parameter of the transfer function of equation (4). The values are the gain, zero, and poles, which are observed in table 3.1 with their frequency expressed in Hz and the angular frequency value. The scope of this work is to model the CTLE at a behavioral level, which means using the values of the below table and not making a circuit derivation.

Table 3.1: CTLE values of their transfer function

| $A_{DC}$     | $f_z (GHz)$ | $\omega_z (Grad/s)$ | $f_{p1}\left(GHz\right)$ | $\omega_{p1} (Grad/s)$ | $f_{p2}\left(GHz\right)$ | $\omega_{p2} (Grad/s)$ |

|--------------|-------------|---------------------|--------------------------|------------------------|--------------------------|------------------------|

| $110 x 10^9$ | 0.65        | 4.0841              | 1.95                     | 12.2522                | 5                        | 31.4159                |

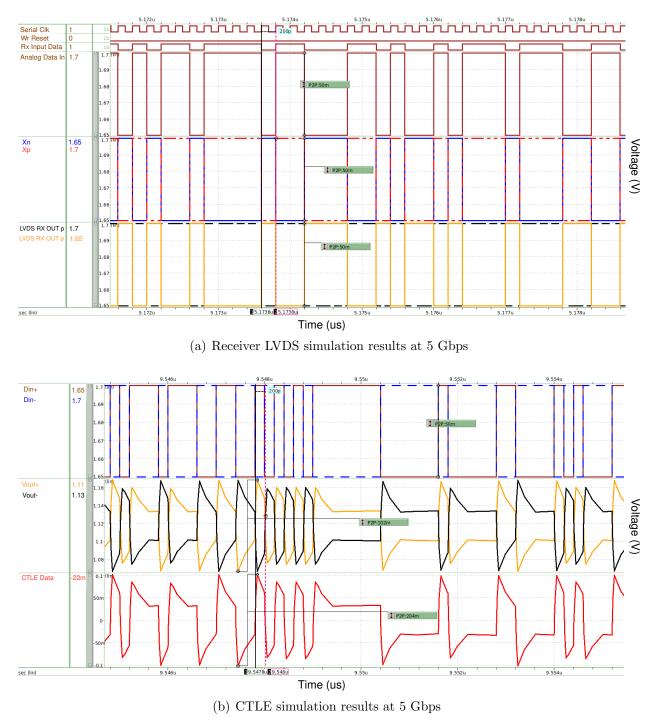

Simulation results of receiver LVDS and CTLE are observed in figure 3.13 (a) and (b), respectively. For demonstration, digital signals are injected into receiver module LVDS and these are in brown, and correspond to the reference signal, reset, and serial data. Then, serial data is transformed and modeled with the values of LVDS standard mentioned in [41, 42] to an analog signal of brown color. Then, the negative and positive signals represented in solid blue and dashed red colors are generated. As the transformation of digital to analog has implicit the signaling value to pass through the interconnect, the receiver LVDS works as a coupler. The outputs are highlighted in solid yellow and dash black.

The outputs of the receiver buffer are connected to the CTLE, where the signals of figure 3.13 (b) in solid brown and dash blue colors of the first row, represent such signals. Positive and negative signals are observed in the second row with black and yellow colors. It is

Figure 3.13: Receiver driver implementation at behavioral AMS level

observed a comparable response as FFE when consecutive bits have the same level voltage. Only the first bit has the maximum voltage peak and the remaining bits decrease their values until a voltage change is presented. The function of the equalizer is accomplished because the differential voltage value at the input is around 100 mV, whereas for the output

observed in the red signal, the difference increases up to 200 mV. A comparator block must be performed to decide with its difference, if the next bit will be represented with a lower or higher value.

# 3.4.2. Clock and Data Recoverys (CDR)

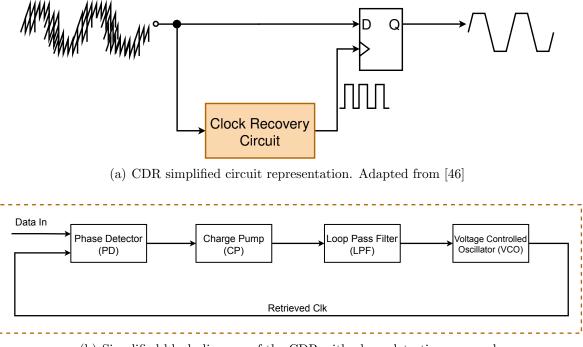

The recovery of the transmitter's clock signal is required and is performed by the Clock and Data Recovery (CDR). The two main functions of the CDR are to recover the clock signal from the data stream and retimed the data with the recovery clock in order to reduce jitter [46]. The representation of CDR's purpose is observed in figure 3.14 (a); however, in this work, the implementation of CDR is avoided by the fact that a loopback is performed for the evaluation of the transceiver. Thus, it is used the same clock of the transmitter in the receiver; only the data is retimed at the output of CTLE to synchronize the stream at the receiver stage.

CDRs can be implemented by phase or delay detection of the input data regarding the reference signal generated by the CDR. An implementation with delay detection leads to jitter propagation and thereby the retimed data is not a cleaner signal. Meanwhile, phase detection enables the jitter to be significantly reduced and consequently, clearer retimed data. In figure 3.14 (b), a simplified block diagram of the CDR using phase detection is depicted.

(b) Simplified block diagram of the CDR with phase detection approach

Figure 3.14: Simplified operation and block diagram of the CDR

The first block is the phase detector (PD), which compares the phase between the input data and the CDR reference. This provides information to adjust the phase of the CDR clock. The charge pump (CP) is used to store energy to increase or decrease the voltage for a certain amount of time. The low pass filter (LPF) suppresses ripples that can affect the VCO. The last block is the voltage-controlled oscillator (VCO), which generates a periodic signal at the output according to the input voltage applied to it. The goal of the CDR is that the phases of the input data and the reference signal of the CDR are as similar as possible such that the receiving stage is locked [46].

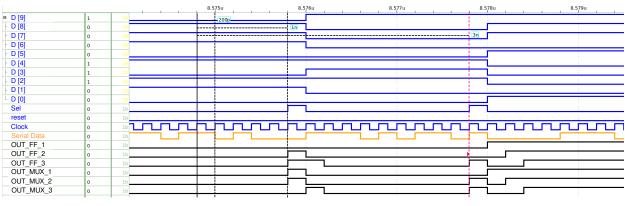

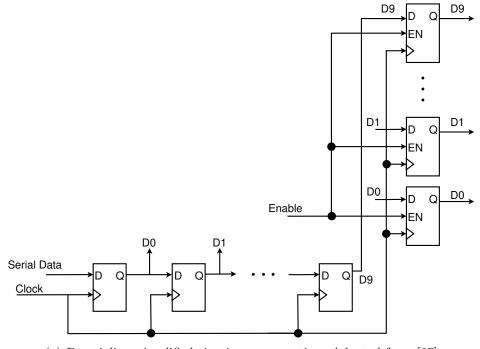

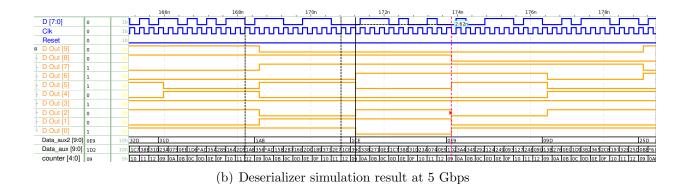

#### 3.4.3. Deservalizers

Once the data is retimed, the deserialization of the data stream is performed. Therefore, the serial data changes to a parallel one of 10-bits. The behavior of the deserializer is based on figure 3.15 (a), where the data is injected in the first register and each clock cycle is propagated through the next registers [37]. When the data is on the 10 registers, these are connected to the vertical array of enable-registers. This array facilitates the holding of the 10-bit data for a whole clock cycle of the parallel reference signal. In figure 3.15 (b), is observed the response at the behavioral level. The blue signals belong to the inputs, the black ones are internal signals for producing the output and the orange one is the deserialized data. The deserialization is produced with the use of a counter that behaves as the enable signal to propagate a new deserialized data.

(a) Deserializer simplified circuit representation. Adapted from [37]

Figure 3.15: Deserializer circuit description and event-driven simulation of its behavioral AMS model 3.4.4. K28.5 Detectors

This block performs the data alignment according to the special K-symbol. This K-symbol is the K28.5 that has a special value that the block detects and allows the data alignment. The special feature of K-symbols is that they have 5 bits in a row, either of the two logical levels available. This facilitates the detection and data alignment [47]. Nevertheless, the goal of this block is when a loopback is not performed because it must ensure the data synchronization. The implementation of this block is out of the scope of this work.

## 3.4.5. Elastic Buffers

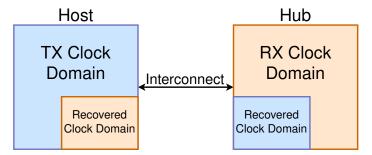

The purpose of a USB transceiver is the information flow between two modules (host and hub). Each one can assume the function of transmitter or receiver by the half-duplex configuration. In figure 3.16, it is depicted a description of host and hub with their respective clock domains, where the host performs the function of transmitter and the hub the function of the receiver. The same reference signal is not the given for both devices. Hence, the transmitted reference signal is retrieved in the hub from the data stream, where the reference transmitter signal is inserted. The recovered reference signal is used to synchronize the incoming data at the receiver stage. However, this signal might have deviations by the nature of a communication system; therefore, an elastic buffer is used. The elastic buffer tolerates these deviations with data insertion in a memory block or controlling the data path of further stages to avoid data losses. The implementation of this block is detailed later.

#### 3.4.6. 8b/10b Decoders

The reverse operation to coding is implemented with the 8b/10b decoder. In essence, the idea is the same as encoder 8b/10b. Instead of just mapping data of 8 bits to 10 bits, it is mapped a data of 10 bits to 8 bits. The same control signals as disparity and special character are used to produce the 8-bit output. The data is split into 6 and 4 bits, which represent the LSB and MSB, respectively. The previous description is observed in figure

Figure 3.16: Clock domains representation of USB transceiver

3.17 (a). Each data is transformed into 5-bit and 3-bit data and then they are concatenated to generate the 8-bit data.

Simulation results are observed in figure 3.17 (b), where inputs are represented with blue signals and the output is represented with the orange signal. It can be observed the variation in parity signal is based on input data variations. The period of this block is 2 ns and transformation of 10-bit data to 8-bit data is performed. This output data is almost the original, because the remaining block that is the descrambler, converts the data into the original one.

(a) General diagram of 8b/10b decoder

(b) Simulation results of 8b/10b decoder at 500 MHz

Figure 3.17: 8b/10b decoder description and event-driven simulation of its behavioral AMS model

#### 3.4.7. Descramblers

This block restores the originally sent data. The implementation is absolutely the same as the scrambler. This implies that the same polynomial showed in equation (2), circuits of figure 3.3 and behavioral description of scrambler are used. In figure 3.18, it is observed the

simulation response. Blue signals belong to the inputs, the black one to internal signals for producing the orange signal output. For performing this simulation, the data is scrambled and then descrambled. Once the data is scrambled, it takes two cycles to return its original value.

Figure 3.18: Descrambler event-driven simulation of its behavioral AMS model at 500 MHz

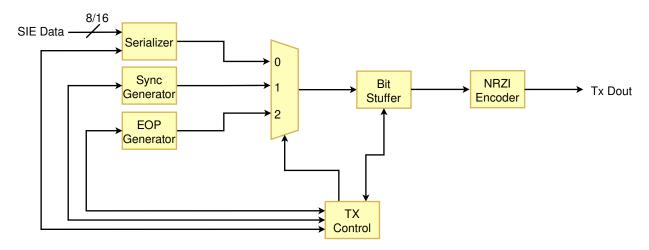

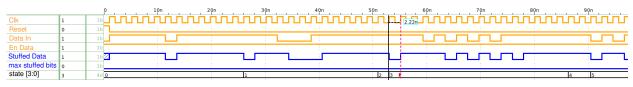

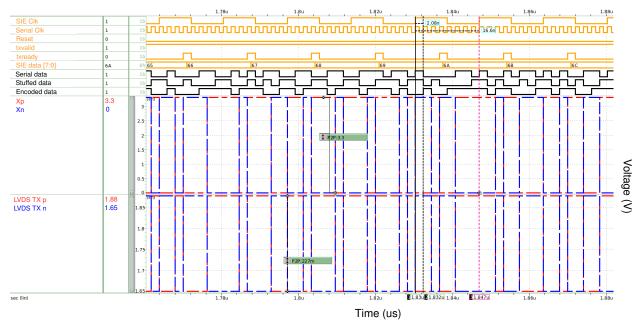

# 3.5. Transmitter of USB 2.0 Transceivers

The first part of the transceiver belongs to the transmitter, which is depicted in figure 3.19. The simplified block diagram shown in chapter 2 has 4 blocks. However, by the fact that the data is transmitted serially instead of parallel, several patterns must be generated to provide synchronization into the transceiver [48]. Therefore, this block diagram has 7 blocks and these are the serializer, Sync/EOP generators, a multiplexer that connects the previously mentioned blocks, a bit stuffer, an encoder, and a control FSM. These blocks are modeled digitally, and mixed-signal simulation is performed with the interconnect and LVDS described for USB 3.0 transceiver. Equalizers are not used because the data rate is less, and losses are not harmful. The general specifications based on USB 2.0 standard are the data rate of 480 Mbps with a bit-time of 2.08 ns for serial data, whereas for parallel data, 8 bits are used with a period of 16.64 ns.

Figure 3.19: USB 2.0 transmitter simplified block diagram

#### 3.5.1. Transmitter Control FSM

Unlike the USB 3.0 standard, this transceiver uses a state machine to control the digital shared path and to communicate with the Serial Engine Interface (SIE) that is responsible

for generating the appropriate packets for the USB link. This interface is out of the scope of this work.

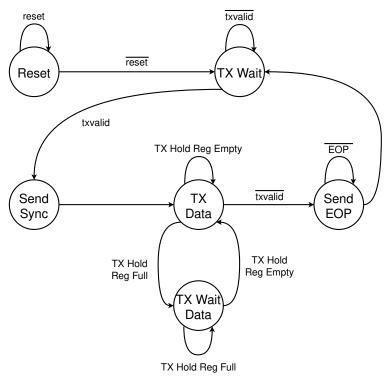

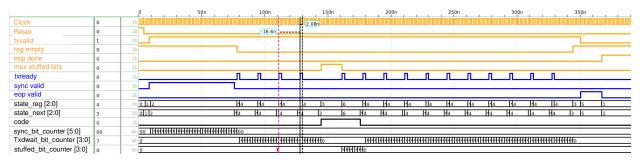

The state machine is composed by six states and is depicted in the figure 3.20 (a). The first state is the *Reset* state and is entered when the reset signal is asserted. Once this signal is not asserted, it goes to the TX Wait state, where this machine waits for the txvalid signal sent by the SIE. This indicates that data transmission is about to take place. When this signal is asserted, it goes to the Send Sync state, and is sent the Sync pattern through the digital shared path. When the sending of this pattern is finished, it switches to the TX Data state, where it is analyzed if new data is coming from the SIE. If the hold register is no longer empty then goes to the TX Wait Data state; it is waited for a byte time to return to the previous state and analyze if there is new data. During the waiting state, the present data is serialized and sent through the digital shared path [49].

The maximum number of stuffed bits is also detected, which it is 8. It occurs when the transmitter waits for a byte time for reading new data. The control machine will be transitioning in the last two mentioned states until the txvalid signal is no longer asserted and that is when it is moved to the *Send EOP* state. This state sends the end of packet (EOP) pattern and it waits for an EOP flag indicating that the pattern has been inserted into the digital shared path. Thus, it is returned to the initial wait state waiting for the assertion of the txvalid signal by the SIE again.

(a) State diagram of the transmitter FSM. Adapted from [49]

(b) Transmitter control FSM simulation results at 480 MHz

Figure 3.20: Transmitter control FSM state diagram description and implementation at behavioral level

The simulation of the digital path control of the transmitter is shown in figure 3.20 (b). The orange signals correspond to the inputs, the blue ones to the outputs, and the black ones to internal signals that allow the monitoring of the FSM. With the assertion of the txvalid signal, it is passed to the sending state of the Sync pattern. It will be a time of 32 bits that is the length of the high-speed link, and the same time is the sync valid signal asserted. Once the sending of the Sync pattern is finished, it will be switching between the data and waiting states that indicates the reading and conversion of the parallel to serial data sent from the SIE. The txready signal is asserted every byte time, indicating to the SIE that the data was consumed by the transmitter. The scenario where the maximum number of stuffed bits is reached is also observed, which implies that a byte time must be waited to be able to continue reading. If the txvalid signal is no longer asserted it goes to the EOP pattern sending state. This indicates the end of data transmission, wherein this state it remains for a byte time and then returns to the waiting state, in expectation of txvalid assertion by the SIE.

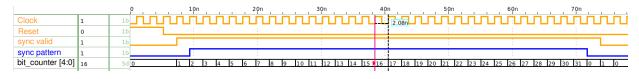

## 3.5.2. Sync Generators

Channel synchronization is achieved with different sent patterns through the channel. The first sent pattern is the *Sync*, which indicates the start of data transmission. For the high-speed link the pattern consists of 32 bits, where the first and last bits have a logic level of 0 and the remaining bits have a logic level of 1. The bit stuffer is disabled when this pattern is sent. The simulation response of this block is shown in figure 3.21, where the blue colored signal corresponds to the output pattern that is injected into the digital shared path. The first and last bit have a logic value of 0 and the remaining ones a logic level of 1, this when the sync valid orange color signal has been asserted.

Figure 3.21: Sync generator simulation results at 480 MHz

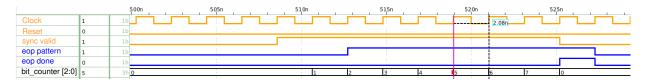

# 3.5.3. EOP Generators