#### Instituto Tecnológico de Costa Rica

#### Escuela de Ingeniería Electrónica

Diseño de una unidad de deslinealización y desnormalización para un sistema de optimización de energía de uso en paneles fotovoltaicos

Informe de Proyecto de Graduación para optar por el título de Ingeniero en Electrónica con el grado académico de Licenciatura

Juan José Rojas Salazar

# INSTITUTO TECNOLÓGICO DE COSTA RICA ESCUELA DE INGENIERÍA ELECTRÓNICA PROYECTO DE GRADUACIÓN ACTA DE APROBACIÓN

Defensa de Proyecto de Graduación Requisito para optar por el título de Ingeniero en Electrónica Grado Académico de Licenciatura Instituto Tecnológico de Costa Rica

El Tribunal Evaluador aprueba la defensa del proyecto de graduación denominado Diseño de una unidad de deslinealización y desnormalización para un sistema de optimización de energía de uso en paneles fotovoltaicos, realizado por el señor Juan José Rojas Salazar y, hace constar que cumple con las normas establecidas por la Escuela de Ingeniería Electrónica del Instituto Tecnológico de Costa Rica.

Miembros del Tribunal Evaluador

Ing. Ronny García Ramírez

Ing. Miguel Hernández Rivera

Profesor lector

Profesor lector

Ing. Alfonso Chacón Rodríguez

Profesor asesor

Cartago, 21 de Noviembre 2016

Declaro que el presente Proyecto de Graduación ha sido realizado enteramente por mi persona, utilizando y aplicando literatura referente al tema e introduciendo conocimientos propios.

En los casos en que he utilizado bibliografía he procedido a indicar las fuentes mediante las respectivas citas bibliográficas. En consecuencia, asumo la responsabilidad total por el trabajo de graduación realizado y por el contenido del correspondiente informe final.

Juan José/Rojas Salazar

Cartago, 21 de noviembre de 2016

Céd: 3-0458-0051

#### Resumen

En este trabajo, se realizó una unidad general de desnormalización-deslinealización para un sistema de optimización de energía de paneles fotovoltaicos, la cuál permite obtener los parámetros necesarios para la búsqueda del punto de máxima de potencia de los mismos. Esta se encuentra basada tanto en el estándar IEEE754 como también el algoritmo de CORDIC, se brinda así mismo una adecuada solución en software y una implementación mediante un HDL. Se muestran además, los resultados de las simulaciones Post Place & Route (recursos, potencia, reporte de tiempos) y una verificación funcional de la misma en una FPGA con un error menor al 0,5% para ambos parámetros de tensión y corriente buscados.

Palabras clave: HDL, FPGA, IEEE754, CORDIC, Verilog, Aritmética Binaria.

#### Abstract

In this work, a general delinearization-denormalization unit for an energy optimization system of photovoltaic panels was implemented. The unit is based on the IEEE754 standard, and uses the CORDIC algorithm. A suitable implementation is provided in HDL. Post Place & Route simulations (resources, power, timming report) and functional verification in an FPGA are also given with a maximum error of 0.5 % for both current  $(I_s)$  and voltage  $(\alpha)$  parameters.

Keywords: HDL, FPGA, IEEE754, CORDIC, Verilog, Binary Arithmetic.

### Agradecimientos

Dedico primordialmente este trabajo a Dios, quién ha sido el encargado de darme la fortaleza y entendimiento para llegar a este momento en el que daré por concluido un ciclo tan importante en mi vida.

A muchos profesores que fueron parte de mi formación como profesional, en especial al Dr. Ing. Alfonso Chacón Rodríguez, por el conocimiento brindado, así también por permitirme la oportunidad de desarrollar este proyecto y confiar en mi capacidad para el buen desenvolvimiento del mismo.

A mi querida familia, en especial mis padres, por inculcar valores y actitudes que me han permitido desenvolverme en diversos aspectos y que me han formado como la persona que soy hoy en día, por todo el apoyo a lo largo de mi vida y los sacrificios realizados a través de los años para brindarme el acceso a una educación de calidad.

Por último, agradecer infinitamente a todas las personas que han formado parte de este camino y han colaborado de manera significativa en la consecución de este logro.

Juan José Rojas Salazar

Cartago, 21 de noviembre de 2016.

## Índice general

| Ín | dice | de figuras                                                            | ii  |

|----|------|-----------------------------------------------------------------------|-----|

| Ín | dice | de tablas                                                             | iii |

| 1  | Intr | roducción                                                             | 1   |

|    | 1.1  | Entorno del proyecto                                                  | 1   |

|    | 1.2  | Descripción del problema y justificación                              | 2   |

|    | 1.3  | Síntesis del problema                                                 | 2   |

|    | 1.4  | Meta                                                                  | 3   |

|    | 1.5  | Objetivos                                                             | 3   |

|    |      | 1.5.1 Objetivo general                                                | 3   |

|    |      | 1.5.2 Objetivos específicos                                           | 3   |

|    | 1.6  | Enfoque de la solución                                                | 4   |

|    | 1.7  | Estructura                                                            | 5   |

| 2  | Ma   | rco teórico                                                           | 6   |

|    | 2.1  | Panel Fotovoltaico                                                    | 6   |

|    |      | 2.1.1 Curvas Corriente-Tensión (I-V) para un PV                       | 6   |

|    |      | 2.1.2 Modelo general del panel fotovoltaico                           | 7   |

|    | 2.2  | Modelo de estimación                                                  | 9   |

|    | 2.3  | Estándar IEEE 754                                                     | 11  |

|    | 2.4  | Formato de representación binaria coma fija                           | 11  |

|    |      | 2.4.1 Representación de números negativos                             | 12  |

|    | 2.5  | Algoritmo de CORDIC                                                   | 12  |

|    |      | 2.5.1 Sistema de coordenadas hiperbólico                              | 16  |

|    |      | 2.5.2 Exponencial utilizando el algoritmo hiperbólico de CORDIC       | 17  |

|    |      | 2.5.3 Expansión del rango de convergencia del algoritmo hiperbólico   | 18  |

| 3  | Mo   | delo teórico del algoritmo estimador de parámetros                    | 20  |

|    | 3.1  | Estimación de parámetros                                              | 20  |

|    | 3.2  | Dinámica en la fase plana                                             | 23  |

|    | 3.3  | Resultados del modelo teórico                                         | 27  |

| 4  | Sist | ema de conversión coma fija a coma flotante y desnormalización        | 29  |

|    | 4.1  | Diseño del sistema de conversión, desnormalización y control de datos | 29  |

Índice general ii

|    | 4.2<br>4.3<br>4.4 | Convertidor coma fija - coma flotante y desnormalizador                       | 31<br>35 |

|----|-------------------|-------------------------------------------------------------------------------|----------|

|    |                   | Verilog HDL                                                                   | 36       |

| 5  | Sist              | ema de deslinealización                                                       | 40       |

|    | 5.1               | Función exponencial utilizando el algoritmo de CORDIC hiperbólico en software | 40       |

|    | 5.2               | Sistema de deslinealización implementado en hardware (CORDIC)                 | 40       |

|    | 5.3               | Diseño e implementación del coprocesador de deslinealización por medio        | 71       |

|    |                   | del algoritmo de CORDIC                                                       | 46       |

|    | 5.4               | Ajuste de rango para unidad de deslinealización                               | 49       |

|    | 5.5               | Sistema de control para la unidad de coprocesamiento CORDIC por medio         |          |

|    |                   | de un máquina de estados finita (FSM)                                         | 51       |

|    | 5.6               | Reducción de hardware en la arquitectura CORDIC                               | 51       |

|    | 5.7               | Verificación y resultados del sistema de deslinealización mediante Verilog    | - 1      |

|    |                   | HDL                                                                           | 54       |

|    |                   | deslinealizador CORDIC                                                        | 55       |

| _  | _                 |                                                                               |          |

| 6  |                   | leba completa de la unidad sobre una placa de desarrollo Nexys 4              | 57       |

|    | 6.1               | Descripción de la unidad completa bajo prueba                                 | 57       |

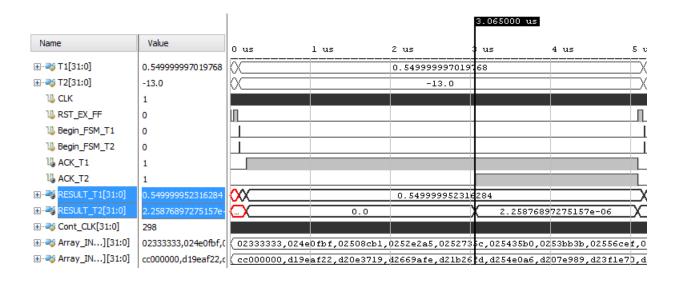

|    | 6.2<br>6.3        | Simulación generada para la unidad completa                                   | 59<br>60 |

|    | 6.4               | Resultados de las pruebas de la unidad general en una placa de desarrollo     | 00       |

|    | 0.1               | Nexys 4                                                                       | 61       |

|    | 6.5               | Recursos utilizados                                                           | 65       |

|    | 6.6               | Reporte de tiempos                                                            | 65       |

|    | 6.7               | Consumo de potencia                                                           | 66       |

| 7  | Cor               | nclusiones y recomendaciones                                                  | 68       |

|    | 7.1               | Conclusiones                                                                  | 68       |

|    | 7.2               | Recomendaciones                                                               | 69       |

| Bi | bliog             | grafía                                                                        | 71       |

## Índice de figuras

| 1.1 | energética en un panel fotovoltaico                                                                                                                                                | 4  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

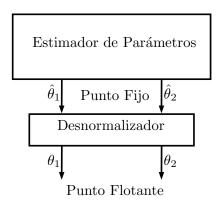

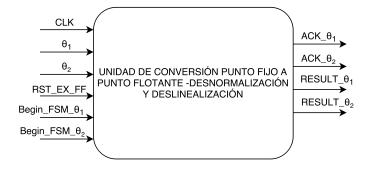

| 1.2 | Diagrama de solución para el sistema de desnormalización y deslinealización, con entradas $\hat{\theta_1}$ - $\hat{\theta_2}$ en coma fija-normalizadas y salidas $\alpha$ - $I_s$ |    |

|     | en coma flotante-desnormalizadas                                                                                                                                                   | 5  |

| 2.1 | Curva característica de corriente(A)-tensión(V) y potencia(P)-tensión(V) para un un panel fotovoltaico $[1]$                                                                       | 7  |

| 2.2 | Modelo general para un panel fotovoltaico, compuesto por un diodo, una fuente de corriente y pérdidas resistivas por cada celda                                                    | 8  |

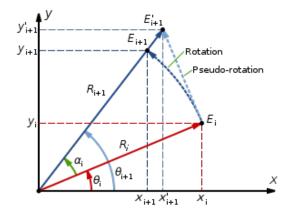

| 2.3 | Vector bidimensional antes y después de ser rotado. [2]                                                                                                                            | 13 |

| 2.4 | Pseudorotación de un vector bidimensional. [3]                                                                                                                                     | 13 |

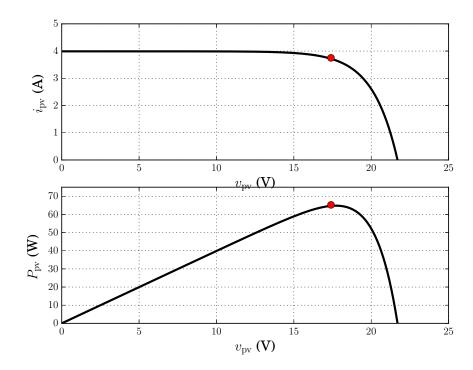

| 3.1 | Gráficas $i$ - $v$ y $P$ - $v$ obtenidas con el modelo para el panel Kyocera Solar KC65T con parámetros $\theta_1=0.625$ y $\theta_2=\ln(I_s)=-12.178$                             | 22 |

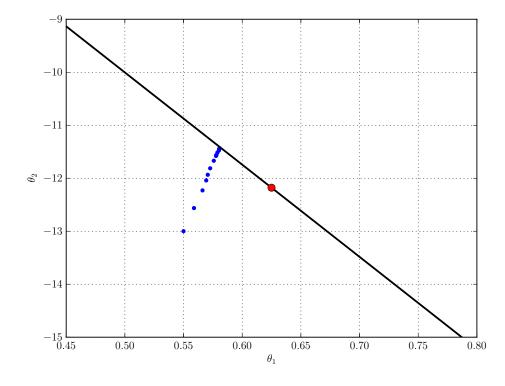

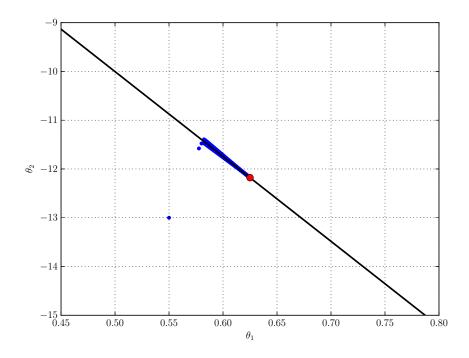

| 3.2 | Evolución de parámetros $\hat{\theta_1}$ y $\hat{\theta_2}$ en el plano bidimensional antes de alcanzar la trayectoria de la isoclina de crecimiento cero                          | 24 |

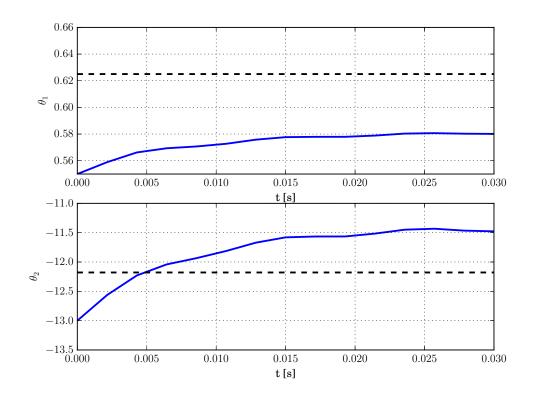

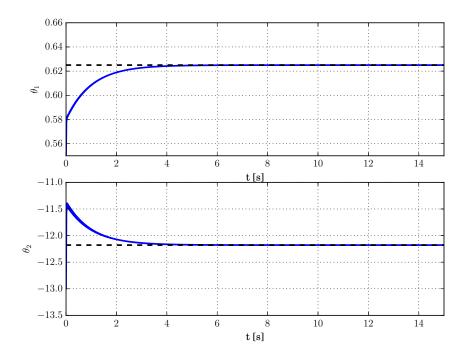

| 3.3 | Dinámica de los parámetros $\hat{\theta_1}$ y $\hat{\theta_2}$ mostrando su evolución en el tiempo.                                                                                |    |

| 3.4 | Tiempo de simulación= 0.030 segundos                                                                                                                                               | 25 |

| 3.5 | zado el punto de equilibrio planteado                                                                                                                                              | 26 |

|     | Tiempo de simulación= 15 segundos                                                                                                                                                  | 26 |

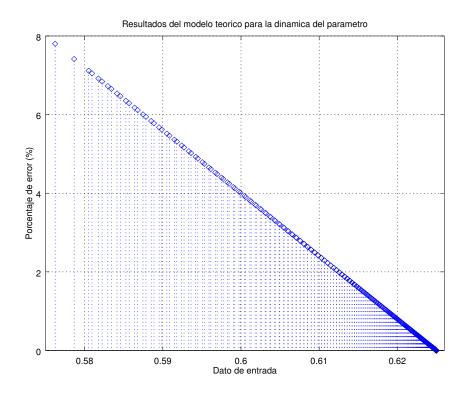

| 3.6 | Porcentaje de error obtenido para la convergencia de $\theta_1 = \alpha$                                                                                                           | 27 |

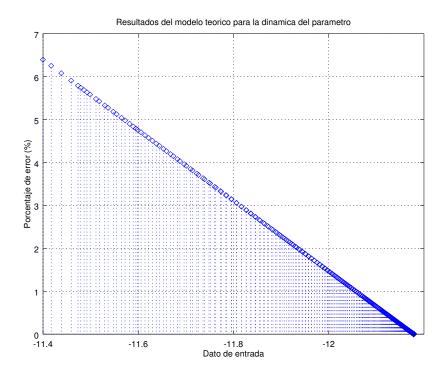

| 3.7 | Porcentaje de error obtenido para la convergencia de $\theta_2 = \ln(I_s)$                                                                                                         | 28 |

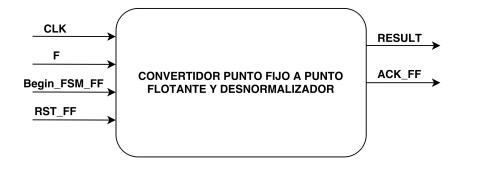

| 4.1 | Diagrama general de entradas y salidas para el convertidor coma fija a coma flotante y desnormalizador                                                                             | 29 |

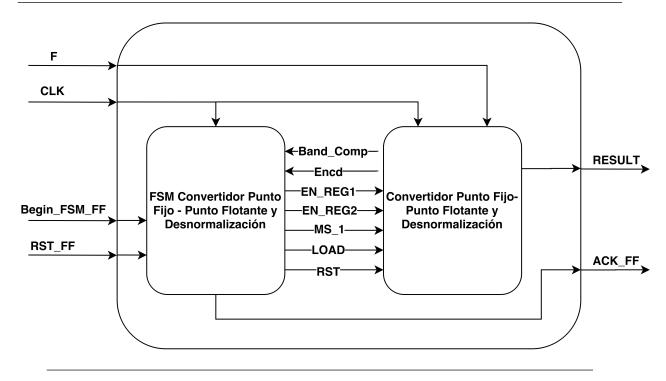

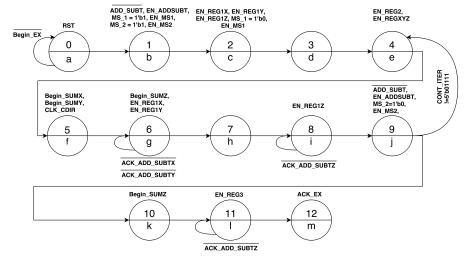

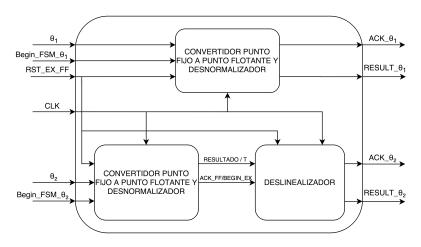

| 4.2 | Sistema de conversión, desnormalización y control utilizando una máquina                                                                                                           |    |

|     | de estados                                                                                                                                                                         | 30 |

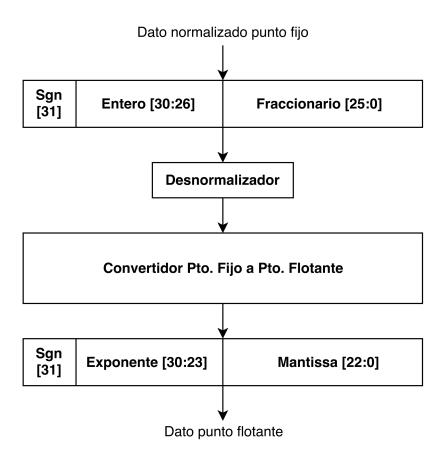

| 4.3 | Diagrama general del sistema de conversión de coma fija a coma flotante y desnormalización de parámetros $\alpha$ - $\ln(I_s)$ (parámetros dependientes de la                      |    |

|     | irradiancia y temperatura)                                                                                                                                                         | 31 |

Índice de figuras iv

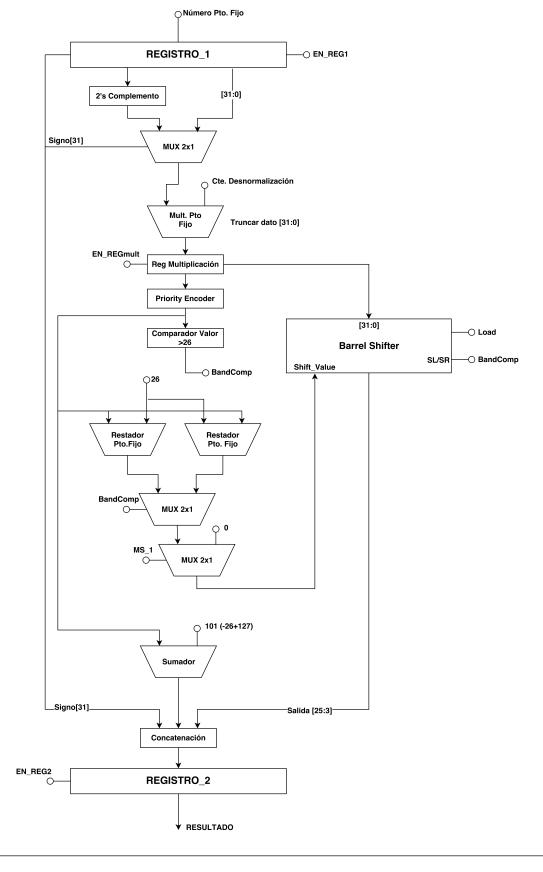

| 4.4        | Circuito de conversión coma fija a coma flotante y desnormalización de parámetros $\alpha$ y $\ln(I_s)$ , con un dato de entrada en coma fija, posteriormente | 00         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.5        | desnormalizado y salida en coma flotante                                                                                                                      | 32         |

| 4.0        | spondiente conversión-desnormalización                                                                                                                        | 35         |

| 4.6        | Esquema general para la comprobación de datos del módulo conversión-                                                                                          | 00         |

| 1.0        | desnormalización                                                                                                                                              | 36         |

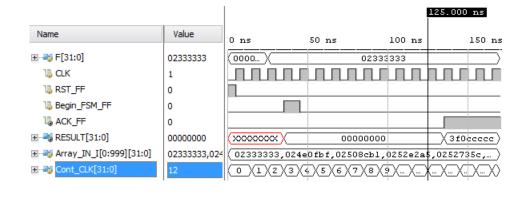

| 4.7        | Simulación del circuito de conversión y desnormalización con una entrada                                                                                      | 00         |

| 4.8        | de 1000 valores provenientes del modelo teórico del estimador $\dots$ Porcentaje de error obtenido para la conversión-desnormalización de $\alpha$            | 37         |

|            | teórica y la simulación post-implementación del circuito                                                                                                      | 37         |

| 4.9        | Porcentaje de error obtenido para la conversión-desnormalización de $\ln I_s$ teórico y la simulación post-implementación del circuito                        | 38         |

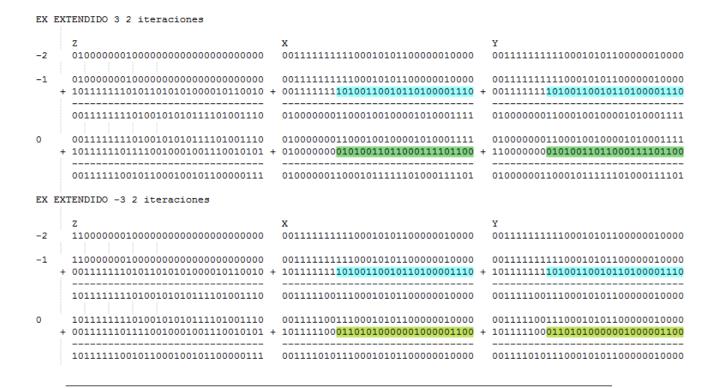

| 5.1        | Algoritmo de CORDIC en Python para el cálculo de la función exponencial                                                                                       | 41         |

| 5.2        | Algoritmo de CORDIC en Python con expansión del rango de convergencia                                                                                         |            |

|            | con dos iteraciones negativas                                                                                                                                 | 42         |

| 5.3        | Representación binaria punto flotante de cada una de las tablas $5.1~\mathrm{y}~5.2~$ .                                                                       | 43         |

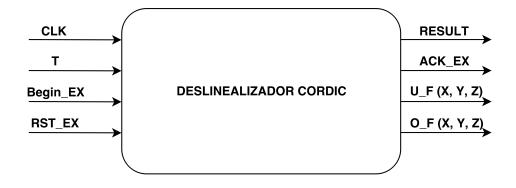

| 5.4        | Bloque de deslinealización: Entradas y salidas para el cálculo de la función                                                                                  |            |

|            | exponencial basada en el algoritmo de CORDIC e implementación en hard-                                                                                        | 44         |

| 5.5        | ware                                                                                                                                                          | 44         |

|            | ple (32 bits) basado en el algoritmo de CORDIC y una máquina de estados                                                                                       |            |

|            | finita                                                                                                                                                        | 44         |

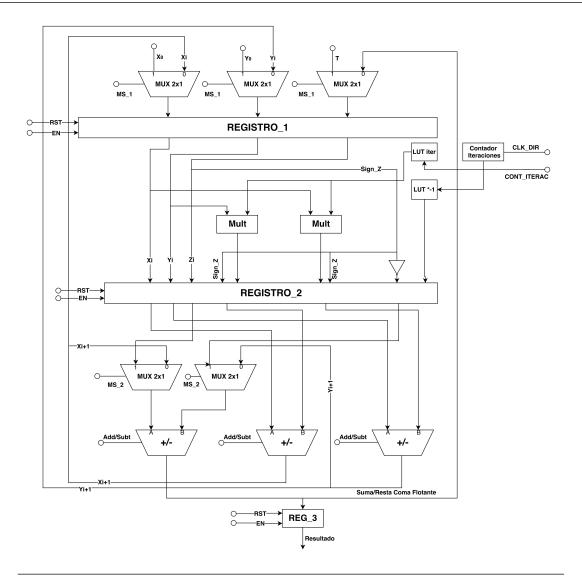

| 5.6        | Coprocesador segmentado para el cálculo de una función exponencial con                                                                                        |            |

|            | el algoritmo de CORDIC en hardware                                                                                                                            | 46         |

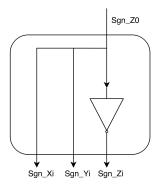

| 5.7        | Circuito de comparación de signo actual $\delta$ , para las variables $X_{i+1}$ , $Y_{i+1}$ y                                                                 | 4.0        |

| <b>F</b> 0 | $Z_{i+1}$ de la iteración siguiente, utilizando la tabla 5.3                                                                                                  | 48         |

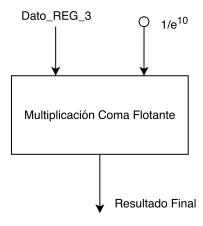

| 5.8        | Esquema ideado incluyendo la multiplicación para determinar el cálculo de                                                                                     | 40         |

| F 0        | la función exponencial                                                                                                                                        | 49         |

| 5.9        | Coprocesador segmentado modificado para el cálculo de una función expo-                                                                                       | <b>E</b> O |

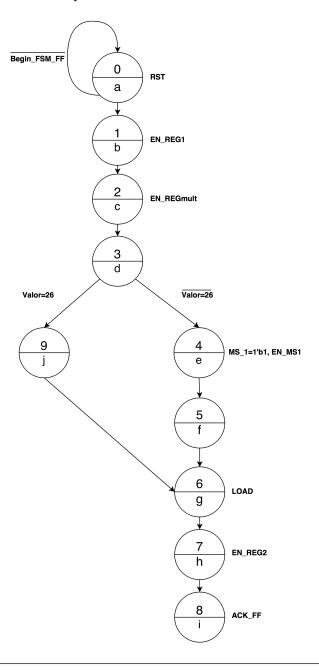

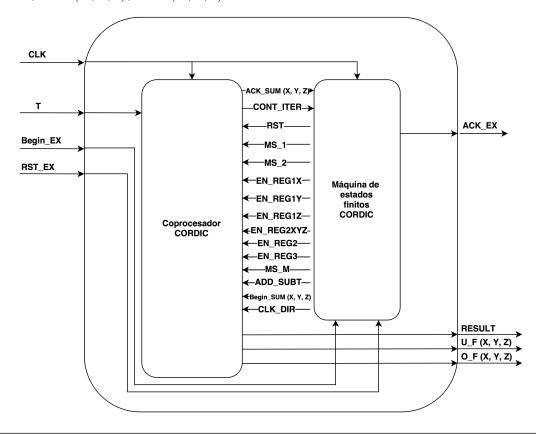

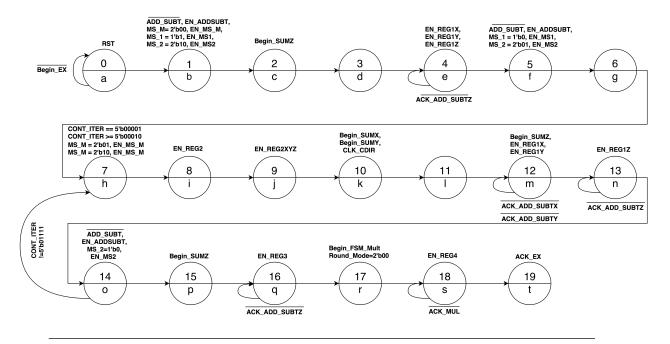

| 5 10       | nencial con el algoritmo de CORDIC para el parámetro $\theta_2 = \ln(I_s)$                                                                                    | 50<br>51   |

|            | Máquina de estados finitos para la unidad de coprocesamiento CORDIC Algoritmo de CORDIC en Python con expansión del rango de convergencia                     | 51         |

| 5.11       | con siete iteraciones negativas                                                                                                                               | 52         |

| 5 19       | Coprocesador segmentado con reducción de hardware para el cálculo de                                                                                          | 02         |

| 0.12       | una función exponencial con el algoritmo de CORDIC                                                                                                            | 53         |

| 5 13       | Máquina de estados finitos para la unidad de coprocesamiento CORDIC                                                                                           | 53         |

|            | Esquema general para la comprobación de datos del sistema de deslineal-                                                                                       | 99         |

| 0.14       | ización                                                                                                                                                       | 54         |

| 5 15       | Simulación de la arquitectura modificada implementada en Verilog, ingre-                                                                                      | 94         |

| 5.10       | sando un archivo de texto, con 1000 valores del intervalo de convergencia                                                                                     |            |

|            | para $\theta_2$                                                                                                                                               | 54         |

|            | range 2                                                                                                                                                       | J 1        |

Índice de figuras v

| 5.16 | Simulación de la arquitectura reducida implementada en Verilog, ingresando un archivo de texto, con 1000 valores del intervalo de convergencia                                                                   |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | r · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                          | 54 |

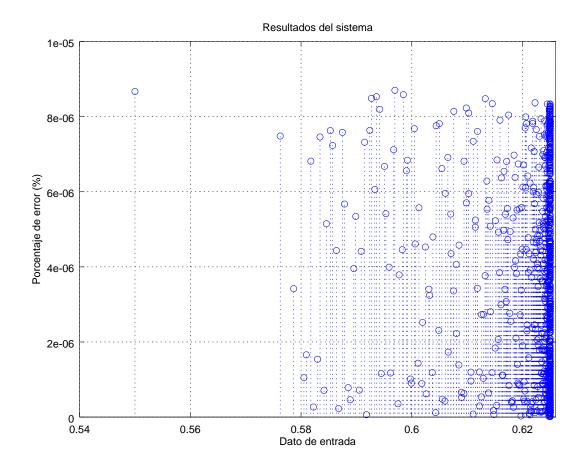

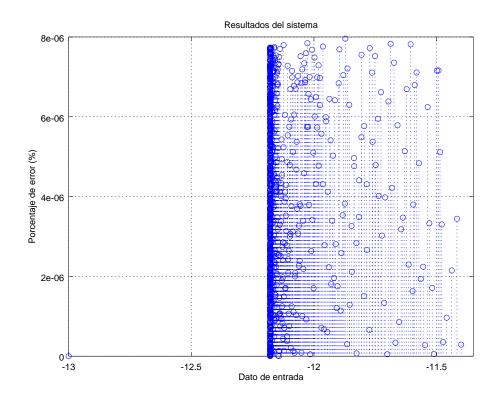

| 5.17 | del deslinealizador, tomando mil valores de entrada dentro del rango de                                                                                                                                          | 55 |

| 5.18 |                                                                                                                                                                                                                  | JJ |

| 0.10 | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                            | 56 |

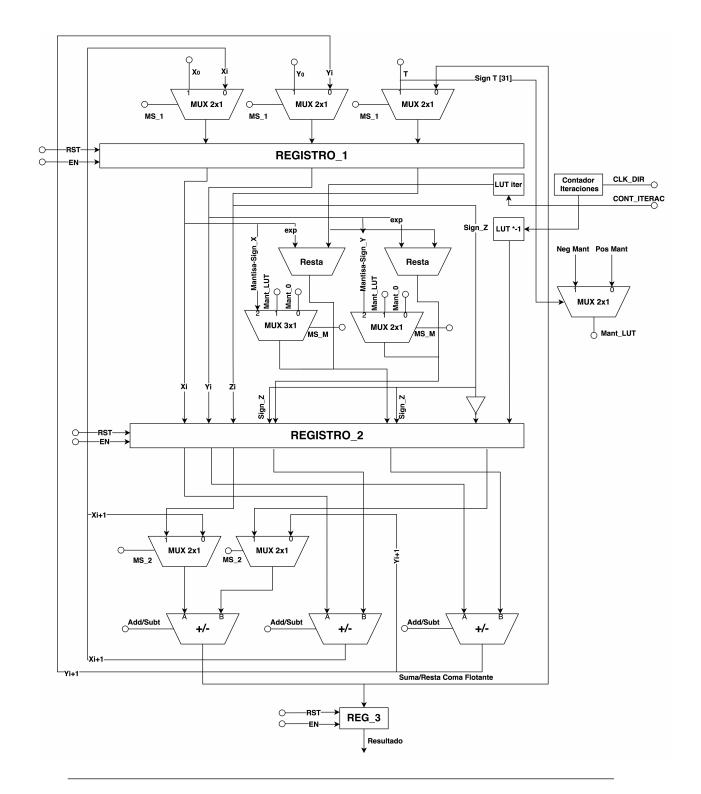

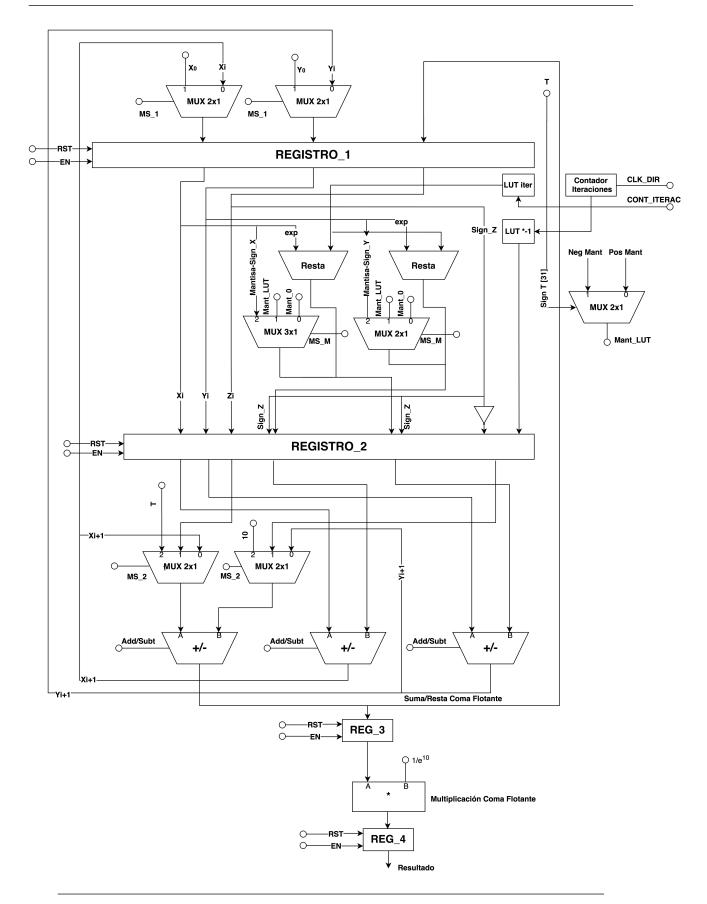

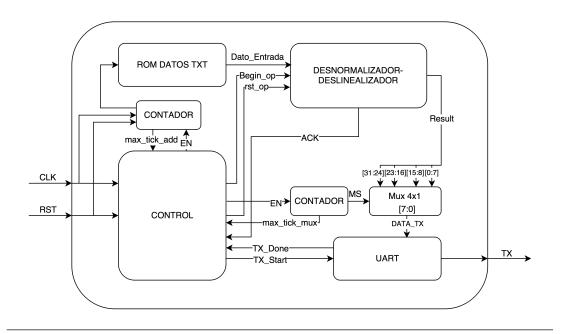

| 6.1  | Unidad general del sistema conversión - desnormalización y deslinealización                                                                                                                                      |    |

|      | •                                                                                                                                                                                                                | 57 |

| 6.2  | Unidad general completa que contiene los sistemas de conversión coma fija a coma flotante y deslinealización                                                                                                     | 58 |

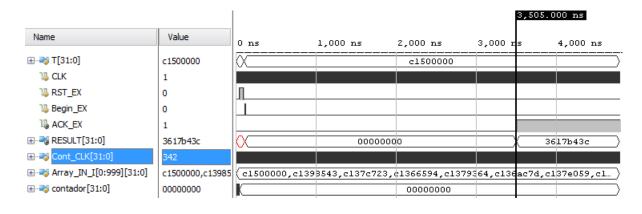

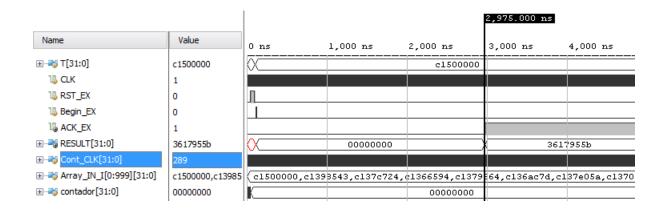

| 6.3  | Simulación de la unidad completa para un modelo de estimación de parámetros                                                                                                                                      | 59 |

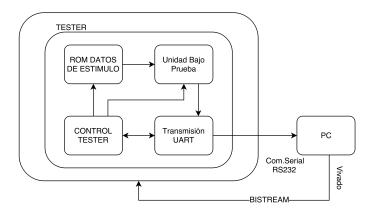

| 6.4  | Diagrama de flujo general para el ambiente de verificación utilizado en la FPGA, utilizando un tester con una memoria ROM para los vectores de entrada y una UART para la transmisión de los resultados hacia el |    |

|      | computador                                                                                                                                                                                                       | 60 |

| 6.5  | Detalle del ambiente de verificación ingresando los datos de estímulo por medio de una memoria ROM y enviando los datos de salida por medio de                                                                   |    |

|      | transmisión serial (UART) desde la Nexys $4$ hacia un computador $\ .\ .\ .\ .$                                                                                                                                  | 60 |

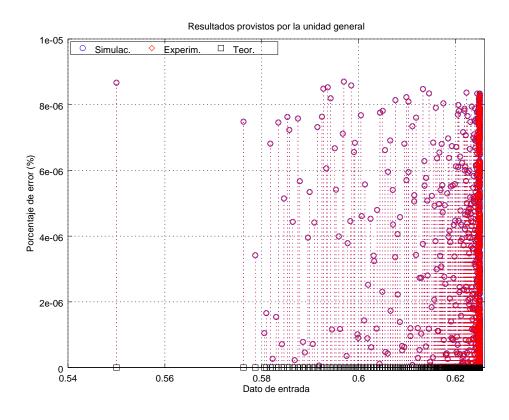

| 6.6  | Porcentaje de error para la conversión-desnormalización de $\alpha$ obtenido mediante el sistema de verificación                                                                                                 | 62 |

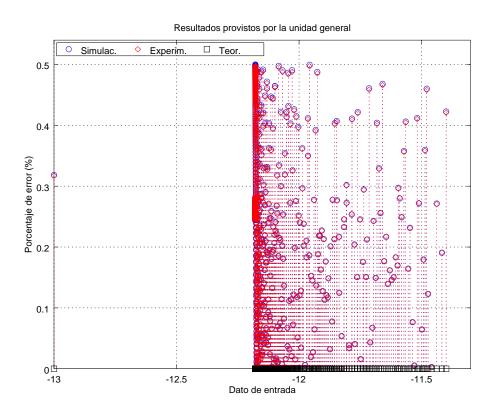

| 6.7  | Porcentaje de error para la conversión-desnormalización/deslinealización                                                                                                                                         |    |

|      | de $I_s$ obtenido mediante el sistema de verificación                                                                                                                                                            | 63 |

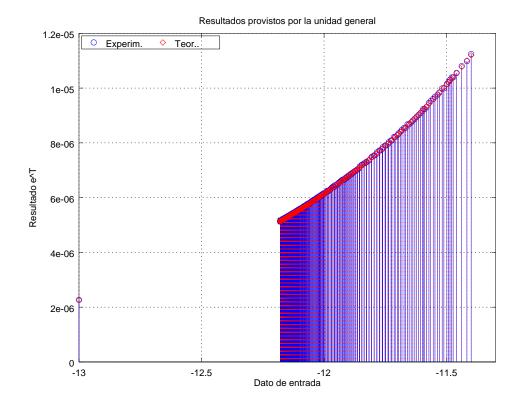

| 6.8  | Resultado de la conversión-des<br>normalización/deslinealización para ${\cal I}_s$ obtenido                                                                                                                      | 64 |

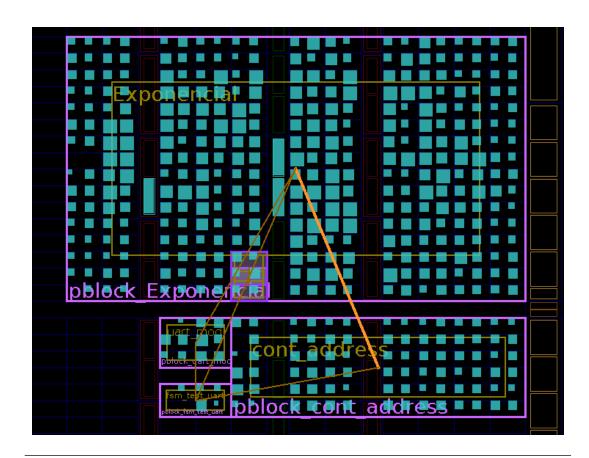

| 7.1  | Floorplanning realizado para ambas unidades                                                                                                                                                                      | 69 |

## Índice de tablas

| 2.1                               | Modelos para un PV: ideal, con perdidas en serie $R_s$ y con perdidas en paralelo $R_p$                                                                                                                                                                                           | 9        |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2<br>2.3                        | Sistema de coordenadas unificado (CORDIC): circular, lineal e hiperbólico. [4] Valores de $\chi_{max}$ con el algoritmo hiperbólico extendido                                                                                                                                     | 16<br>19 |

| 3.1                               | Especificaciones del comportamiento eléctrico del panel fotovoltaico KC65T, bajo condiciones estándar de prueba (STC) [5]                                                                                                                                                         | 21       |

| 3.2                               | Parámetros considerados para la simulación del estimador para un tiempo reducido                                                                                                                                                                                                  | 25       |

| 3.3                               | reducido                                                                                                                                                                                                                                                                          | 27       |

| 4.1                               | Resultados experimentales obtenidos de la simulación post-implementación, para los valores de entrada $\alpha$ y $\ln I_s$ , presentes en el circuito de conversión-desnormalización                                                                                              | 38       |

| 5.1<br>5.2                        | Cálculo de las primeras dos iteraciones negativas para $e^{-3}$                                                                                                                                                                                                                   | 43<br>43 |

| <ul><li>5.3</li><li>5.4</li></ul> | Signo $\delta$ de la iteración siguiente para las variables $X_{i+1}$ , $Y_{i+1}$ y $Z_{i+1}$ , comparando el signo de las variables $X_i$ , $Y_i$ y $Z_i$ contra el signo de $Z_i$ Resultados experimentales obtenidos por medio de una simulación postimplementación para $I_s$ | 47<br>55 |

| 6.1                               | Comparación de resultados de simulación vs experimentales de $\alpha$ obtenidos por el sistema de verificación implementado en una placa de desarrollo Nexys 4. El funcionamiento en la FPGA es por tanto correcto al 100% contra el modelo                                       | 63       |

| 6.2                               | Comparación de resultados de simulación vs experimentales de $I_s$ obtenidos por el sistema de verificación implementado en una placa de desarrollo Nexys 4. El funcionamiento en la FPGA es por tanto correcto al $100\%$                                                        | 61       |

| 6.3                               | contra el modelo                                                                                                                                                                                                                                                                  | 64       |

| 6 1                               | por la herramienta Vivado                                                                                                                                                                                                                                                         | 65       |

| 6.4                               | Resumen del reporte post implementación de tiempos del circuito completo, a partir de la herramienta Vivado. CLK=100 MHz                                                                                                                                                          | 66       |

Índice de tablas vii

| 6.5 | Resumen del reporte post implementación de la potencia estática, dinámica |    |

|-----|---------------------------------------------------------------------------|----|

|     | y total, de la herramienta Vivado para la unidad general                  | 66 |

| 6.6 | Resumen del reporte generado por la herramienta Vivado que indica el      |    |

|     | consumo de potencia de diversos elementos.                                | 67 |

## Capítulo 1

#### Introducción

#### 1.1 Entorno del proyecto

Actualmente a nivel mundial el impacto de las energías renovables se encuentra en un constante crecimiento y dentro de ellas, la mayoría viene generada por medios indirectos o directos del sol. La energía solar es usualmente utilizada para ser convertida en electricidad por medio de paneles fotovoltaicos, cuyo principio de funcionamiento proviene de sus materiales semiconductores de construcción [6]. Nuestro país no escapa a este fenómeno y es por esto que actualmente ha aumentado el uso de los mismos de manera drástica, basado en el hecho de que estos brindan múltiples beneficios en una gran cantidad de sectores debido a su fiabilidad y versatilidad [7].

Los sistemas fotovoltaicos requieren de diversos componentes, entre los que se pueden citar: paneles solares, acumuladores de energía, inversores de onda sinusoidal, protectores de sobretensión y reguladores [8]; no obstante, estos no cuentan con un mecanismo que permita adecuar la tensión para operar constantemente en el punto de máxima potencia, por lo que este varía por efectos de las magnitudes eléctricas de la corriente y la tensión con respecto a la temperatura e irradiancia del medio en el que se encuentra, de manera que si la tensión varía, la potencia asociada a esa tensión también lo hace. El rendimiento de un panel fotovoltaico está estrictamente relacionado a la eficiencia de convertir luz solar en electricidad; sin embargo, no toda la luz es ciertamente aprovechada por el material del que se encuentra constituido; típicamente la eficiencia se sitúa en un 15%, cercano a un sexto de la luz incidente en las celdas [9] [10].

El objetivo principal se centra en buscar el punto de tensión donde se obtenga la máxima potencia por lo cual es importante aprovechar las mejores condiciones ambientales presentes con un sistema capaz de controlar más eficientemente la energía.

El diseño realizado tanto del modelo como de las unidades presentes en esta tesis se basará en las características eléctricas de operación de un panel previamente escogido: KC65T Kyocera Solar [5]. El Laboratorio de Diseño de Circuitos Integrados [DCILab] (Instituto Tecnológico de Costa Rica) ya cuenta con una pequeña incursión en este problema [11], donde se dio la aproximación general del sistema total requerido para cumplir con tal objetivo. Este mismo no fue concluido de manera total, por lo que se requiere el diseño de las unidades restantes.

#### 1.2 Descripción del problema y justificación

El principal motivo del desarrollo de esta tesis surge debido a la falta de un modelo práctico para estimar parámetros que sea capaz de aproximar los valores de corriente de saturación y voltaje térmico necesarios para aproximar el punto de potencia máximo de un panel. Debido a que este estimador será implementado en un lenguaje de descripción de hardware, idealmente en formato coma fija con una linealización previa, es necesario crear un par de unidades que sean capaces tanto de convertir datos a formato coma flotante, como también deslinealizarlos.

La aproximación de parámetros se da con base en los datos de las curvas características de  $I_{pv} - V_{pv}$  y  $P_{pv} - V_{pv}$  de una celda solar. Sin embargo, la corriente  $I_{pv}$  no tiene un comportamiento lineal, por lo que en [11] se dió el trabajo necesario para linealizar y normalizar los datos para que en un desarrollo futuro del estimador este sea capaz de procesarlos.

La deslinealización depende de las operaciones aritméticas en coma flotante suma y multiplicación. En este aspecto el DCILab ya tiene un mínimo de experiencia en el desarrollo de las mismas ([12][13]).

Los siguientes requerimientos serán contemplados como parte de la solución:

- El deslinealizador se deberá basar en el estándar IEEE 754 (coma flotante).

- Utilización de arquitecturas de 32 bits.

- Utilizar Verilog como lenguaje de descripción de hardware y el software suite Vivado (Xilinx).

- Optimización de las unidades para requerir la menor cantidad de recursos y menor tiempo de ejecución.

- Utilización de lenguajes de alto nivel para determinar la fiabilidad de las unidades.

#### 1.3 Síntesis del problema

¿Cómo implementar las unidades de desnormalización y deslinealización en un lenguaje de descripción de hardware de manera que permita optimizar la eficiencia de paneles fotovoltaicos?

#### 1.4 Meta

Desarrollar un sistema en un lenguaje de descripción de hardware que logre incrementar sustancialmente la eficiencia de un panel fotovoltaico, el cual permita seguir impulsando de manera paulatina la utilización de energías limpias en una amplia cantidad de sectores.

#### 1.5 Objetivos

#### 1.5.1 Objetivo general

Desarrollar las unidades de desnormalización y deslinealización para un estimador de parámetros corriente (I)-tensión (V) de un panel fotovoltaico.

#### 1.5.2 Objetivos específicos

- Desarollar un modelo en un lenguaje de alto nivel del comportamiento del algoritmo estimador de parámetros, con predicción de la dinámica de  $\hat{\theta}_1 = \alpha$  y  $\hat{\theta}_2 = \ln(I_s)$ . Indicador: obtener la dinámica de la trayectoria de los parámetros en la fase plana y alcance del equilibrio con al menos una precisión del 95%.

- Crear un circuito de desnormalización para los parámetros  $\hat{\theta_1}$  y  $\hat{\theta_2}$  en coma fija, a la salida del estimador de parámetros.

Indicador: Verificar mediante un programa de alto nivel la precisión del desnormalizador con un error menor al 5%.

- Crear un circuito capaz de convertir de coma fija a coma flotante, las salidas θ<sub>1</sub> y θ<sub>2</sub> del desnormalizador.

Indicador: Verificar mediante un programa de alto nivel la precisión del convertidor con un error menor al 5%.

- Crear un circuito que deslinealice el parámetro  $\theta_2$ , por medio de una operación exponencial, para obtener como parámetro de salida  $I_s$ .

Indicador: Verificar mediante un programa de alto nivel la precisión del algoritmo implementado con un error menor al 5%.

- Integrar las unidades de desnormalización y deslinealización creadas con el estimador de parámetros, para determinar el funcionamiento del sistema.

Indicador: Comprobar que las unidades presentan un error de 0 % al ser interconectadas y que la precisión de los algoritmos se mantenga con un error menor al 5%.

#### 1.6 Enfoque de la solución

Se determinarán primeramente las curvas características y modelos de un panel fotovoltaico, debido a que son el fundamento de la estimación de parámetros. Para ello se desarrollará un modelo teórico de todo el sistema en un programa de alto nivel, específicamente en Python. Se investigarán temas tales como: estándar IEEE 754, representación binaria en coma fija y aspectos relacionados al algoritmo de CORDIC. Se seguirá una metodología de diseño Top-Down, para diseño y simulación de sistemas digitales:

- Definición de la interfaz de entrada-salida de cada una de las unidades, con una descripción funcional de la operación en conjunto.

- Creación de una estrategia factible de conexión entre bloques.

- Descripción mediante una herramienta EDA, en este caso Vivado (Xilinx), con el lenguaje de descripción de hardware Verilog. Esto para obtener una correspondiente simulación y verificación funcional antes de su posterior implementación.

- Comparación de resultados de la implementación del diseño en un dispositivo programable FPGA Nexys 4 contra resultados obtenidos mediante herramientas de software como Python y GNU Octave.

Todo esto formará parte del sistema general el cuál se muestra en la figura 1.1, en el que se desarrollarán los bloques enmarcados.

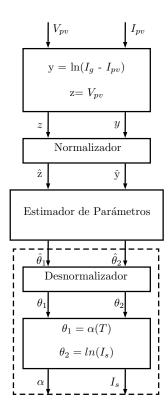

**Figura 1.1:** Diagrama de solución para el sistema completo de aumento de eficiencia energética en un panel fotovoltaico.

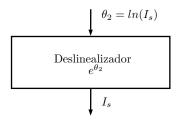

**Figura 1.2:** Diagrama de solución para el sistema de desnormalización y deslinealización, con entradas  $\hat{\theta_1}$  -  $\hat{\theta_2}$  en coma fija-normalizadas y salidas  $\alpha$  -  $I_s$  en coma flotante-desnormalizadas.

#### 1.7 Estructura

El capítulo 2 muestra la información que será utilizada a lo largo de la tesis y que fundamentará los conceptos básicos de los que se hacen uso. En el capítulo 3 se desarrollará el modelo teórico del estimador de parámetros, a través de simulaciones en un programa de alto nivel. En el capítulo 4 y 5 se da el desarrollo, implementación y comprobación del error de las unidades de conversión-desnormalización y deslinealización respectivamente. En el capitulo 6 se muestra una comprobación general de las unidades en la FPGA Nexys 4 y por último en el capítulo 7 se presentan las conclusiones y recomendaciones.

## Capítulo 2

#### Marco teórico

#### 2.1 Panel Fotovoltaico

Un panel fotovoltaico está compuesto por una gran cantidad de celdas solares, estas consisten en la unión de un par de capas delgadas conocida como junta p-n compuesta por materiales semiconductores no similares. Las capas n semiconductoras se encuentran hechas de silicón cristalino que es dopado con una cantidad pequeña de impurezas (fósforo, por ejemplo) para generar una gran cantidad de electrones libres. Igualmente las capas p son de silicón cristalino pero dopadas generalmente con boro, haciendo que esta tenga un déficit de electrones libres (huecos) [14].

Si la energía proveniente de la incidencia solar producida por un fotón es igual o mayor que la banda prohibida del semiconductor, esta hará que en la junta se dé una recombinación de electrones y huecos, de la capa n a la p y viceversa. Es por esto que se produce un efecto en el que se da una mayor cantidad de cargas positivas alrededor de la capa n semiconductora. Los semiconductores del panel, mayormente poseen un comportamiento exponencial y no lineal en sus regiones intrínsecas, contrario a las regiones extrínsecas [14].

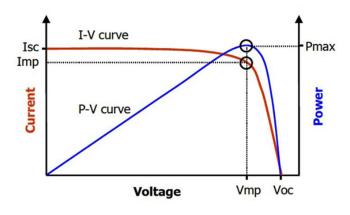

#### 2.1.1 Curvas Corriente-Tensión (I-V) para un PV

Un panel fotovoltaico produce su máxima corriente cuando no tiene ninguna resistencia en el circuito, es decir cuando existe un corto circuito en las terminales positiva y negativa. Esta corriente es generalmente conocida como corriente de corto circuito o  $I_{sc}$  y en este el voltaje en el circuito es de cero [15].

Contrario a  $I_{sc}$ , el voltaje máximo ocurre cuando no se tiene ninguna carga presente en el circuito. Este se conoce como voltaje de circuito abierto  $V_{oc}$  y bajo esta condición la resistencia es aproximada a infinito y no existe ninguna corriente circulante debido a que no se tiene ninguna carga presente [16].

Cuando se realiza la caracterización de un PV, se toman en consideración ambas pruebas debido a que la unión de ambas generará una curva de corriente-tensión que describirá el modelo eléctrico del panel. Esta caracterización es utilizada para determinar el rendimiento de un PV. La curva I-V se genera bajo condiciones estándar de prueba conocidas como STC, en la que se establece una determinada cantidad de irradiancia, generalmente  $1000 \ W/m^2$  y un valor de temperatura del dispositivo a 25 grados centígrados. [17]

**Figura 2.1:** Curva característica de corriente(A)-tensión(V) y potencia(P)-tensión(V) para un un panel fotovoltaico [1].

El punto de máxima potencia de un PV, puede ocurrir para una gran variedad de valores de corriente (I) y voltaje (V), al incrementar la carga resistiva desde el corto circuito  $I_{sc}$  hasta un valor muy alto cercano a circuito abierto  $V_{oc}$ , donde es posible determinar  $P_{max}$ , el punto en el que se genera la máxima salida eléctrica de potencia que la celda es capaz de proveer a un cierto nivel de irradiancia. Está se expresa como  $P_{max}=V_{max}$   $I_{max}$  [18]

#### 2.1.2 Modelo general del panel fotovoltaico

Un panel fotovoltaico se puede modelar utilizando una fuente de corriente en paralelo, un diodo, una resistencia paralela y una resistencia en serie, como se ejemplifica en la figura 2.2 [11].

En esta se incluyen las variables características del panel:

- Dependencia de la temperatura, corriente de saturación del diodo (Is) y foto-corriente (Ig).

- Pérdidas debidas al flujo de corriente (Rs) y pérdidas con referencia a tierra (Rp).

- Número de celdas en análisis n.

**Figura 2.2:** Modelo general para un panel fotovoltaico, compuesto por un diodo, una fuente de corriente y pérdidas resistivas por cada celda.

A partir de este modelo es posible deducir la ecuación que describe las corrientes  $i_{pv}$  e  $I_g$ , como sigue a continuación [11]:

$$i_{pv} = I_q - i_d + i_p \tag{2.1}$$

$$I_g = 2i_{pv} + \frac{v_{pv} + i_{pv}R_s}{R_p} - I_s + I_s e^{\frac{v_{pv} + i_{pv}v_{pv}}{nv_t}}$$

(2.2)

Despejando  $i_{pv}$

$$i_{pv} = \frac{1}{2} \left[ I_s + I_g - \frac{v_{pv} + i_{pv}R_s}{R_p} - I_s e^{\frac{v_{pv} + i_{pv}v_{pv}}{nv_t}} \right]$$

(2.3)

La corriente que fluye por las terminales de un generador fotovoltaico está determinada por tres funciones de corriente:

- Ig: Corriente generada debido al efecto fotoeléctrico.

- id: Corriente de pérdida debido a la juntura p-n.

- *ip*: Corriente de pérdida de naturaleza resistiva.

Las siguientes suposiciones se consideran para el comportamiento estático del generador fotovoltaico:

- Ig: depende de la irradiancia (S), pero no depende de la tensión en las terminales del generador fotovoltaico  $v_{pv}$ .

- ip e id: dependen de la tensión  $v_{pv}$ .

- *ip*: Depende de la temperatura (T).

De esta forma, la expresión que define  $i_{pv}$  es:

$$i_{pv}(v_{pv}, T, S) = i_g(v_{pv}) - i_d(v_{pv}, T)$$

(2.4)

Según se definan las funciones  $i_{pv}$  e  $i_d$ , se obtendrán modelos con complejidad y precisiones distintas, a partir de los casos enumerados en la tabla 2.1

**Tabla 2.1:** Modelos para un PV: ideal, con pérdidas en serie  $R_s$  y con pérdidas en paralelo  $R_p$

| Modelos | $i_g$ | $i_p$                         | $i_d$                                                              |

|---------|-------|-------------------------------|--------------------------------------------------------------------|

| 1       | KS    | -                             | $I_s\left(T\right)\left[e^{rac{V_{pv}}{v_t}}-1\right]$            |

| 2       | KS    | $G_pV_{pv}$                   | $I_s\left(T\right)\left[e^{rac{V_{pv}}{v_t}}-1\right]$            |

| 3       | KS    | -                             | $I_s\left(T\right)\left[e^{\frac{V_{pv}+i_{pv}R_s}{v_t}}-1\right]$ |

| 4       | KS    | $G_p V_{pv} + G_p i_{pv} R_s$ | $I_s\left(T\right)\left[e^{\frac{V_{pv}+i_{pv}R_s}{v_t}}-1\right]$ |

De manera general se tiene para el modelo general del comportamiento estático de un generador PV:

$$i_{pv}(v_{pv}) = KS - G_p v_{pv} - G_p i_{pv} R_s - i_d$$

(2.5)

$$i_{pv} = KS - G_p v_{pv} + I_s (T) - G_p i_{pv} R_s - I_s (T) e^{\frac{v_{pv}}{v_t}} e^{\frac{i_{pv} R_s}{v_t}}$$

(2.6)

#### 2.2 Modelo de estimación

Para propósitos del modelo del panel fotovoltaico se considera al mismo como un sistema de dos puertos, de donde se conocen sus magnitudes eléctricas: corriente circulante a través del dispositivo  $i_{pv}$  y tensión en sus terminales  $v_{pv}$ , respectivamente. Estas se encuentran asociadas por una función no lineal dependiente de los parámetros de temperatura T e irradiación solar S. Del panel se conocen también un set de parámetros  $\rho = (\rho_1, \rho_2, ..., \rho_n)$  asociados a los materiales de fabricación empleados. La cantidad de n dependerá del número de componentes utilizados en la creación del panel [19], [20], [21], [22].

En la mayoría de caracterizaciones de paneles, la relación entre la corriente y tensión,  $i_{pv}$  y  $v_{pv}$ , está representada por

$$i_{pv} = \xi(S, T, \rho) - \varphi(S, T, v_{pv}, \rho) \tag{2.7}$$

con  $\xi(\cdot) \geq 0$  y  $\varphi(\cdot) \geq 0$  funciones dependientes de la tecnología del panel.

La ecuación (2.7) para un gran cantidad de paneles fotovoltaicos (mono y policristalinos) [19] puede ser aproximada a:

$$i_{pv} = \xi(S, \rho) - \varphi_1(S, v_{pv}, i_{pv}, \rho) - \varphi_2(T, v_{pv}, i_{pv}, \rho)$$

(2.8)

donde efectivamente se separa la ecuación para establecer la relación directa a los parámetros de temperatura e irradiación solar  $(T \ y \ S)$ . Sin embargo es posible simplificar la ecuación 2.8 considerando el caso en el que

$$\varphi_2(T, v_{pv}, i_{pv}, \rho) = \Psi(T, \rho)e^{\alpha(T, \rho)z(\rho, v_{pv}, i_{pv})}$$

(2.9)

con  $\Psi$  y  $\alpha$  dependientes de la temperatura y  $\rho$ . Z es una nueva variable introducida y está estrictamente relacionada a  $\rho$ ,  $v_{pv}$  e  $i_{pv}$ . Se puede reescribir la ecuación (2.8) en una manera más sencilla

$$y(S, \rho, i_{pv}, v_{pv}) = \theta_1(T, \rho)z(i_{pv}, v_{pv}, \rho) + \theta_2(T, \rho)$$

(2.10)

donde

$$y = ln(\xi(S, \rho) - i_{pv} - \varphi_1(S, v_{pv}, i_{pv}, \rho))$$

(2.11)

$$\theta_1 = \alpha(T, \rho) \quad \theta_2 = \ln(\Psi(T, \rho))$$

(2.12)

Un modelo simple de estimación puede plantearse para obtener los valores de  $\theta_1$  y  $\theta_2$  a partir de las relaciones dadas por las ecuaciones anteriores y la tabla 2.1. Se deduce del modelo eléctrico de un panel fotovoltaico que cuenta con un único diodo y una resistencia serie, que su corriente  $i_{pv}$  está dada en términos de

$$i_{pv} = I_q(S) + I_s(T) - I_s(T)e^{\alpha(T)V_{pv}}$$

(2.13)

A partir de esta relación, se puede obtener mediante una linealización con  $I_g \gg I_s$

$$ln(I_s(T)e^{\alpha(T)v_{pv}}) = ln(I_g(S) - i_{pv})$$

(2.14)

$$\alpha V_{pv} + ln(I_s) = ln(I_g - i_{pv}) \tag{2.15}$$

con

$$y = \alpha V_{pv} + \ln(I_s) \tag{2.16}$$

Una vez que el estimador es capaz de determinar los parámetros necesarios, la ecuación 2.17 se mantiene constante en un plano de fases [19] [23].

$$y = \theta_1 z + \theta_2 = \hat{\theta}_1 z + \hat{\theta}_2 \tag{2.17}$$

#### 2.3 Estándar IEEE 754

El estándar IEEE754 coma flotante es una de las representaciones más comunes para números reales en diversa variedad de sistemas computacionales hoy en día. Este estándar permite representar un número por medio del uso de la notación científica, con un número base y un exponente [24], [25]. La representación de un dato en coma flotante para un número real está representado por tres partes principales: signo, exponente y mantisa (número normalizado en notación científica), de la forma:

$$(-1)^{signo} \cdot b^{exponente} \cdot mantisa(significando)$$

Esta representación posee un 1 bit de signo, 8 bits de exponente y 23 bits de mantisa para precisión simple (32 bits), donde valores de 0 y 1 en el signo representan valores positivos y negativos respectivamente [26]. El exponente necesita representar tanto exponentes positivos como negativos, un valor de bias es añadido con tal de obtener un valor adecuado en flotante, generalmente para el estándar en precisión simple se encuentra definido en 127, por lo tanto el rango original de -126 a +127 con la suma del bias puede variar el rango desde 1 hasta 254 (los valores de 0 y 255 poseen valores especiales en este formato) [27].

La mantisa o significando representa la precisión del número y está compuesto por un bit implícito (a la izquierda de la coma flotante) y los bits de precisión a la derecha de este, típicamente los valores son guardados en su forma normalizada.

#### 2.4 Formato de representación binaria coma fija

La mayoría de computadoras poseen soporte para números en formato coma flotante, sin embargo, esta no es la única representación que existe para números fraccionales. La representación binaria coma fija tiene un conocido uso en el procesamiento digital de señales (DSP) y diversidad de aplicaciones donde se considera más importante el rendimiento que la precisión. La aritmética de coma fija se considera mucho más veloz que la de coma flotante ya que permite realizar operaciones con un comportamiento similar al de un número entero [28].

La ventaja que posee es que permite conversiones sumamente veloces e inmediatas, con la desventaja en el rango o dominio en comparación con la notación científica, además de que las operaciones tienden a perder precisión por redondeo. La representación fraccional de un número posee el concepto de una coma binaria el cual es similar a cuando se habla de coma decimal bajo un sistema decimal, éste actúa como un divisor entre la parte entera y la parte fraccional. Para representar un número binario en coma fija se necesita definir un valor o posición donde se encontrará, para esto se necesita definir al menos dos parámetros:

- Tamaño de la representación numeral.

- Posición de la coma binaria dentro del número.

El esquema general para representar un número en binario punto fijo se define como

$$Signo-Magnitud-Fraccional$$

A excepción del signo  $(tama\tilde{n}o=1)$ , la magnitud y la parte fraccional pueden ser modificadas a discreción para representar un rango adecuado según la aplicación que se ejecute.

#### 2.4.1 Representación de números negativos

Debido a que se pueden encontrar números negativos en este formato, es necesario expresarlos en una forma adecuada. La representación del complemento a dos del número es la manera más común de hacerlo. Una de las propiedades de este complemento es que las operaciones aritméticas de suma y resta de números positivos o negativos son idénticas, esto incluye también al desplazamiento. Incluso, es posible dividir números negativos representados en complemento a dos con un simple desplazamiento a la derecha de 1 bit con extensión de signo, al igual que como se hace con los números positivos [28].

#### 2.5 Algoritmo de CORDIC

Coordinate Rotational Digital Computer (CORDIC) es un algoritmo simple y eficiente de iteraciones básicas, que se clasifica generalmente como uno de los algoritmos de la clase desplazamiento y suma (shift and add), donde se genera un método de rotación de vectores con el fin de calcular un valor numérico deseado. La variedad de usos es sumamente amplia, entre los que se puede encontrar: funciones trigonométricas, logarítmicas, exponenciales, procesamiento digital de señales, transformada discreta de Fourier y transformadas discretas de Hartley [29].

Este algoritmo no es precisamente una de las técnicas más rápidas para implementar todas las funciones anteriormente descritas; sin embargo, debido a su simplicidad de hardware, es ampliamente utilizado, por ser muy eficiente en términos de potencia y complejidad [30]. CORDIC ofrece una solución a los problemas de recursos en hardware, generalmente en recursos como multiplicación, donde puede ser reemplazada por sumadores y *shifters*.

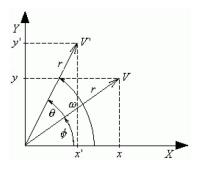

El algoritmo en su forma original [31] describe la rotación de un vector bidimensional en el plano cartesiano, como el mostrado en la Figura 2.3. El funcionamiento del algoritmo se deduce de la formula general de rotación de vectores [32]

$$x' = x\cos\theta - y\sin\theta$$

$$y' = y\cos\theta + x\sin\theta$$

(2.18)

Figura 2.3: Vector bidimensional antes y después de ser rotado. [2]

Se puede asumir que  $cos\theta \neq 0$  y simplificando la ecuación 2.18, se obtiene [32]

$$x' = \cos\theta(x - y \tan\theta)$$

$$y' = \cos\theta(y + x \tan\theta)$$

(2.19)

Se puede reexpresar  $\cos\theta$  como:

$$\cos\theta = \frac{1}{\sqrt{1 + \tan^2\theta}} \tag{2.20}$$

lo que deriva en

$$x' = \frac{x - y \tan \theta}{\sqrt{1 + \tan^2 \theta}}$$

$$y' = \frac{y + x \tan \theta}{\sqrt{1 + \tan^2 \theta}}$$

(2.21)

Las rotaciones pueden ser substituidas por pseudorotaciones vectoriales como se muestra en la figura 2.4.

Figura 2.4: Pseudorotación de un vector bidimensional. [3]

En una rotación real no se cambia la magnitud del vector V una vez realizada la rotación, pero en una pseudorotación esto no aplica, ya que incrementa su magnitud en

$$V'' = V\sqrt{1 + \tan^2\theta} \tag{2.22}$$

La rotación puede ser descompuesta en una sumatoria de rotaciones más pequeñas. Suponiendo inicialmente que  $x = x_0$ ,  $y = y_0$  y  $z = z_0$ , después de realizadas n iteraciones para una rotación real, se obtiene que

$$x'_{n} = x \cos \theta (\sum_{i=0}^{n-1} \theta_{i}) - y \sin \theta (\sum_{i=0}^{n-1} \theta_{i})$$

(2.23)

$$y_n' = y\cos\theta(\sum_{i=0}^{n-1}\theta_i) + x\sin\theta(\sum_{i=0}^{n-1}\theta_i)$$

(2.24)

$$z_n' = z - (\sum_{i=0}^{n-1} \theta_i) \tag{2.25}$$

Para una pseudorotación se tiene que

$$x_n'' = (x\cos\theta(\sum_{i=0}^{n-1}\theta_i) - y\sin\theta(\sum_{i=0}^{n-1}\theta_i)) \prod_{i=0}^{n-1} \sqrt{1 + \tan^2\theta_i}$$

(2.26)

$$y_n'' = (y\cos\theta(\sum_{i=0}^{n-1}\theta_i) + x\sin\theta(\sum_{i=0}^{n-1}\theta_i)) \prod_{i=0}^{n-1} \sqrt{1 + \tan^2\theta_i}$$

(2.27)

$$z_n'' = z - (\sum_{i=0}^{n-1} \theta_i) \quad con \quad (\sum_{i=0}^{n-1} \theta_i) = \theta$$

(2.28)

Las ecuaciones (2.25) y (2.28) son referidas como el parámetro acumulador angular y contienen la rotación parcial realizada.

Para poder hacer un cambio de la operación multiplicación por una de desplazamiento se restringe la rotación de manera que  $tan\theta = \pm 2^{-i}, i \in N$ , haciendo que se pueda reducir factores como área y tiempo a nivel computacional con esta consideración. Los cálculos se reducen a realizar rotaciones sucesivas de valores muy pequeños en cada iteración, pero únicamente se debe decidir en qué sentido se debe de rotar. Al sustituir la aproximación en la fórmula general de rotación de vectores (2.19) y sabiendo que una de las identidades del coseno es  $cos(\theta) = cos(-\theta)$ , la anterior ecuación se puede reescribir de manera tal que

$$x_{i+1} = K_i(x_i - y_i d_i 2^{-i})$$

$$y_{i+1} = K_i(y_i + x_i d_i 2^{-i})$$

(2.29)

donde  $K_i = \frac{1}{\sqrt{1+2^{-2i}}}$  y  $d_i = \pm 1$  depende del sentido de rotación [32].

$K_i$  es definido por las pseudorotaciones, ya que estas aumentan el tamaño del vector, por lo que este valor se encarga de eliminar un posible escalado. Una vez que  $K_i$  se remueve se tiene un algoritmo capaz de realizar cálculos a partir de sumas y desplazamientos. El factor  $K_i$  se aplica como constante  $K_n$  generalmente al inicio del proceso y el valor de la misma es determinada por la cantidad de iteraciones por realizar, definida como

$$K_n = \lim_{n \to \infty} \prod_{i=0}^{n} K_i \cong 0.607253 \tag{2.30}$$

El algoritmo define únicamente el sentido de rotación y cado ángulo tiene una representación adecuada mediante un vector de signo correspondiente a un ángulo de secuencia elemental. Los valores de los ángulos se almacenan en una Look-Up Table(LUT) y mediante esto es posible modificar el acumulador angular, de forma que

$$z_{i+1} = z_i - d_i \arctan(2^{-i}) (2.31)$$

Los métodos de operación del algoritmo pueden variar entre rotación o vectorización:

- Rotación: el acumulador angular comienza con un valor inicial de un ángulo y se realiza la decisión de sentido de rotación en cada iteración con el fin de minimizar la magnitud del ángulo a cero.

- Vectorización: el ángulo ingresado rota hasta alinearse con el eje X. Para esto se utiliza el signo de la variable y para definir el sentido de rotación.

Las ecuaciones iterativas para la rotación, son

$$x_{i+1} = x_i - y_i d_i 2^{-i}$$

$$y_{i+1} = y_i + x_i d_i 2^{-i}$$

$$z_{i+1} = z_i - d_i e(i)$$

(2.32)

donde,

$$d_i = \begin{cases} -1, z_i < 0 \\ +1, z_i \geqslant 0 \end{cases}$$

Las ecuaciones iterativas para la vectorización, son

Para el modo de *vectorización*, las ecuaciones iterativas son

$$x_{i+1} = x_i - y_i d_i 2^{-i}$$

$$y_{i+1} = y_i + x_i d_i 2^{-i}$$

$$z_{i+1} = z_i - d_i \arctan(2^{-i})$$

(2.33)

donde,

$$d_i = \begin{cases} -1, y_i \geqslant 0 \\ +1, y_i < 0 \end{cases}$$

Una manera general para expresar las ecuaciones 2.32 y 2.33 se resume como:

$$x_{i+1} = x_i - md_i 2^{-i} y_i (2.34)$$

$$y_{i+1} = y_i - d_i 2^{-i} x_i (2.35)$$

$$z_{i+1} = z_i - d_i \chi(i) \tag{2.36}$$

Donde  $\chi(i)$  se muestra en la tabla 2.3 según corresponde cada caso.

**Tabla 2.2:** Sistema de coordenadas unificado (CORDIC): circular, lineal e hiperbólico. [4]

| m  | Sistema de coordenadas | Valor de $\chi(i)$             |

|----|------------------------|--------------------------------|

| 1  | Circular               | $tan^{-1}(2^{-i})$             |

| 0  | Lineal                 | $2^{-1}$                       |

| -1 | Hiperbólico            | $tanh^{-1}\left(2^{-i}\right)$ |

#### 2.5.1 Sistema de coordenadas hiperbólico

Para el cálculo de algunas funciones con el algoritmo aumenta la complejidad, de manera que se deben utilizar las siguientes identidades [4]:

$$\tan z = \frac{\sin z}{\cos z} \tag{2.37}$$

$$tanh z = \frac{\sinh z}{\cosh z} \tag{2.38}$$

$$\exp z = \sinh z + \cosh z \tag{2.39}$$

$$\ln \omega = 2 \cdot \tanh^{-1} \left( \frac{y}{x} \right) \tag{2.40}$$

Donde

$$x = \omega + 1 \quad y = \omega - 1 \tag{2.41}$$

#### 2.5.2 Exponencial utilizando el algoritmo hiperbólico de COR-DIC

Para una función  $e^{\varphi}$ , con el algoritmo de CORDIC hiperbólico, se deben de utilizar las ecuaciones [29]

$$x_{i+1} = x_i + d_i 2^{-i} y_i (2.42)$$

$$y_{i+1} = y_i + d_i 2^{-i} x_i (2.43)$$

$$z_{i+1} = z_i - d_i \tanh^{-1} \left( 2^{-i} \right) \tag{2.44}$$

Los valores finales de x y y, representan el resultado de  $cosh(\varphi)$  y  $sinh(\varphi)$  respectivamente y que al ser sumados generan el valor del exponencial (vease la ecuación 2.39). Aquí, i es el índice de cada iteración (i=1,2,3,..N) y se debe tomar en cuenta la repetición de las iteraciones 4, 13, 40, ...k, 3k+1 para garantizar la convergencia dando una mejor precisión en el cálculo. El rango básico de convergencia del algoritmo se define mediante las siguientes ecuaciones [33] [34]

Modo Rotación:

$$|z_0| = \chi_N + (\sum_{i=1}^N \chi_i)$$

(2.45)

$$|z_0| = \tanh^{-1}(2^{-N}) + \sum_{i=1}^{N} \tanh^{-1}(2^{-N})$$

(2.46)

$$|z_0|_{max} \approx 1.182 \quad para \quad N \to \infty$$

(2.47)

Este es el dominio impuesto por el argumento de la función hiperbólica en el modo de rotación.

Modo Vectorización:

$$|tanh^{-1}(\frac{y_0}{x_0})| \le \chi_N + (\sum_{i=1}^N \chi_i)$$

(2.48)

$$|tanh^{-1}(\frac{y_0}{x_0})| \le 1.182 \quad para \quad N \to \infty$$

(2.49)

$$\left|\frac{y_0}{x_0}\right| \approx 0.80694 \quad para \quad N \to \infty$$

(2.50)

Este es el dominio impuesto por el argumento de la función hiperbólica en el modo de vectorización. El dominio de las funciones  $\tanh^{-1}$  es ]-1, +1[ [35]. Los valores iniciales para calcular la función exponencial se definen como constantes:  $x_0 = 1,20753406$ ,  $y_0 = 0$  y  $z_0 = \varphi$ , con  $\varphi$  como el valor del argumento que se desea calcular;  $d_i$  es el signo de  $z_i$ . El rango de convergencia para la función exponencial se puede definir como:

$$-1.12642 < \varphi < 1.12642 \tag{2.51}$$

#### 2.5.3 Expansión del rango de convergencia del algoritmo hiperbólico

El rango expresado en las ecuaciones 2.47 y 2.50 es insuficiente para realizar la mayoría de funciones que dependen de este algoritmo. Se propone un esquema para agregar iteraciones al cálculo y este consiste en introducir índices negativos en las mismas, modificando  $\chi(i)$ , de la forma [36]

$$\chi_i = \tanh^{-1}(1 - 2^{i-2}), para \quad i \le 0$$

(2.52)

Teniendo en cuenta esta consideración, las ecuaciones 2.42, 2.43 y 2.44 se pueden reescribir de manera que se tomen los índices negativos como [35]

$Para i \leq 0$

$$x_{i+1} = x_i + d_i(1 - 2^{i-2})y_i (2.53)$$

$$y_{i+1} = y_i + d_i(1 - 2^{i-2})x_i (2.54)$$

$$z_{i+1} = z_i - d_i \tanh^{-1}(1 - 2^{i-2})$$

(2.55)

Para i > 0

$$x_{i+1} = x_i + d_i 2^{-i} y_i (2.56)$$

$$y_{i+1} = y_i + d_i 2^{-i} x_i (2.57)$$

$$z_{i+1} = z_i - d_i \tanh^{-1} \left( 2^{-i} \right) \tag{2.58}$$

Esto produce la expansión de los valores máximos de  $z_0$  y el arcotangente de la relación  $\frac{y_0}{x_0}$  de modo en que se convierte cada uno en (-M: índices negativos):

$$|z_0| \le \chi_{max} \tag{2.59}$$

$$|tanh^{-1}(\frac{y_0}{x_0})| \le \chi_{max}$$

(2.60)

$$\chi_{max} = \sum_{i=-M}^{0} \tanh^{-1}(1 - 2^{i-2}) + \left[\tanh^{-1}(2^{-N}) + \sum_{i=1}^{N} \tanh^{-1}(2^{-i})\right]$$

(2.61)

**Tabla 2.3:** Valores de  $\chi_{max}$  con el algoritmo hiperbólico extendido.

| Μ  | $\chi_{max}$ |

|----|--------------|

| 0  | 2.09113      |

| 1  | 3.44515      |

| 2  | 5.16215      |

| 3  | 7.23371      |

| 4  | 9.65581      |

| 5  | 12.42644     |

| 6  | 15.54462     |

| 7  | 19.00987     |

| 8  | 22.82194     |

| 9  | 26.98070     |

| 10 | 31.48609     |

Por ejemplo, si M=1 (dos iteraciones negativas), el rango de  $\chi_{max}$  para las funciones cosh y sinh es expandido a [-3.44515, 3.44515] para la función exponencial, es decir [ $e^{-3.44515}$ ,  $e^{3.44515}$ ], obteniendo valores de [0.03189, 31.347989]. La función tanh con un M mayor hace que el dominio se expanda hasta prácticamente ]-1,+1[, el cuál es el dominio completo de esta función.

## Capítulo 3

## Modelo teórico del algoritmo estimador de parámetros

En este capítulo se describe el desarrollo de un algoritmo estimador que tiene como finalidad determinar los parámetros necesarios para calcular el punto de máxima potencia en un panel fotovoltaico. También se presenta la dinámica de los parámetros en la fase plana o plano de fase como parte de la solución matemática en un plano bidimensional  $(\theta_1, \theta_2)$ . El estimador está fundamentado en el uso del mismo para una gran variedad de tecnologías de paneles presentes en el mercado, pero ciertamente no es válido para todas ellas.

Este modelo parte de las investigaciones realizadas en [19] y [23], que demuestran el funcionamiento del estimador para un diagrama de un cargador de baterías (PVG Battery Charger) y un arreglo de paneles (PVG Full Bridge Inverter), respectivamente. Para la correspondiente verificación del sistema se genera un modelo en alto nivel, específicamente en Python, donde se describe el comportamiento esperado para un panel específico que a su vez simula la operación real bajo condiciones estándar de prueba.

#### 3.1 Estimación de parámetros

La estimación, capaz de aproximar los parámetros dependientes de la temperatura y los elementos característicos de un panel fotovoltaico, es necesaria para predecir el punto de máxima potencia sin hacer uso de algoritmos heurísticos MPPT (maximum power point tracker) [37] [38], los cuales requieren de condiciones de irradiancia y temperatura específicas lo que los hace más costosos y complejos. Mediante las siguientes ecuaciones es posible crear un método alternativo necesario para acelerar la búsqueda del punto máximo de potencia de un PV, se parte de las ecuaciones (2.10) a (2.16), las cuales pueden ser reducidas a

$$y = ln(I_q - i_{pv}) \quad z = v_{pv} \tag{3.1}$$

$$\theta_1 = \alpha(T) \quad \theta_2 = \ln(I_s) \tag{3.2}$$

Estas ecuaciones pueden sintetizarse en una única ecuación dada por:

$$y = \theta_1 z + \theta_2 \tag{3.3}$$

Se parte de los siguientes supuestos para la obtención de los parámetros  $\theta_1$  y  $\theta_2$ :

- $\bullet \ v_{pv}$ e  $i_{pv}$ son medidas y provienen del panel fotovoltaico.

- $\bullet$   $I_g$  (corriente de corto circuito) y S (irradiancia solar) son medidas.

- T (temperatura del medio) no se mide.

- $I_s$  y  $\alpha$  son desconocidos

Debido a que se necesita trabajar con datos lo más cercanos posibles a un modelo de panel fotovoltaico previamente escogido (Kyocera Solar KC65T [5]), es necesario generar un modelo en un lenguaje de alto nivel que represente las curvas I-V (corriente - tensión) y P-V (potencia - tensión) de manera adecuada, realizando una aproximación con los siguientes parámetros provistos por el fabricante según la tabla 3.2.

**Tabla 3.1:** Especificaciones del comportamiento eléctrico del panel fotovoltaico KC65T, bajo condiciones estándar de prueba (STC) [5].

| Parámetro                                        | Valor | Unidad |

|--------------------------------------------------|-------|--------|

| Potencia Máxima $(P_{max})$                      | 65.25 | W      |

| Voltaje a la Pot.<br>Máxima $(V_{mpp})$          | 17.4  | V      |

| Corriente a la Pot.<br>Máxima $(I_{mpp})$        | 3.75  | A      |

| Voltaje de circuito abierto $(V_{oc})$           | 21.7  | V      |

| Corriente de corto circuito $(I_{sc} \circ I_g)$ | 3.99  | A      |

| Máximo voltaje del sistema $(V_{max})$           | 600   | V      |

Se sabe que para un PV, el voltaje de circuito abierto  $V_{oc}$  representa el máximo voltaje que puede entregar una celda solar, cuando la corriente es cero [16]. El  $V_{oc}$  corresponde a la cantidad de polarización directa que permite polarizar la junta p-n. La ecuación típica del voltaje de circuito abierto está dada por:

$$V_{oc} = \frac{nkT}{q}\ln(\frac{I_g}{I_s} + 1) \tag{3.4}$$

La relación de  $V_{oc}$  en la ecuación (3.4), puede aproximarse a la ecuación (3.5) con  $I_g \gg I_s$ . Sin embargo, se necesita de al menos una aproximación inicial de uno de los valores a estimar, debido a que se tiene una única ecuación lineal con dos incógnitas. A razón de

ello, se crea una reducción a la mejor zona para obtener las curvas en el punto máximo de potencia, en un valor aproximado de  $\alpha$ =0.625.

$$V_{oc} = \frac{1}{\alpha} ln(\frac{I_g}{I_s}) \tag{3.5}$$

Mediante el valor aproximado para  $\alpha$  se puede determinar el otro parámetro desconocido,  $I_s$ , con un simple despeje

$$21.7 = \frac{1}{0.625} ln(\frac{3.99}{I_s}) \tag{3.6}$$

$$I_s = 5,1387085 \cdot 10^{-6} \tag{3.7}$$

Con el valor obtenido en la ecuación (3.7), el valor de  $\alpha$  y las siguientes relaciones, es posible graficar las curvas de la figura 3.1 las cuales representan que los valores aproximados de  $\theta_1$  y  $\theta_2$  son adecuados para obtener el máximo punto de potencia del panel.

- $i_{pv} = I_g I_s * e^{V_{oc} V_{test}}$  con restricción: si  $V_{oc}$   $V_{test} > (\frac{\ln(I_g) \ln(I_s)}{\alpha})$ ,  $i_{pv} = 0$ , ya que en ningún momento la tensión  $V_{oc}$   $V_{test}$  puede ser mayor que la tensión de circuito abierto  $v_{oc}$ .

- $V_{test}$  = muestras continuas que forman una función exponencial desde  $e^{ln(0.001)}$  hasta  $e^{ln(V_{pv})}$ .

- $P_{pv} = i_{pv} * (V_{oc} V_{test}) \text{ con } (V_{oc} V_{test}) = v_{pv}$ .

**Figura 3.1:** Gráficas *i-v* y *P-v* obtenidas con el modelo para el panel Kyocera Solar KC65T con parámetros  $\theta_1 = 0.625$  y  $\theta_2 = \ln(I_s) = -12.178$ .

Se puede entonces considerar la reescritura de la ecuación (3.3) en

$$y = \theta^T \Phi \tag{3.8}$$

Donde  $\Phi = \begin{bmatrix} V_{pv} & 1 \end{bmatrix}^T$ ,  $y = \ln(I_g - I_{pv})$  y  $\theta = \begin{bmatrix} \theta_1 & \theta_2 \end{bmatrix}^T$  representa los parámetros por estimar  $\theta_1 = \alpha$  y  $\theta_2 = \ln(I_s)$ .

En [19] [23], se definen las siguientes consideraciones y del mismo modo se toman como base para el desarrollo del modelo del estimador:

- $\hat{\theta} = \begin{bmatrix} \hat{\theta}_1 & \hat{\theta}_2 \end{bmatrix}^T$  definición de los valores una vez estimados.

- Estimador por implementar (Γ definida como una matriz de tamaño 2x2)

$$\dot{\hat{\theta}} = \Gamma \Phi (y - \Phi^T \hat{\theta}) \tag{3.9}$$

• Si se define el parámetro de error como  $\tilde{\theta} = \hat{\theta} - \theta$ , se puede reescribir (3.9) de la forma

$$\tilde{\dot{\theta}} = -\Gamma \Phi \Phi^T \tilde{\theta} \tag{3.10}$$

#### 3.2 Dinámica en la fase plana

Una vez definido el esquema sugerido en la ecuación (3.9), se define la matriz  $\Gamma$  cómo:

$$\Gamma = \begin{bmatrix} \gamma_{11} & \gamma_{12} \\ \gamma_{21} & \gamma_{22} \end{bmatrix}$$

Sus componentes  $\gamma_{ii}$  serán escogidos de manera que sean positivos. Debido a que el ajuste de los mismos es crítico en términos de comportamiento y rapidez de convergencia del estimador, se opta por crear una reducción a únicamente dos valores, los cuáles serán los elementos de la diagonal principal  $\gamma_{11}$  y  $\gamma_{22}$ , el par de valores restantes se establecen en un valor de cero, es decir  $\gamma_{12} = \gamma_{21} = 0$ .

Para representar de una mejor manera las ecuaciones que se introducen al modelo de alto nivel, se sintetiza la ecuación (3.9) para  $\dot{\hat{\theta_1}}$  y  $\dot{\hat{\theta_2}}$ , con  $\hat{y} = \hat{\theta_1}z + \hat{\theta_2}$  de la siguiente forma:

$$\dot{\hat{\theta}}_1 = (\gamma_{11}z + \gamma_{12})(y - \hat{y}) \tag{3.11}$$

$$\dot{\hat{\theta}}_2 = (\gamma_{21}z + \gamma_{22})(y - \hat{y}) \tag{3.12}$$

Una vez aplicada la reducción:

$$\dot{\hat{\theta}}_1 = (\gamma_{11}z)(y - \hat{y}) \tag{3.13}$$

$$\dot{\hat{\theta}}_2 = (\gamma_{22})(y - \hat{y}) \tag{3.14}$$

Adicionalmente para poder graficar la respuesta del estimador se debe de considerar:

- $v_{pv} = v_{pv}^- + 0.3v_{pv}^- \sin(200 * \pi * t)$  (tensión de excitación permanente en estado estable).

- $y=\alpha v_{pv} + \ln I_s$  de la ecuación 2.16.

- Reescribir (3.13) y (3.14) como

$$\dot{\hat{\theta}}_1 = (\gamma_{11} v_{pv})(\alpha v_{pv} + \ln I_s - \hat{\theta}_1 v_{pv} - \hat{\theta}_2)$$

(3.15)

$$\dot{\hat{\theta}}_2 = (\gamma_{22})(\alpha v_{pv} + \ln I_s - \hat{\theta}_1 v_{pv} - \hat{\theta}_2)$$

(3.16)

Conociendo todas las ecuaciones necesarias para el modelo a simular, es posible generar la dinámica de  $\hat{\theta}_1$  y  $\hat{\theta}_2$  cuando no se ha alcanzado la isoclina de crecimiento cero. Este método se emplea debido a que se trata de aproximar un sistema no lineal como uno lineal utilizando una aproximación gráfica ([39], [40]) alrededor de un punto de equilibrio dado. El comportamiento del sistema se muestra en la figura 3.2.

**Figura 3.2:** Evolución de parámetros  $\hat{\theta_1}$  y  $\hat{\theta_2}$  en el plano bidimensional antes de alcanzar la trayectoria de la isoclina de crecimiento cero.

**Figura 3.3:** Dinámica de los parámetros  $\hat{\theta_1}$  y  $\hat{\theta_2}$  mostrando su evolución en el tiempo. Tiempo de simulación= 0.030 segundos.

La figura 3.2 muestra que para un tiempo muy pequeño de simulación el estimador no es capaz de alcanzar el equilibrio establecido con el punto rojo en la gráfica, ni el comienzo del *nullcline*. En la figura 3.3 se aprecia con mayor detalle la diferencia que existe con respecto al punto de equilibrio deseado para  $\theta_1$  y  $\theta_2$ . A medida de que se incremente el tiempo de simulación en el modelo, este mostrará cómo se genera el comportamiento de los parámetros en el plano de fases. La tabla 3.2 resume los valores utilizados.

**Tabla 3.2:** Parámetros considerados para la simulación del estimador para un tiempo reducido

| Parámetro                      | Valor             |

|--------------------------------|-------------------|

| $\gamma_{11}$                  | 0.1               |

| $\gamma_{22}$                  | 100               |

| $\hat{	heta_1}(	ext{t=0})$     | 0.55              |

| $\hat{\theta_2}(t=0)$          | -13               |

| Número de puntos               | 15                |

| Tiempo de simulaciones [s]     | 0.03              |

| Tolerancia absoluta y relativa | $5 \cdot 10^{-8}$ |

**Figura 3.4:** Evolución de parámetros  $\hat{\theta_1}$  y  $\hat{\theta_2}$  en el plano bidimensional una vez alcanzado el punto de equilibrio planteado.

**Figura 3.5:** Dinámica de los parámetros  $\hat{\theta_1}$  y  $\hat{\theta_2}$  mostrando su evolución en el tiempo. Tiempo de simulación= 15 segundos.

**Tabla 3.3:** Parámetros considerados para la simulación del estimador para un tiempo extenso

| Parámetro                      | Valor             |

|--------------------------------|-------------------|

| $\gamma_{11}$                  | 0.1               |

| $\gamma_{22}$                  | 100               |

| $\hat{\theta_1}(	ext{t=0})$    | 0.55              |

| $\hat{\theta_2}(	ext{t=0})$    | -13               |

| Número de puntos               | 1000              |

| Tiempo de simulación(s)        | 15                |

| Tolerancia absoluta y relativa | $5 \cdot 10^{-8}$ |

La tabla 3.3 muestra que incrementando el tiempo de simulación y el número de puntos utilizados se puede representar la dinámica de manera clara (ver figuras 3.4 y 3.5), tanto en la fase plana como en la evolución del tiempo una vez que la ecuación (2.17) se mantiene constante.

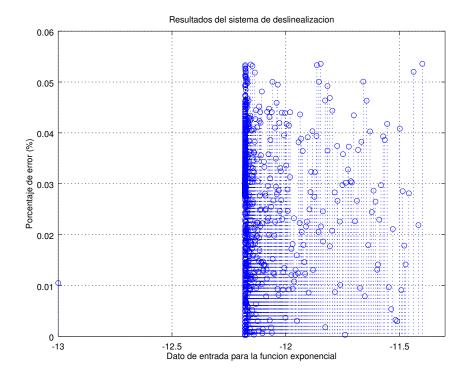

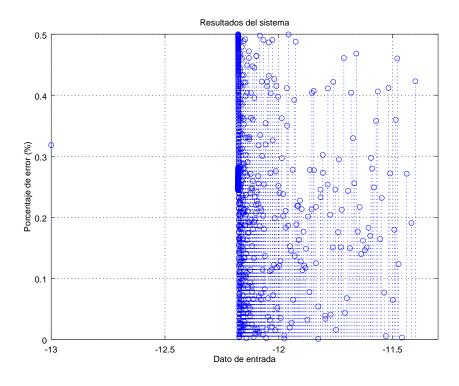

#### 3.3 Resultados del modelo teórico

En las figuras 3.6 y 3.7 se muestra el porcentaje de error para  $\hat{\theta_1}$  y  $\hat{\theta_2}$ , en el que se observa que este supera el 5% para ambos casos cuando los valores iniciales se encuentran distantes de  $\alpha = 0.625$  y ln  $I_s = -12.178708$  respectivamente.

Figura 3.6: Porcentaje de error obtenido para la convergencia de  $\theta_1 = \alpha$ .

Figura 3.7: Porcentaje de error obtenido para la convergencia de  $\theta_2 = \ln(I_s)$ .

El error decrece linealmente a medida que el valor converge hasta alcanzar un valor de 0%, este puede ser aún menor para valores iniciales que se encuentren más cercanos a los deseados. Para efectos de demostrar el comportamiento del modelo se tomaron estos valores arbitrariamente. Es importante aclarar que se debe de realizar un análisis del modelo teórico y una modificación de  $\gamma_{11}$  y  $\gamma_{22}$  con miras a una implementación en un dispositivo programable. Lo anterior se debe, a que estos valores pueden permitir acelerar la convergencia notablemente haciendo que el tiempo de ejecución sea muy bajo.

El tiempo de estimación mostrado en la figura 3.5 es de aproximadamente 5 segundos, lo que se considera aceptable debido a que los parámetros desconocidos sólo cambiarán estrictamente cuando la temperatura varíe en el PV.

## Capítulo 4

# Sistema de conversión coma fija a coma flotante y desnormalización

En este capítulo se presenta la creación de un sistema capaz de convertir datos representados en formato coma fija al estándar IEEE 754. El estimador de parámetros se realizará en coma fija ya que permitirá obtener los cálculos necesarios de una forma rápida y utilizando menos recursos comparado con una implementación en coma flotante.

## 4.1 Diseño del sistema de conversión, desnormalización y control de datos